La tecnología para cortar una sola unidad de una obleas y luego encapsularla ha sido la norma para encapsular circuitos integrados semiconductores durante décadas. Sin embargo, debido a los altos costos de fabricación y al creciente número de componentes de radiofrecuencia en los módulos actuales, los principales fabricantes de semiconductores aún no han adoptado este método. Por lo tanto, la aparición de la encapsulación a nivel de obleas (wlap) ha llevado a un cambio de paradigma en el desarrollo de la encapsulación de bajo costo. Wlap es una tecnología de encapsulamiento a nivel de chip antes de cortar el dispositivo de encapsulamiento de chip.

Utilizando herramientas y procesos estándar, wlp se utiliza como una extensión del proceso de fabricación de obleas. Finalmente, el wlp die fabricado tendrá almohadillas metálicas en la superficie del CHIP y depositará puntos de soldadura en cada almohadilla antes de cortar el chip. Esto, a su vez, hace que el wlap sea compatible con los procesos tradicionales de montaje de PCB y permite realizar pruebas de dispositivos en el propio chip. Por lo tanto, se trata de un proceso relativamente barato y eficiente, especialmente cuando el tamaño del chip aumenta y el chip die se contrae. El tamaño de las obleas ha ido en aumento en las últimas décadas, pasando de 4, 6 y 8 pulgadas de diámetro a 12 pulgadas. Esto ha provocado un aumento de la cantidad de die por chip, lo que ha reducido los costos de fabricación. En términos de rendimiento eléctrico, el wlap es superior a otras tecnologías de encapsulamiento, ya que una vez integrado el dispositivo wlap en un módulo de radiofrecuencia denso, reduce significativamente el acoplamiento parasitario em, ya que la interconexión entre el dispositivo y el PCB es relativamente corta, a diferencia de la interconexión de Unión de cables utilizada en algunos tipos de tecnologías csp.

Tecnología de chip invertido de chip wlap

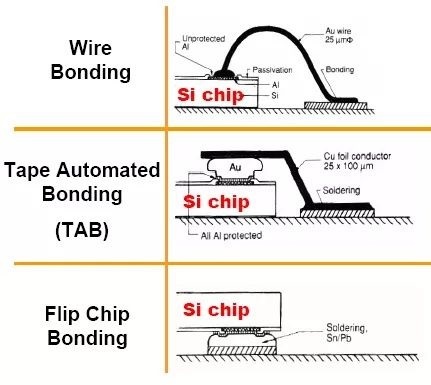

La tecnología de chips invertidos, también conocida como conexión de chips plegables controlables (c4), es una de varias tecnologías de ensamblaje de chips desarrolladas por IBM en la década de 1960. Aunque la tecnología de encapsulamiento basada en la Unión de alambre es más flexible en términos de capacidad de inducción libre para la puesta en marcha de laboratorio después de la construcción de hardware y también proporciona una buena conductividad térmica, el uso de protuberancias de soldadura en la tecnología de encapsulamiento de chip invertido hace que la conexión eléctrica entre el sustrato de Encapsulamiento y el chip proporcione una reducción relativa de tamaño y retraso. Y un mejor aislamiento en sus pines de entrada y salida. La figura 1 muestra la estructura básica del chip die en el sustrato, con una bola de soldadura en la parte superior de la columna de cobre que crece en la superficie del chip. Las juntas de soldadura suelen encapsularse con un compuesto de molde de relleno para proporcionar soporte mecánico a las juntas de soldadura.

Encapsulamiento a nivel de chip wlap

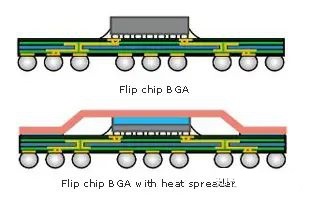

El encapsulamiento a nivel de chip (csp) es uno de los métodos de encapsulamiento más utilizados en la industria de la microelectrónica y semiconductores. Aunque los fabricantes de microchips ya pueden usar varios tipos de tecnología csp, siguen surgiendo nuevos tipos de CSP para satisfacer la demanda de productos que admitan nuevas funciones y nuevas aplicaciones para productos específicos. Estos requisitos de encapsulamiento pueden variar según la fiabilidad, el costo, las funciones adicionales y el tamaño general requeridos. Como su nombre indica, el tamaño de encapsulamiento del CSP es aproximadamente el mismo que el tamaño del chip die, que es una de sus principales ventajas. A través del proceso de fabricación de wlap, el CSP está evolucionando constantemente para lograr la relación de tamaño del núcleo encapsulado lo más pequeña posible. Como se muestra en la figura 2, el CSP de matriz de rejilla esférica (bga) en el paquete permite múltiples interconexiones, al tiempo que simplifica el cableado de pcb, mejora el rendimiento de montaje de PCB y reduce los costos de fabricación.

Otras tecnologías de encapsulamiento

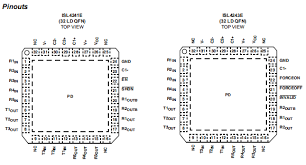

Hay varias otras formas de encapsulamiento IC integrado que permiten una integración perfecta en el encapsulamiento de módulos personalizados por la Aplicación. El encapsulamiento de cuatro planos (qfps) es una de las primeras tecnologías de encapsulamiento IC de montaje de superficie, en las que la estructura del encapsulamiento está compuesta por cuatro lados con cables de interconexión extendidos, como se muestra en la figura 3 (a). El cable elevado está conectado al marco de encapsulamiento para formar un capacitor de tipo Metal - aislador - metal (mim) entre el cable y el metal die del chip, que se puede utilizar como elemento de emparejamiento. La tecnología es adecuada para IC de tamaño milimétrico, donde el número de pines periféricos en el encapsulamiento puede alcanzar más de 100. Según el material utilizado, este tipo de encapsulamiento tiene varios derivados, como encapsulamiento plano cuadrado de cerámica, encapsulamiento plano cuadrado delgado, encapsulamiento plano cuadrado de plástico (encapsulamiento plano cuadrado de plástico) y encapsulamiento plano cuadrado metálico (mqfps). Qfn, quad Flat no lead, como se muestra en la imagen. 3 (b) es una de varias técnicas de encapsulamiento de montaje de superficie, formada por un marco plano de alambre de cobre y un encapsulamiento de plástico utilizado como almohadilla de transferencia de calor para radiadores. Las uniones de alambre también se pueden utilizar para interconexiones, ya que los cables de unión no son solo conductores, sino también inductores, por lo general afectan el rendimiento de los dispositivos bajo esta tecnología de encapsulamiento, a menos que se consideren parte del diseño general. Aunque el qfn es una interconexión compuesta por cuatro lados, los cables biplanos sin plomo (dfn) también han aparecido y formado ambos lados de los cables planos de interconexión.