Interconnect technology of encapsulation chips with high performance and reliability-IC Packaging

The market development direction of electronic components(For Assemblea del bordo dei circuiti stampati - PCBA)

For the mature technology of LSI with higher integration and speed, è necessario sviluppare una tecnologia di isolamento utilizzando materiali a basso K a seconda dei casi. But in order to satisfy the high performance of these units, l'isolamento diventa sempre più sottile a causa della struttura porosa e multistrato. Di conseguenza, LSI becomes brittle. On the other hand, per soddisfare i requisiti ad alta velocità, the current of LSI is constantly increased. Oltre alla dimensione del chip da grande a piccolo, thermal density and power consumption are also increasing. Therefore, for the semiconduttore packaging substrateï¼IC Substrate Packagingï¼ in the future, it is required to solve these problems, vale a dire, the fragility of the interlayer media, calore elevato, high speed and low cost. The future presupposition of semiconduttore i processi saranno nella generazione 20nm e inferiore, which will be much weaker.

Tecnologia di imballaggio richiesta per la generazione 20nm

La specifica richiesta per la prossima generazione di 20nm è:

Basso stress per fragile strato K basso

High thermal radiation ¥5W for high-performance LSI

Alta velocità 10GHz per alte funzionalità

Imballaggio a semiconduttore development direction

Al fine di accogliere la crescita funzionale e la riduzione dei costi delle strutture elettriche, comprese le strutture mobili, le regole preimpostate per i wafer si stanno spostando verso regole preimpostate più ampie e più fini. A tal fine e ridurre i costi, la tecnologia di confezionamento dei semiconduttori si sta rapidamente spostando dalla tecnologia di incollaggio più standard del filo d'oro al filo di rame, che riduce la quantità di oro utilizzato. Inoltre, L'uso della tecnologia di incollaggio flip-chip ha soddisfatto notevolmente l'integrazione e le prestazioni superiori di LSI. Nel 2010 Il flip-chip bonding rappresentava il 15% e il piombo bonding 85% del mondo semiconduttore packaging technology. Entro il 2015, la quota di flip-chip bonding dovrebbe raggiungere il 25 per cento, e la quota di lead bonding dovrebbe raggiungere il 75 per cento. Soprattutto per l'elevata integrazione LSI ad alte prestazioni e la velocità di irraggiamento termico, La tecnologia di incollaggio flip-chip è considerato appropriato e che richiede un elevato segnale appropriato.

Common sense flip-chip technology

Idoneità per basse K

Commonly used flip chip technology:

Welding adjacent flank, the main structure is C4 (controllable subsidence chip co-sign)

For pressure bonding of Au urto and ACF type

Ultrasonic bonding for AU-AU type signature

Pressure and ultrasonic bonding have high pressure and mechanical oscillation applied to LSI, quindi questi metodi non possono essere utilizzati per LSI basso K. Because of this, nel metodo di cui sopra, C4 can be used as appropriate, e a causa del confronto dei tre metodi, the bond is consistent with the fact that C4 does the least damage to the chip.

La tecnologia C4 è stata creata nei primi anni '40 per computer di uso generale ed è stata utilizzata da allora. With the increasing number of low K wafers, C4 è stato utilizzato per la bassa K sostituendo le strutture UBM, materials and improvements.

Recently developed Cu column urtos (roughly similar to advances in C4) are suitable for in-line or overlapping pads, not for low K wafers. It has been reported that Cu column structure encapsulation may damage the low k layer due to the high elastic modulus of Cu (130GPa). The mismatch of thermal expansion coefficient (CTE) is the acceleration factor.

Inoltre, the C4 technology originally used molten metal junction after the flux and the high elastic modulus of the flux (50GPa) deemed appropriate, quindi la quantità di stress è stata aggiunta all'LSI a causa della differenza nell'espansione del riscaldamento durante l'incollaggio e l'installazione della piastra madre. Therefore, La tecnologia C4 non può essere utilizzata per il futuro LSI, which is much weaker.

Radiazioni termiche

Fino ad ora, substrati organici sono stati utilizzati per l'imballaggio flip-chip. La conducibilità termica dei substrati organici è piccola, 0,5 W / MK, ed è difficile da applicare a LSI con alto consumo energetico. Se si aggiunge un sistema di raffreddamento o raffreddamento per migliorare la radiazione termica, il costo dell'incapsulamento, la dimensione e l'altezza del piano o della superficie aumenteranno.

In fact, perché la radiazione termica è bassa, a bit of LSI limits its potential so as not to generate a large amount of heat. In addition, because the heat radiation is not good, la temperatura di giunzione aumenta, the leakage current increases, che aumenta ulteriormente il consumo energetico, and the increase in power consumption makes the temperature rise. È un circolo vizioso pericoloso. Therefore, Il miglioramento della radiazione termica è un problema stretto.

High speed of the signal

La perdita media di danno dello strato centrale del substrato organico è alta (0,02) e l'impedenza del foro passante (T/H) dello strato centrale è alta. Di conseguenza, la perdita di danno all'inserzione nella gamma ad alta frequenza è elevata. Tuttavia, utilizzare substrati senza anima dello stesso materiale dei substrati organici tradizionali non è la soluzione fondamentale. Inoltre, i materiali dello strato composito possono essere una varietà di, in modo che l'utente scelga il materiale migliore è più difficile, tutti i requisiti preimpostati per pensare al problema delle prestazioni ad alta velocità.

Poiché il substrato è sottile, una serie di strutture devono essere cambiate. Questo diventa un ostacolo alla produzione. A causa di questo problema, il trasferimento su un substrato senza anima è ad alto rischio e adatto solo per propuntoti localizzati.

La tecnologia tradizionale è difficile da soddisfare la futura generazione 20nm. Therefore, è necessario sviluppare nuovi imballaggi a semiconduttore with new central technology.

Monsterpac-typec e elementi essenziali di processo

Monsterpac-typec è stato sviluppato per soddisfare il processo 20nm, difficile da adattare alla tradizionale tecnologia di imballaggio. This is the traditional packaging process and structure is absolutely different from the packaging.

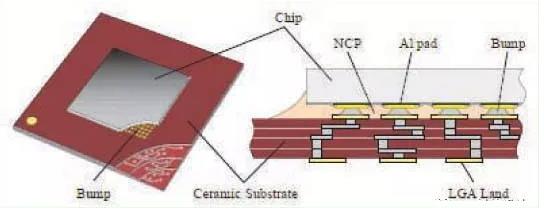

Encapsulation structure

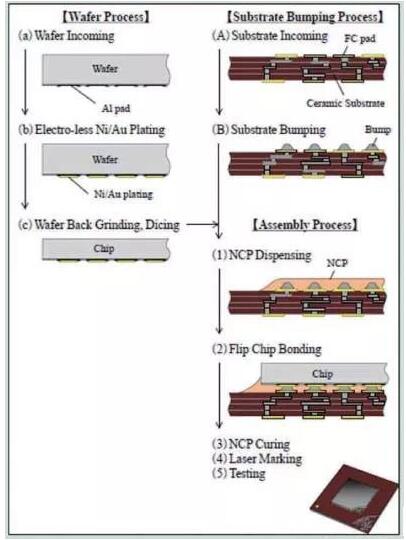

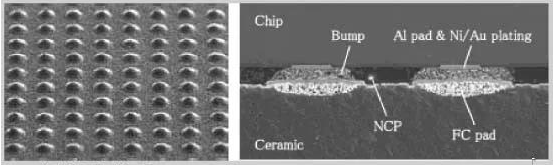

La nostra struttura d'imballaggio, il substrato è ceramico, chip semiconduttore con flip bump, chip e substrato supplemento NCP (pasta non conduttiva). Non è stampato con gas epossidico o resina naturale. Quindi il retro del chip è esposto. La deformazione ad alta temperatura della saldatura di riflusso è piccola, meno di 30-50μm, quindi il pacchetto è LGA (pacchetto matrice di contatto) senza palle di saldatura, non BGA (pacchetto matrice di griglia). Una pasta conduttiva contenente argento viene utilizzata per gli urti, che vengono stampati sul substrato in modo che i moduli non siano più fabbricati sui pad. Nichel e oro non placcati solo sui pad Al del chip senza il processo di tamponamento del wafer (Figura 1-3).

FIC-1 Packaging Structure

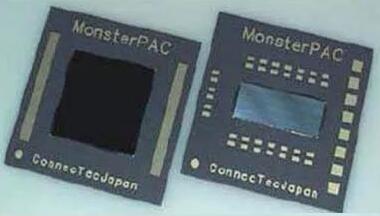

FIC-2 Packaging Image

Processo FIC-3

Ampiamente simile a quanto sopra, our package consists of only 4 materials (chip, bump, ceramic and NCP). Questa struttura semplice rende per un piccolo, thin and lightweight package.

There are two main types of ceramic substrate materials available: HTCC (high temperature co-fired ceramic) and LTCC (low temperature co-fired ceramic). The special properties of ceramics (such as electrical properties, conducibilità della temperatura, CTE and warping) and flip chip bonding enable our packages to satisfy the best solution for a wide range of requirements from electrical products to semiconduttore chips.

Monsterpac-typec structure is unique

I luoghi unici sono descritti come segue:

Nessun legame di danno

Elevata radiazione termica

Low insertion loss

Alta affidabilità

Combinando ciascuno di questi principali vantaggi, MonsterPac-TypeC riesce a fornire le migliori prestazioni possibili per la generazione LSI 20nm.

No damage bond

La tecnologia di base del nostro pacchetto è la tecnologia di incollaggio flip-chip senza danni, che raggiunge con successo l'incollaggio senza danni e altamente affidabile per chip semiconduttori fabbricati con lavorazioni di precisione all'avanguardia.

Chips a semiconduttore without damage refers to:

Low pressure bonding

We can achieve a bonding pressure of 0.12g/ bump, which is 1/20 dei C4 normali 2.4g/ bump. By reducing the bonding load to this limit, damage of the bonding induced interlaminar medium can be avoided.

Low retraction stress during convex curing

The shrinkage stress during the solidification of the punto convesso is less than 10MPA/ convex point, which is very small. High yield and reliable flip-chip bonding is successfully achieved by upper limit reduction of temperature, load and retracting stress applied to the middle layer of the brittle medium (such as low K and Al pads and lines, etc.) to avoid line breakage and cracks.

Da questi vantaggi, it can be seen that it is the only package with the structure to avoid weak low K layer damage.

High thermal radiation

Rendendoci conto che le calorie del chip semiconduttore sono irradiate dal substrato incapsulato, invece del substrato organico comune (conducibilità termica di 0.5W/mk), abbiamo scelto il substrato ceramico, perché la sua conducibilità termica è più del substrato organico, Quando la dimensione del pacchetto è 2121mm e si utilizza il substrato ceramico, la dissipazione di potenza raggiunge 6W, che è 1,7 volte superiore a quella del substrato organico con dissipazione di potenza 3,6W.

Un basso inserimento ti farà male

Electronic facilities require high level performance in the high frequency range. The insertion loss of ceramic substrate is 0.42dB (@20GHz, L=5mm), while that of organic substrate is 0.62dB. La frequenza consentita dal substrato ceramico è superiore a 10GHz, while that of organic substrate is 3GHz.

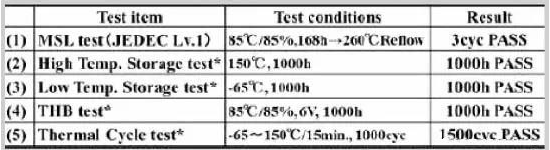

High reliability and high tolerance to moisture resistance

Normal reflow resistance (MSL: Wetness Level) is Level 3 (@30DEG /60 100% RH192Hr). Monsterpac-typec ognuno ne ha uno semiconduttore chip that is undamaged and the bumps are made of non-fused material. At high temperature reflow, the bump is not fused, in modo da non ripetere ri-fusione e ri-indurimento, and the ceramic substrate does not borrow moisture. Di conseguenza, the MonsterPac-TypeC is MSL Level 1 (@85DEG /85 100% RH192Hr), it does not have to be pre-baked to remove moisture and moisture proof packaging, e la vita vegetale del MonsterPac-TypeC è illimitata.

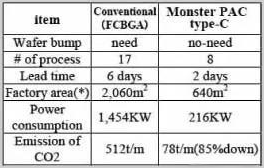

High plant rate

Invece of welding bumps, Abbiamo sviluppato una struttura di tamponamento a gas epossidico per facilitare la produzione. As a result, un gran numero di impianti di processo di tamponamento del wafer sono necessari, the cost of a large number of can + wisp welding adjacent to reflow is also necessary. Quindi, compared to a conventional C4 process plant of the same size, the size of the plane or surface of the plant can be reduced by 69 percent, and the energy consumption of the plant can be reduced by 85 percent. Può raggiungere con successo il risparmio energetico e l'impianto a basso carico di fondo.

Capacity

Luogo unico del processo Monsterpac-typec

Ceramic technology bump

Monsterpac-typec ritiene opportuno utilizzare una pasta conduttiva contenente argento come materiale antiurto. Per formare protuberanze sul supporto ceramico utilizzando la consueta tecnica di stampa di parti SMD con stampa di saldatura, se ritenuto appropriato. Non è necessario pre-smaltire e pulire la superficie del substrato ceramico prima di sollevare lo smaltimento del punto e elettroplaccare la dopo la superficie la formazione del punto di sollevamento. La FCBGA organica convenzionale richiede dossi lunghi, come il flusso, dossi Au e Cu, sulle pastiglie Al dei wafer semiconduttore. Tuttavia, i bump a base di ceramica non richiedono questo processo di bump lungo del wafer. Invece, producono Ni e Au non elettroplaccati su chip semiconduttori. I dossi basati sulla tecnologia ceramica hanno realizzato con successo il processo di smaltimento semplice ea basso costo.

Inoltre, a differenza degli urti duri (durezza ¤10Hv) utilizzati nelle tecniche di buon senso come flux, Au e Cu bump, i colpi morbidi (¤1Hv) sono stati sviluppati per mantenere il modello sotto bassa durezza.

For silver-containing soft convex conductive pastes, we have developed concerned fixation points that are experienced in low stress, bassa resistenza al controsegno e stampa del passo dei dettagli. The labor capacity we have so far formed bumps is face array pads: pitch 150μm; Peripheral pads: Pitch 75μm. Tuttavia, this pad pitch is considered by the actual preset rule, Quindi il passo della matrice superficiale di 60μm è applicabile solo per urti di apertura.

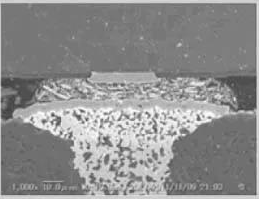

No damage bond

Con la tecnologia soft flip chip bonding, l'NCP utilizzato per distribuire gli urti morbidi formati dalla tecnologia ceramica bump e quindi il chip semiconduttore è legato con il flip chip. Durante il processo di incollaggio, la pasta conduttiva degli urti e l'NCP sono solidificati allo stesso tempo. Di conseguenza, sia la co-firma che l'affidabilità sono raggiunti con successo.

The temperature of the FCB facility is below 200, which is more than 40 lower than the normal bonding technology. La pressione di incollaggio è inferiore a 0.12g/ dot, which is 1/20 della normale tecnologia di incollaggio. With these low temperature and low pressure hot pressing bonds, semiconduttore I trucioli non sono sottoposti a sollecitazioni e forze esterne durante l'incollaggio e la polimerizzazione post-incollaggio. Using the newly developed conductive paste and NCP, la tempistica dei tasti ad alta velocità inferiore a 1.0 seconds was successfully achieved. Il PNC comprende supplementi, which are commonly found on both sides of the chip pad and the bump. Tuttavia, it is common to flip the chip keys at low pressure. Il supplemento è sepolto tra i dossi, so it does not affect the signature between the chip pad and the bumps. Questo è uno dei vantaggi di urti morbidi. After the distribution of NCP before the flip chip welding, NCP è facilmente integrato tra il punto convesso e lo spazio stretto, and with the low load key, il puntamento tra il chip e il substrato non avverrà. Therefore, Questa tecnica di incollaggio è adatta per l'uso con piazzole di tampone strette.

Il problema con le comuni tecniche di incollaggio è che nel caso di incollaggio flip-chip con protuberanze di saldatura, durante la fusione del flusso per l'indurimento vengono applicate sollecitazioni di retrazione molto elevate (circa 200-500 mpa/bump) alle protuberanze e ai cuscinetti di Al del chip semiconduttore . Tuttavia, la tecnica di incollaggio a bassa sollecitazione ha successo perché il basso modulo elastico dei materiali convessi non fusi richiede una sollecitazione di rimbalzo molto piccola (inferiore a 10 MPa/convesso).

A causa del suddetto processo di sviluppo di queste tecnologie di base, il successore dell'incollaggio integro del chip flip. FICO. 4 è una vista cutaway del keypoint e del controsegno del flip chip.

FIG-4 Visual and Section Photo

Affidabilità degli imballaggi

TC ha testato il profilo del punto convesso posteriore, but did not test and measure the cracks and descaling that would be induced by fracture coupling.

APIC (Application device IC)

Oggi l'elaborazione APIC si sta muovendo verso l'uso di materiali low-K per la lavorazione di precisione, che richiede alta tolleranza alle temperature e alta velocità. Il Monsterpac-TypeC soddisfa questi requisiti con i vantaggi elencati di seguito.

No damage bonding

Elevata radiazione termica

Quando ad alta velocità

Alcuni clienti APIC stanno valutando il MonsterTipo PAC per la produzione in scala

Tipo PAC

As a result of the actual evaluation between the organic FCBGA and monsterpac-TypeC under the same conditions (same skirt, same chip and same pad pitch), the monsterpac-TypeC temperature Tj is 10 lower than that of the organic package. Dopo un confronto molto accurato di Tj, the difference would be about 20.

The RF Board(Radio Frequency Board):

Attualmente, per la comunicazione LSI ad alta velocità, l'incapsulamento della piastra sta migliorando costantemente. Queste sezioni richiedono proprietà speciali elencate di seguito:

Suitable for high speed and high frequency

Low size small

For high speed and high frequency applications, come sopra, if appropriate, L'uso di substrato ceramico può migliorare la perdita di inserzione, can be used for 10GHz.

Inoltre, il multi-chip e l'alto numero di parti SMD possono essere utilizzati in piccoli pacchetti a causa della disponibilità di piccoli legami flip-chip a passo di dettaglio.

Collaborato con un cliente di piastra RF, developed a sample, la sua prestazione è stata approvata dal cliente, is preparing for scale production

RF Module

For these plate enclosures, l'umidità del substrato è molto stretta. L'MSL di monsterpac-TypeC è Livello 1, so there is no wetting degree choking.

Si vede quel mostroTipo PAC is the most suitable for plate packaging, che richiede saldatura a riflusso multipla per imballaggi organici convenzionali SMD e flip-chip.

Judge

Per la prossima generazione di processi 20nm, i pacchetti sono necessari per ospitare radiazioni termiche più elevate e velocità più elevate. Tuttavia, la tecnologia di imballaggio del buon senso è difficile soddisfare questi requisiti. Pertanto, è necessario sviluppare una nuova tecnologia di imballaggio adatta alla generazione di processo 20nm.

Il nostro Monsterpac-TypeC è adatto per la prossima generazione di processo 20nm e massimizza le prestazioni LSI. Its high performance is like an amazing weird product. MonsterPAC, which we developed, ha reso C4 obsoleto e diventato la principale tecnologia che contribuisce alla prossima generazione di semiconduttores in the future.

Per la prossima generazione di sviluppo tecnologico

Ricerca e sviluppo di nuovi substrati ceramici

The development of ceramic substrate technology has been more than bright. Fino ad ora, precise and detailed plotting with high density has lagged far behind organic IC Substrates.

Per risolvere questo problema e fare progressi, we set out to develop a precise ceramic substrate with high density without affecting the cost. Il nostro obiettivo è 20μm campo di linea, to achieve as appropriate and the use of precision and detailed graphics more flexible default, Anche il passo attraverso il foro deve essere più preciso e dettagliato, the goal is 50μm.

Finora il substrato ceramico è stato realizzato utilizzando punch e mascherina come ritenuto appropriato. These existing techniques are very limited to precise and detailed drawing. Stiamo pensando di sostituirli con processi di stampa laser e diretta. Implementing this technology will provide much better performance than organic substrates. Fino ad ora, ceramic substrates have been commonly used in high-end products, tuttavia, this new substrate will be aimed at consumer products. E il substrato ha davvero bisogno di prodotti di consumo ad alte prestazioni per crescere se stesso.

La combinazione di questo substrato e della tecnologia MonsterPAC fornirà al mondo le migliori prestazioni e un'elevata affidabilità Printed Circuits Board(PCB).