のデザインで PCBボード, 周波数が急速に増加して, 低周波数の設計とは異なる多くの干渉 PCBボード が現れる. Moreover, 周波数が増えるにつれて, 小型化と低コスト化の矛盾 PCBボード ますます顕著になった. これらの擾乱はますます複雑になっている. 実際研究で, 我々は合計する, つの主な干渉があります, 電源ノイズを含むこと, 伝送線干渉, カップリング, and electromagnetic interference (EMI). 種々の干渉問題の解析 高周波PCB, 仕事の練習と組み合わされる, 有効解を提案する.

電源ノイズ

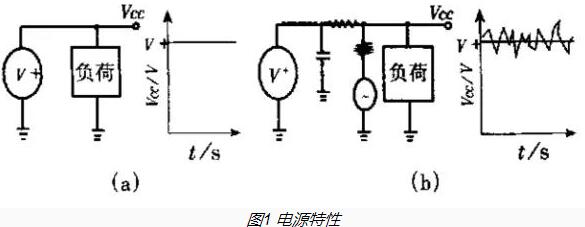

に 高周波回路, 電源のノイズは、高周波信号に特に明らかな影響を及ぼす. したがって, 第1の要件は、電源が低雑音であることである. ヒア, きれいな地面はクリーンな電源と同じくらい重要です. なぜ? 電力特性は、図1のように示される. 1. 明らかに, 電源はあるインピーダンスを有する, そして、インピーダンスは電源全体に分配される, 従って、電源にはノイズが重畳される. 次に、電源のインピーダンスをできるだけ小さくする必要があります, したがって、専用のパワー層および接地層を有することが最善である. イン 高周波回路 デザイン, 電源は、層の形で設計されている, そして、ほとんどの場合、それはバスの形でデザインよりはるかによいです, ループが常に最小のインピーダンスで経路に続くことができるように. 加えて, パワーボードはPCB上の全ての生成信号及び受信信号に対して信号ループを提供しなければならない, 信号ループを最小化できるようにする, それによってノイズを減らす, 低周波回路設計者にしばしば見落とされる.

Figure 1 Power supply characteristics

There are several ways to eliminate power supply noise in PCB design.

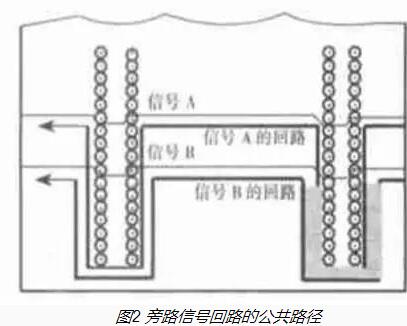

ボード上のスルーホールに注意してください:スルーホールは、通過するスルーホールのためのスペースを残して開口部をエッチングするためにパワー層を必要とします。パワー層の開口が大きすぎると、信号ループに必然的に影響を与え、信号がバイパスされ、ループ面積が増加し、ノイズが増加する。同時に、いくつかの信号線が開口の近くに集中し、このループを共有する場合、共通インピーダンスはクロストークを引き起こす。写真2に示すように。

Figure 2 Common path of bypass signal circuit

2. ワイヤーを接続するには十分な接地線が必要です, そして、信号とループのループ面積は、できるだけ小さくなければならない, 即ち, 信号とループは並列でなければならない.

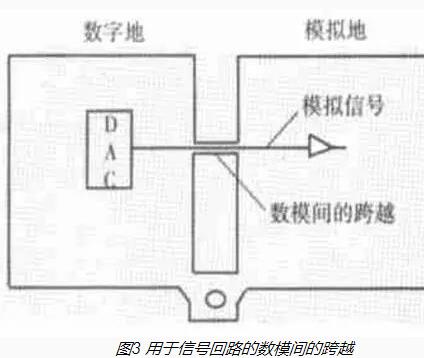

アナログおよびデジタル電源の電源は分離されるべきである:高周波デバイスは一般にデジタルノイズに非常に敏感であるので、2つは分離されて、電源の入口で一緒に接続されなければならない。信号がアナログとデジタルの部分を横断する必要がある場合は、ループ領域を減らすために交差点にループを置くことができます。信号ループで使用されるデジタルとアナログの間のクロスオーバを図3に示す。

図3信号ループのためのデジタルとアナログの間のクロスオーバ

4. 別の層の間で別々の電源をオーバーラップすることを避ける.

5 .高感度成分:例えば、PLLを分離してください。

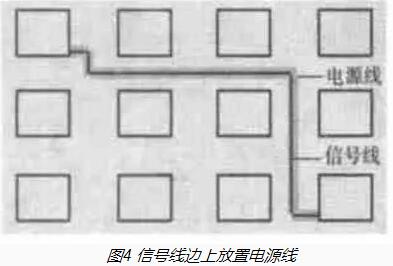

(6)電力線を配置する:図4に示すように、信号線を減少させるために、電力線を信号線の端部に配置することによってノイズを低減する。

図4信号ラインのエッジに電源ラインを配置する

2、送電線

PCBには2つの可能な伝送線しかありません:ストリップラインとマイクロ波ライン。伝送線路の最大の問題は反射である。反射は多くの問題を引き起こします。例えば、負荷信号は、元の信号とエコー信号の重ね合わせであり、信号解析の難しさを増加させる反射はリターン損失(リターン損失)を引き起こします、そして、信号に対するその影響は加法雑音干渉の影響と同じくらい深刻です:

信号源に反射された信号は、システムノイズを増加させ、受信機が信号からノイズを識別することをより困難にする

あらゆる反射信号は、基本的に信号品質を劣化させ、入力信号の形状を変更する。原理的には、解決策は主にインピーダンス整合(例えば、相互接続インピーダンスはシステムのインピーダンスに非常によく適合するべきである)であるが、時々インピーダンス計算がより面倒である場合、いくつかの伝送線路インピーダンス計算ソフトウェアを参照することができる。

PCB設計における伝送線干渉を除去する方法は以下の通りである。

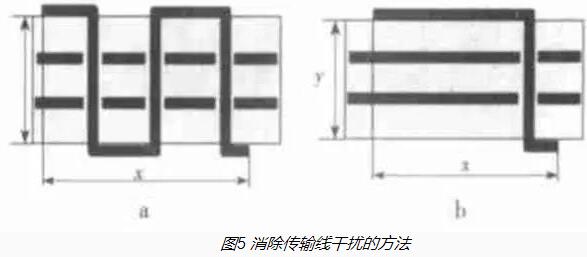

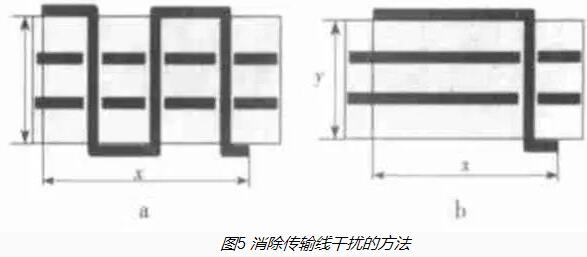

(a)伝送線路のインピーダンスの不連続性を回避する。インピーダンスが不連続になる点は、直線状のコーナーやビアなどの急激な変化が避けられない点である。方法は:トレースの直線の角を避けるために、45度の角度角度や円弧のために行くしようとすると、大きな曲が良いです図5に示すように、各ビアはインピーダンス不連続点であるので、できるだけ少ないバイアとして使用する外側の層信号は、内側の層を通過するのを回避する。

Figure 5 Methods to eliminate transmission line interference

(B) Do not use stubs. どんなスタブも雑音の源だから. スタブラインが短いならば, これは、伝送ラインの終端で終了することができますスタブラインが長いならば, メイン伝送ラインはソースとして使用されます, これは大きな反射を引き起こし、問題を複雑にする, だから、それを使用することをお勧めしません.

カップリング

共通インピーダンス結合:一般的な結合チャネル、すなわち、干渉源と干渉されたデバイスは、図6に示すように、特定の導体(ループ電力、バス、共通接地など)を共有することが多い。

Figure 6 Common impedance coupling

On this channel, ICのドロップは、直列電流ループ内のコモンモード電圧を引き起こす, 受信機に影響する.

フィールド共通モード結合は、放射源が干渉回路及び共通基準面によって形成されたループ上のコモンモード電圧を引き起こす原因となる。磁界が支配的であれば、直列接地ループで発生するコモンモード電圧の値は、Vcm=−(Low−Cherno−B/Ea−CHERUNT−T)*領域(Low−AnchB−B=磁気誘導強度の変化)である。電磁界であれば、その電界値、誘起電圧:VCM=(L*H*F*E)/48、式をL(m)=150 MHz以下とすることが知られているが、この限界を超えて、最大誘導電圧の計算は、VCM=2*H*Eとなる。

3. 差動モードフィールド結合:直接放射線を誘導し、ワイヤペアまたはリード線によって受信される 回路基板 とそのループ. それが2本のワイヤーにできるだけ近いならば. この結合は大幅に削減される, それで、2つのワイヤーは、干渉を減らすために一緒にねじられることができます.

ライン結合(クロストーク)は、任意のラインを並列回路間の望ましくない結合に等しくすることができ、それはシステムの性能を重大に損なう。そのタイプは、容量性クロストークと誘導クロストークに分けることができる。前者は、ライン間の寄生容量がノイズ注入ラインに電流注入を介して結合されたノイズ源のノイズを作るためである後者は望ましくない寄生トランスの一次及び二次ステージ間の信号の結合と考えられる。誘導クロストークの大きさは、2つのループの近接性とループ面積の大きさと、負荷のインピーダンスに依存する。

電源ラインの結合:ACまたはDC電力線が電磁干渉を受けると、電力線は他の装置にこれらの干渉を送信することを意味する。

PCB設計におけるクロストークを除去する方法はいくつかあります。

(1)負荷インピーダンスの増加に伴い両クロストークが増加するため、クロストークによる干渉に敏感な信号線を適切に終端する必要がある。

2 .効果的に容量性漏話を減らすためにできるだけ信号線間の距離を増やす。接地層の管理、配線間の間隔(例えば、孤立した状態とグランドを有する信号線の間において、特に活性化された信号線および接地線)をリードし、リードインダクタンスを低減する。

隣接する信号線間に接地線を挿入することにより、容量性クロストークも効果的に低減することができる。このグランド線は1/4波長毎にグランドに接続する必要がある。

誘導性クロストークに関しては、ループ面積をできるだけ小さくし、許容すると、このループを除去する必要がある。

5 .シグナル共有ループを避けてください。

6 .信号の整合性にフォーカス:設計者は、信号の整合性を解決するために溶接プロセス中に終了を実装しなければならない。この方法を採用する設計者は、良好な信号完全性性能を得るために、遮蔽銅箔のマイクロストリップ長に焦点を当てることができる。通信構造に密なコネクタを使用するシステムでは、設計者は、終了のためにPCBを使用することができる。

電磁干渉

速度が増加するにつれて、EMIはますます深刻になり、多くの面(相互接続における電磁干渉など)に現れてしまう。高速デバイスは特にこれに敏感です。したがって、それらは低速の偽信号を受信する。一方、低速のデバイスはこのような偽信号を無視する。

PCB設計における電磁干渉を除去する方法はいくつかある。

ループを減らす:各ループはアンテナと等価であるので、ループの数、ループの面積およびループのアンテナ効果を最小化する必要がある。信号が任意の2点で1つのループ経路を持つことを保証し、人工ループを回避し、電力層を使用しようとする。

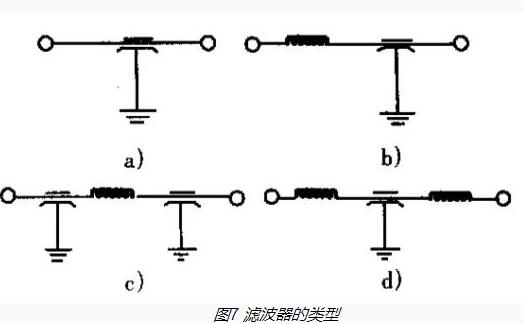

フィルタリング:フィルタリングを使用して、電力線および信号線上のEMIを低減することができる。デカップリングコンデンサ,EMIフィルタおよび磁気部品の3つの方法がある。EMIフィルタを図7に示す。

Figure 7 Types of filters

3. 遮蔽. スペース問題と多くの記事ブロッキングについて議論して, 詳細は紹介しません.

4 .高周波デバイスの高速化を図る。

5. の誘電率の増加 PCBボード 基板に近い伝送線路などの高周波部品を外側に放射させるのを防ぐことができるの厚さを増やす PCBボード そして、マイクロストリップラインの厚みを最小にすることによって、電磁ワイヤが溢れ出るのを防ぐことができる, また、放射線を防ぐこともできます .

議論のこの時点で, 我々はそれを結論付けることができます 高周波PCB設計, 以下の原則に従うべきです。

1電源・グランドの統一性と安定性

慎重な配線と適切な終了は、反射を除去することができます。

慎重な配線と適切な終端は、容量性および誘導性クロストークを低減することができる。

EMC要件を満たすためには、ノイズを抑制する必要がある。