電子技術の急速な発展と様々な分野における無線通信技術の広い応用, 高周波, ハイスピード, そして、高密度は徐々に現代の電子製品の重要な開発傾向の1つになりました.高周波PCB回路 マイクロホールへの信号伝達力PCBの埋め込み/ブラインドホール, 微細導体, ミディアムレイヤー, 高周波, 高密度多層PCB設計技術は重要な研究分野になっている. ハードウェア設計の長年の経験に基づきます, 著者は、いくつかのデザインのスキルと問題をあなたの参照用の高周波回路の注意を必要と要約します.

25 .コストを過大にすることなくEMC要件をできるだけ達成する方法

EMCのコスト増加 PCBボード 通常、遮蔽効果を高めるための層数の増加とフェライトビーズの増加による, チョーク, 及び他の高周波高調波抑制装置. 加えて, 全体のシステムがEMC要件を通過させるために、シールド構造を他の機構に結合するのが通常必要である. 以下は、いくつかのデザインのヒントです PCBボード 回路によって生じる電磁放射線効果を減らすために.

より遅い信号速度を有するデバイスは、シグナルによって、生じる高周波コンポーネントを減らすためにできるだけ選択される。

高周波デバイスの位置に注意してください。あまりにも近くの外部コネクタに配置しないでください。

高周波反射と放射を減少させるために高速信号,ケーブル層およびそのリターン電流経路のインピーダンス整合に注目した。

十分な適切なデカップリングコンデンサを各デバイスのパワーピンに配置して、パワー層および形成のノイズを緩和する。コンデンサの周波数応答と温度特性が設計要件を満たすかどうかに注意を払う。

26. 時 PCBボード 複数の番号/モジュール関数ブロック, 慣習は数を分けることだ/モジュール, なぜ?

デジタル/モードグランドの分離の理由は、高電位と低電位との間のスイッチング時にデジタル回路が電源及びグラウンドにノイズを発生させることである。ノイズの大きさは信号の速度と電流の大きさによって決まる。接地領域が分割されず、デジタルエリア回路によって生成されるノイズが大きい場合、アナログ領域回路が非常に接近している間に、デジタル信号およびアナログ信号が交差しない場合であっても、アナログ信号は依然としてグラウンドノイズによって妨害される。すなわち、アナログ回路領域が大きなノイズを発生するデジタル回路領域から遠く離れている場合にのみ、デジタルおよびアナログの非分割モードを使用することができる。

27 .別の方法は、ナンバー/モジュール分離レイアウトとナンバー/モジュール信号線が交差しないことを確実とすることになっています。なぜ?

アナログ信号がワイヤを横断することができないという要求は、より速いデジタル信号の戻り電流経路が、ケーブルの底部付近の接地に沿ってデジタル信号のソースに逆流しようとすることである。アナログ信号がワイヤを横切ると、リターン電流によって発生したノイズがアナログ回路領域に現れる。

高速PCB設計の回路図設計におけるインピーダンス整合問題の考察

インピーダンス整合は高速pcb回路設計の重要な要素の一つである。インピーダンス値はルーティングモードに関連する。例えば、表面層(マイクロストリップ)または内部層(ストリップライン/二重ストリップライン)、基準層(パワー層または層)、ケーブル幅、およびPCB材料の間の距離は、すべて、ルーティングの特性インピーダンス値に影響する。すなわち、配線後のインピーダンス値を求める。一般的なシミュレーションソフトウェアは、インピーダンス不連続配線の状況を考慮するために使用される数学的アルゴリズムのラインモデルまたは制限のためである。このとき、回路図では、インピーダンス不連続配線の効果を緩和するために直列抵抗のようないくつかのターミネータのみを予約することができる。問題や配線に対する真の基本的な解決策は、インピーダンス不連続な発生を避けることである。

29 .私はより正確なIBISモデルベースを提供できますか?

ibisモデルの精度はシミュレーション結果に直接影響する。IBISは実際のチップのI / Oバッファの等価回路の電気的特性データと考えられ、SPICEモデルによって変換することができる(または測定されるが、より制限がある)。しかしながら、SPICEデータはチップ製造に関連しているので、異なるチップ製造者によって同じデバイスが提供される。SPICEデータは異なり、変換されたIBISモデルのデータは異なります。すなわち、製造業者Aの装置が使用されるならば、彼らが彼らの装置のために正確なモデルデータを提供することができるだけであるというわけではありません。ベンダーによって提供されるIBISが正確でないならば、唯一の基本的な解決は常にベンダーをそれを改善するよう頼むことです。

高速PCBの設計において設計者がEMCとEMIのルールを考慮すべきか

一般的に、EMIまたはEMC設計は、放射されて導通した態様の両方を考慮する必要がある。前者は高周波部分(>30 MHz)であり、後者は低周波数部分(<30 MHz)である。だから、高周波数に焦点を当てることはできませんし、低周波を無視する。デバイス位置、PCB積層配置、重要なオンラインルート、デバイス選択のレイアウトの初めに良いEMI / EMC設計を考慮しなければなりません。例えば、クロック発生器の位置をできるだけ外部コネクタに近づけないようにするためには、高速信号をできるだけ内部層に移動させ、特性インピーダンス整合と基準層の連続性に着目して反射を低減する。デバイスによって駆動される信号の傾きは、高周波成分を低減するために可能な限り小さくなければならない。デカップリング/バイパスコンデンサを選択するとき、周波数応答が電力層ノイズを低減するための要件を満たしているかどうかに注意を払う。加えて、放射線を減らすためにループ面積(すなわちループインピーダンス)を最小にするために高周波信号電流逆流経路に注意を払う。高周波ノイズの範囲は、形成を分割することによっても制御することができる。最後に、PCBとシャーシとの間のシャーシ接地を適切に選択する。

EDAツールの選択方法

現在のPCB設計ソフトウェアでは、熱解析は強い点ではないので、それを使用することは推奨されません。他の機能については、1.3.4パッドまたはケイデンスを選択することができます両方のパフォーマンスとコスト良いです。PLDデザイン初心者は、PLDチップメーカーによって提供される統合環境を使用することができます100万以上のドアのデザインでは、単一のポイントツールを選択することができます。

32 .高速信号処理・伝送に適したEDAソフトをお勧めします。

一般的な回路設計のために、革新的なパッドは非常に良いです、そして、彼らはしばしばシミュレーションソフトウェアと互換性を持ちます。高速回路設計のために、ケイデンスソリューションを使用してアナログとデジタルのハイブリッド回路は、パフォーマンスと価格のための最良のソフトウェアですが、もちろん、メンターのパフォーマンスは非常に良い、特にその設計プロセス管理が最適である必要があります。(Datangテレコム技術専門家王勝)

33 . PCBボード各層の意味の解釈

トポバーレイ-トップ層のコンポーネント名、トップシルクスクリーンまたはトップコンポーネントの伝説、例えばR 1、C 5、IC 10と呼ばれます。BOOTOMATERRAL --多層と同じもの-あなたが4層のボードを設計して、あなたが自由なパッドまたはビアを置くならば、あなたがちょうどトップ層としてそれを定義するならば、そのパッドが自動的にすべての4つの層に現れます、そして、そのパッドはトップ層に現れるだけであるとして、そのパッドを自動的に表示します。

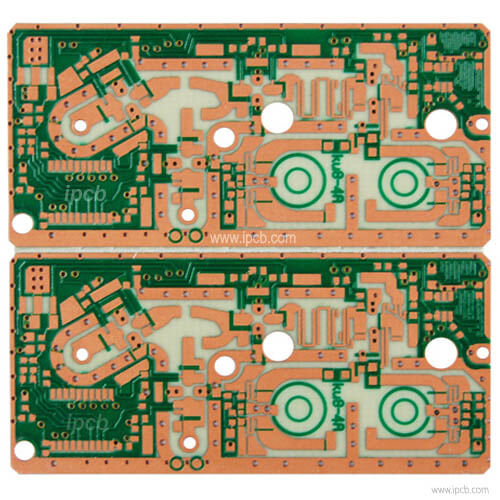

34. 設計上の留意点, ルーティング, と植字 高周波PCB 2 G以上?

2 G以上の高周波PCBはRF回路設計に属し、高速デジタル回路設計の範囲内ではない。レイアウトとルーティングが分配効果を引き起こすので、RF回路のレイアウトとルーティングは、回路と一緒に考慮されるべきです。加えて、RF回路設計は特殊形状銅箔の定義をパラメータ化することによって実現されるので、EDAツールは特殊形状銅箔を編集できるパラメトリックデバイスを提供することが要求される。メンターBoardStationはこれらの要件を満たすためにRFデザインモジュールを専用しています。加えて、一般的なRF設計は特別なRF回路解析ツールを必要とします。

35 .すべてのデジタル信号PCBの場合、ボードは80 MHzのクロック源を有する。ワイヤメッシュ(接地)に加えて、十分な駆動能力を確保するためにどのような回路保護を用いるべきか?

時計駆動機能を確認する, 保護を通じて達成すべきではない, 一般にクロックドライバチップを使用する. クロック駆動能力に関する一般的な懸念は、複数のクロック負荷のためである. クロックドライバチップ, いくつかに1つのクロック信号を回す, ポイントツーポイント接続を採用する. ドライバチップを選択, 負荷との基本的な一致を保証することに加えて, the signal along with the requirements (generally clock along with the effective signal), システムタイミングの計算において, ドライバチップ遅延のクロックを計算するには.