ICパッケージ基板メーカー:チップパッケージ技術リスト

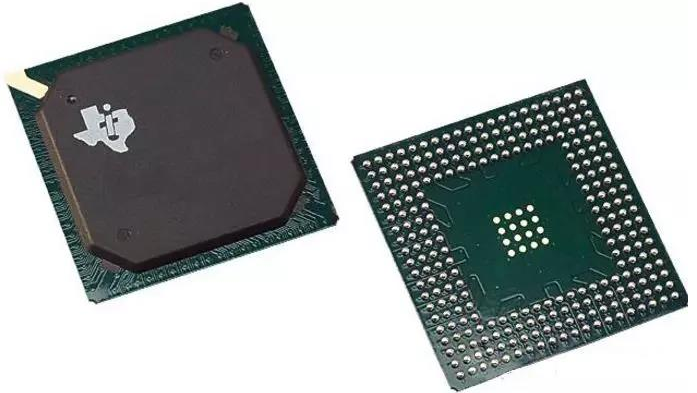

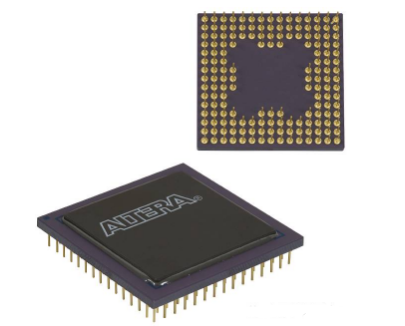

1.BGAグリッドアレイ

CPAC(Globe Top Pad Array Carrier)とも呼ばれます。球面接触ディスプレイ、表面実装型パッケージの1つ。IC PCB背面にはピンの代わりに球形バンプがディスプレイ形式で作成されている。LSIチップはPCBの前面に組み込まれ、モデルを天然樹脂に圧入するか、注入により封止する。凸始点表示担体(PAC)とも呼ばれる。200以上のピンがあり、マルチピンLSI用のパッケージである。パッケージは、QFP(4ピンフラットパッケージ)よりも小さくすることもできる。例えば、コア距離が1.5 mmの360ピンのBGAは31 mm四方しかない、ピン芯距離0.5 mmの304ピンのQFPは40 mm正方形である。BGAはQFPのようなピンバリエーションの問題を心配する必要はありません。

このパッケージは米モトローラ社が開発し、携帯電話などの機器に適用されていることが最初に発覚し、すぐにパソコンで流行した。当初、BGAのピン(バンプ)芯距離は1.5 mm、ピン数は225であった。現在では500ピンBGAを開発しているLSIメーカーもある。BGAの問題はリフロー溶接後の外観検査である。米国のオートバイola企業はこのモデルをMPACと呼ばれる天然樹脂封止パッケージに圧入し、その封止方法をGPACと呼んでいる。

2.C-(セラミックス)

磁器のパッケージを表すためのマーク。例えば、CDIPはセラミックDIPを表す。これは実践でよく使われる記号です。

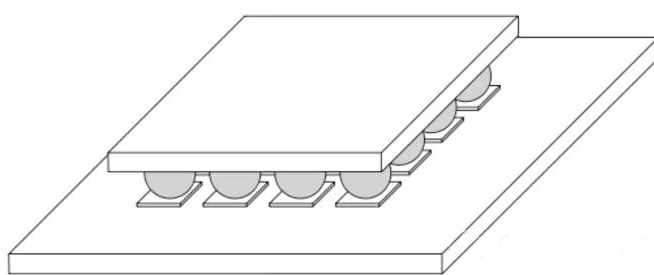

3.COB(オンボードチップ)

オンボードチップ

オンボードチップパッケージは、ベアチップ実装技術の1つです。半導体チップはプリント基板に付着し、リードシーム法によりチップと基板の電気的接続を成功させ、天然樹脂被覆信頼性を採用した。COBは最も簡単なダイ実装技術であるが、パッケージ密度はTABや逆溶接技術よりはるかに低い

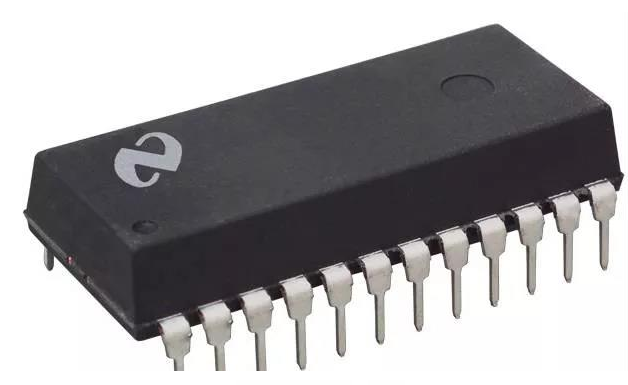

4.DIP(2列直挿パッケージ)

2列直挿パッケージ。ピンはパッケージの両側から引き抜かれています。包装材料は分子複合プラスチックとセラミックスセラミックスである。Europa半導体メーカーはDILを使用している。DIPは最も人気のあるプラグインパッケージで、標準的な思考法IC、ストレージLSI、フラグ回路などの応用に適している。ピンコアは2.54 mm、ピン数は6から64まで。パッケージの幅は通常15.2 mmです。幅7.52 mmと10.16 mmのパッケージの中には、SK-DIP(Skinny Dual In-Line Package)とSL-DIP(Slim Dual In-Line Package)狭胴体DIPと呼ばれるものもあります。しかし、ほとんどのものはDIPと総称されています。また、低融点ガラスで密封されたセラミックDIPはCerdipとも呼ばれる。

4.1 DIC(2列直挿セラミックパッケージ)

セラミックハウジング内のDIP(ガラスでカプセル化)の別の名前。

4.2 Cerdip:

ECLRAM、DSP(デジタル信号プロセッサ)回路用のガラスパッケージセラミック2列直挿パッケージ。窓ガラス付きCerdipは、紫外線消去型EPROMや内部にEPROMがあるフラグ回路などに使用されている。ピン芯は2.54 mm、ピン番号は8から42まで。Toyoでは、このパッケージをDIP-G(Gは緊密に閉じられたガラスを表す)と表現します。

4.3 SDIP(収縮複列直挿パッケージ)

DIPを収縮させる。DIPと同じであるが、ピンコア距離(1.778 mm)がDIP(2.54 mm)より小さいカートリッジパッケージ

そのため名付けられた。ピンの数は14~90です。セラミック陶器と分子複合プラスチックの2種類があります。Sh−dipとも呼ばれる(収縮二列直挿パッケージ)

5.ページをめくる

チップの逆溶接。ベアチップパッケージ技術の一種で、LSIチップの電極領域に金属バンプを作製し、圧力溶接によりプリント基板の電極領域に接合する。パッケージの被占有平面または物体表面の寸法は、基本的にチップ寸法と同じである。これはすべてのパッケージ技術の中で最も小さく、最も薄いものです。しかし、基板の熱膨張係数とLSIチップの熱膨張率が異なると、反応が接合部で発生するため、接合の信頼性が影響を受けることになる。これはLSIチップを天然樹脂で補強し、ベース基板材料の熱膨張係数を用いなければならないからである。

6,FP(フラットパッケージ)

平たい包装。外装の1つ。QFPまたはSOP(QFPおよびSOPを参照)。現地の半導体メーカーは、適切だと考えているため、この名前を使用しています。

7,H-(ヒートシンク付き)

ヒートシンク付きのタグを表します。例えば、HSOPはヒートシンク付きSOPを表す。

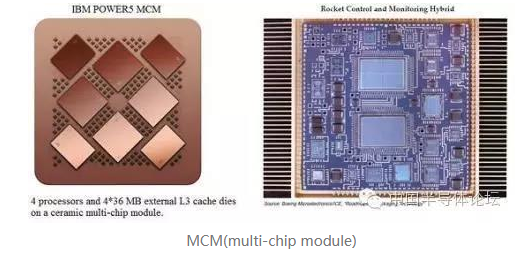

8、MCM(マルチチップモジュール)マルチチップモジュール

9,P-(プラスチック)

プラスチック包装には分子化合物の標識が表示されている。PDIP発現のような分子複合プラスチックDIP。

10、子豚の背中

パッケージがロードされました。セラミックセラミックパッケージ、コンセント付き、形状はDIP、QFP、QFNと類似している。信用プロセスの動作を明確に認めるために、標識付き施設を開発するために使用されます。たとえば、EPROMをソケットに差し込んで調整します。この包装は基本的に固定製品であり、市場にはあまり流通していない。

11.QFP(Quad Flat Package)四辺ピンフラットパッケージ

四角形フラットパッケージ

外部実装パッケージとして、ピンが4つの側面から引き出され、カモメの翼(L)形状をしている。基材にはセラミックス、金属、分子複合プラスチックの3種類がある。プラスチック包装の数を見ると、分子化合物が圧倒的に多い。材料に特別な発現がない場合、ほとんどの場合は分子複合プラスチックQFPである。分子複合プラスチックQFPは、最もポピュラーなマルチピンLSIパッケージである。マイクロプロセッサ、ゲートディスプレイなどのデジタル思考規則のLSI回路だけでなく、VTR信号処理、オーディオ信号処理などのアナログLSI回路にも使用されている。ピン芯ピッチ1.0 mm、0.8 mm、0.65 mm、0.5 mm、0.4 mm、0.3 mmなどの仕様。0.65 mmコアピッチ規格における最大ピン数は304である。

LSIメーカーの中には、ピンコア距離が0.5 mmのQFPを、具体的には収縮QFPまたはSQFP、VQFPと呼ぶものもある。しかし、一部のメーカーでは、0.65 mmと0.4 mmのピン-コア距離QFP(SQFPとも呼ばれる)を一緒にして、名前を少し混乱させることができます。

JEDEC(電子施設委員会)基準によると、ピン−コア距離が0.65 mm、本体厚さが3.8 mm〜2.0 mmの追加QFPはMQFP(メートル法4平面パッケージ)と呼ばれる。55 mm、0.4 mm、0.3 mmなど0.65 mm未満のQFPをQFP(FP)(QFP細ピッチ)と呼び、小芯距離QFP。FQFP(細ピッチ4平面パッケージ)とも呼ばれます。しかし現在、東洋電子機械工業協会のQFP外形規格の実施は新たな名声を得ている。ピンコア距離に差はないが、パッケージの厚さによって、QFP(2.0 mm~3.6 mm厚)、LQFP(1.4 mm厚)、TQFP(1.0 mm厚)の3種類に分類される。

QFPの欠点は、ピン芯距離が0.65 mm未満の場合、ピンが曲がりやすいことである。ピンの変形を避けるために、いくつかの改良されたQFP品種が登場している。例えば、包装の四隅に木の指のBQFPがあり、衝突パッドを軽減する(11.1参照)、GQFPは天然樹脂を採用し、ピン先端を覆うリングにできるだけ配慮している。ピンの変形を回避するために、パッケージにテストバンプを設定し、専用治具に配置することでTPQFPをテストすることができます。思考規則LSIにおいては、多層セラミックスQFPに実装された開発製品や高信頼性製品が多い。最小ピン芯距離0.4 mm、最大ピン数348の製品も提供する。このほか、ガラスパッケージのセラミックQFP(11.9参照)もあります。

11.1 BQFP(バンパー付き四面パッケージ)

BQFP

私たちの側面ピンは平らにパッケージングされ、衝突緩和パッドとなっています。QFPパッケージの1つであり、パッケージの4つの隅に突起(衝突緩和パッド)が設けられ、輸送中にピンが曲がらないようにしている。米国の半導体メーカーは、主にマイクロプロセッサやASICなどの回路でこのパッケージを適切に使用している。ピンコア距離は0.635 mmで、ピン数は84個から約196個まで様々である。

11.2 QIC(四線セラミックパッケージ)

セラミックQFPの別の名前。地元半導体メーカーが適切と判断した名称。

11.3 QIP(四線プラスチック包装)

分子複合プラスチックQFPの別称。地元半導体メーカーが適切と判断した名称。

11.4 PFP(プラスチック平板包装)

分子複合プラスチック平板包装。分子複合プラスチックQFPの別称。現地LSIメーカーが適切と判断した名称。

11.5 QFH(四平面高パッケージ)

四角ピンの厚い胴体の平らな包装。プラスチックQFPの分子化合物であり、包装本体の切断を避けるために、QFP本体はより厚く作られている。地元半導体メーカーが適切と判断した名称。

11.6 CQFP(保護リング付き4フィアットパッケージ)

四角いピンを平らに包装し、最適なケアリングを持っています。分子複合プラスチックQFP、その中の1種のピンは天然樹脂を採用し、できるだけリングの遮蔽を配慮し、屈曲変形を避ける。プリント基板上にLSIを組み立てる前に、最適なケアリングからピンを切断し、カモメの羽形状(L型)にした。この包装は米国のオートバイola企業で量産されている。ピン芯距離は0.5 mm、ピン数は最大約208個。

11.7 MQUAD(金属四角形)

米オーリン社はQFPパッケージ計画を策定した。基材と蓋は、アルミニウムを用いて接着剤で密封するのに適していると考えられている。自然空冷条件下では、出力は2.5 W〜2.8 Wに達することができる。東洋新軽電工業企業は1993年にフランチャイズ権を取得して生産

11.8リットル-4気筒

セラミックセラミックはQFPの1つです。窒化アルミニウムはパッケージ基板として、ベースの熱伝導率はアルミニウム酸素の7 ~ 8倍であり、良好な放熱性能を有する。パッケージのフレームはアルミナであり、チップはポッティングによって密封され、コストを制限している。自然空冷条件下でのW 3電力の使用を可能にする思考法則LSIのために開発されたパッケージです。208ピン(0.5 mmコアピッチ)と160ピン(0.65 mmコアピッチ)LSI Mindruleパッケージの開発が完了し、1993年10月に量産を開始した。

11.9 Cerquad

緊密に閉じられたセラミックQFPの下でDSPなどの思考規則をカプセル化するためのLSI回路である外装パッケージ。Windows付きCerquadはEPROM回路をカプセル化するために使用されます。その放熱性能は分子複合プラスチックQFPより優れており、自然空冷条件下で1.5〜2 Wの電力を許容することができる。しかし、包装コストは分子複合プラスチックQFPの3〜5倍である。ピン芯ピッチは1.27 mm、0.8 mm、0.65 mm、0.5 mm 0.4 mmなどの仕様。ピンの数は32~368です。

12.QFG(Quad Flat J-Leade Package)四辺Jピンフラットパッケージ

外装の1つ。ピンはパッケージの4つの側面から引き出して、下のJ形をしています。東洋電子機械工業協会が定めた名称である。ピン芯の間隔は1.27 mm。材料は分子複合プラスチックとセラミックスの2種類がある。

分子複合プラスチックQFJは、フラグ、ゲート表示、DRAM、ASSP、OTPなどの回路に使用されるPLCC(プラスチックリードチップキャリア)と呼ばれることが多い。ピンの数は18~84です。

セラミックQFJは、CLCC(セラミックリードチップキャリア)およびJLCC(J−leaded chip carrier)とも呼ばれる。ウィンドウパッケージは、紫外線消去型EPROM及びEPROMを有するフラグチップ回路に用いられる。ピンの数は32~84です。

13.QFN(四平面無リードパッケージ)

四辺無ピンフラットパッケージは、高速および高周波ICパッケージ用の外部実装パッケージである。現在はLCCと呼ばれることが多い。QFNは東洋電子機械工業協会が定めた名称である。パッケージの四辺にはすべて電極接点が取り付けられており、ピンがないため、ブラケットのサイズは平面または物体の表面を占め、QFPのサイズより小さく、高さはQFPよりも低い。しかしながら、プリント基板とパッケージとの間の開始応力が電極接触で解放されない場合。このような電極接触はQFPピンのように多くはないため、通常14〜100程度である。

材料はセラミックスと分子複合プラスチックの2種類がある。LCCが表示されている場合、多くはセラミックQFNです。電極接点の芯距離は1.27 mmである。分子複合プラスチックQFNは低コストのガラス−エポキシガス−天然樹脂プリント基板パッケージである。電極接点のコアピッチ1.27 mmのほか、0.65 mmと0.5 mmの2種類がある。このパッケージは分子複合プラスチックLCC、PCLC、P-LCCなどとも呼ばれる。

13.1 PCLP(プリント基板のリードレスパッケージ)

プリント基板にはリード線パッケージがありません。東洋富士通は、分子複合プラスチックQFN(分子複合プラスチックLCC)を適正使用名称としている。ピン芯距離は0.55 mmと0.4 mmの2種類の規格があります。これまで開発段階にあります。

13.2 P-LCC(プラスチック非引裂きチップキャリア)(プラスチックリードチップライブラリ)

分子複合プラスチックQFJであることもあれば、QFN(分子複合プラスチックLCC)であることもある(QFJおよびQFNを参照)。ローカルLSIメーカーは、PLCCを使用してリード線のあるパッケージを表し、P-LCCを使用してリード線のないパッケージを表して差異を表示します。

14.QFI(Quad Flat I-Leaded Packgage)四面Iピンフラットパッケージ

外装の1つ。ピンはパッケージの4つの側面から描き、I字まで下に描きます。MSP(ミニスクエアパッケージ)とも呼ばれます。溶接を結合するための配置と印刷基板。ピンには先端の一部がないため、ベースが平面または物体表面を占める寸法はQFPより小さい。日立製作所は、このビデオファイルシミュレーションIC用パッケージを開発し、使用している。また、Toyo MotorolaのPLL ICもこのパッケージの使用に適していると考えられています。ピン芯距離は1.27 mmで、ピン番号は18~68です。

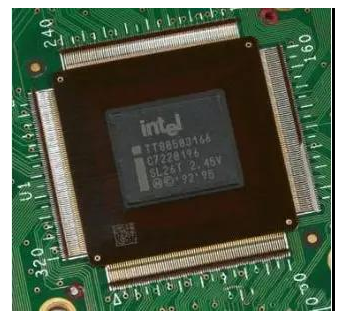

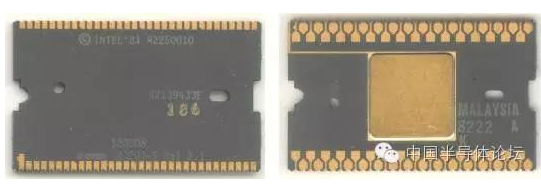

15.TCP(Tape Carrier Package)フィルム封入TCP技術

TCP

主にインテルモバイルPentiumMMXで使用されています。TCPパッケージを適切に使用するCPUの熱は、一般的なPGAピンアレイCPUよりもはるかに小さく、後者はノートパソコンに使用して追加ヒートシンクのサイズを小さくし、ホストの空間利用率を高めることができ、これは少数の超ノートパソコンでは一般的です。しかし、TCPパッケージはCPUをマザーボードに直接溶接するため、一般ユーザーが交換するのは容易ではない。

15.1 DTCP(デュアルキャリアパッケージ)

荷重パック付き二重ピン。TCPの1つ(ロードパッケージ付き)。ピンは絶縁テープ上に製造され、パッケージの両側から引き出される。TAB(半自動負荷溶接)技術のため、パッケージは非常に薄い。LSIを液晶露光で駆動するために一般的に使用されていますが、多くはカスタム製品です。

また、ストレージ用の厚さ0.5 mmのLSIブックパッケージを開発している。東洋ではEIAJ(東洋電子機械工業)規格によりDTCPがDTPと命名されている。

15.2 QTCP(4ベルトキャリアパッケージ)

ロードパック付き四辺ピン。絶縁テープにピンを形成し、パッケージの4つの側面から退出するTCPパッケージの1つ。TAB技術を用いた薄い包装です。東洋ではQTP(Quad Tape Carrier Package)と呼ばれている。

15.3テープ自動接着(TAB)テープ半自動接着技術

粘着テープ自動結合(TAB)半自動結合は、複数の接続脚を有する大規模集積回路(IC)チップであり、従来のパッケージを使用して完全な個体になるのではなく、TABキャリアを使用し、未密封のチップを直接プレート表面に接着する。柔軟な「ポリイミド」テープと銅箔エッチングの内外ピンを担体として使用し、大きなチップをまず内部ピンに付着させる。半自動テスト後、回路基板を「外部ピン」に接合することで組み立てが完了します。この包装と組み立ての新しい施工方法、すなわちTAB法。

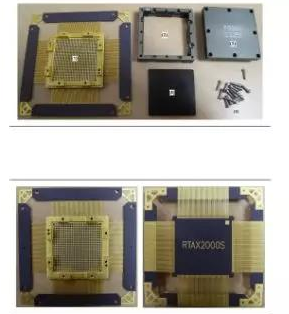

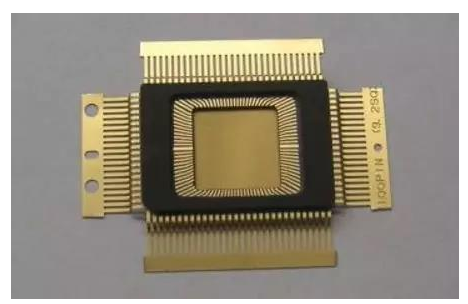

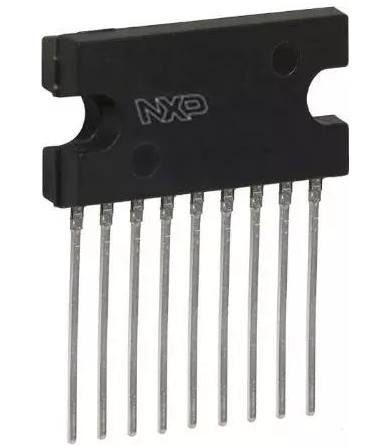

16、PGA(ピングリッドアレイ)

PGA

ピンパッケージを表示します。ボックスパッケージの1つで、底面に直接配置されてパターン配列を表示する。パッケージ基板は一般的に適切と考えられ、多層セラミック基板が用いられる。材料名が具体的に示されていない場合、多くはセラミックスPGAであり、高速大規模な考え方LSI回路に使用されている。コストが高い。ピン芯距離は一般的に2.54 mm、ピン長は約3.4 mm、ピン数は64個から約447個である。コスト削減のために、包装基板の代わりにガラスエポキシガス天然樹脂プリント基板を用いることができる。

プラスチックPGAにも64〜256個のピンの分子化合物がある。また、1.27 mmのピン芯距離、1.5 mm〜2.0 mmのピン長さが短いピン表面実装型PGA(フィレットPGA)があり、挿入型PGAより半分小さいため、パッケージはそれほど大きくなく、ピン数は挿入型(250〜528)より多いことができる。

17、LGA(ランドグリッドアレイ)

LGA

担当者はパッケージを展示します。すなわち、底面側に溝電極接点アレイを有するパッケージを作製する。ソケットに差し込むだけで組み立てられます。227個の接点(1.27 mm芯距離)と447個の接点(2.54 mm芯距離)を有するセラミックLGAは、高速思考規則LSI回路に応用されている。QFPに比べて、LGAはより小さなパッケージにより多くの入出力ピンを収容することができます。また、このリードはその低インピーダンスのため高速LSIに適している。

18.チップ上のリードパッケージ

LSIパッケージ技術は、リードフレームの先端をチップの上に置き、チップコアの近傍にバンプ溶接点を製造し、リード線を縫合して電気的な協同プログラミングを行う構造である。同じ体積のパッケージでは、リードフレームがチップの側面付近に配置された元の構造と比較して、チップの幅は約1 mmであってもよい。

19、試験(四線制セット)

Quad-In Lineは、Quillと呼ばれる4ピン直列パッケージです。ピンはパッケージの両側から引き出し、交差する間隔で下に4列に曲げられています。ピンコア距離は1.27 mmで、プリント基板を挿入するとコア距離は2.5 mmになります。これは標準プリント基板に適しているためです。は、標準DIPよりも小さいパッケージです。東洋電気は、デスクトップパソコンや家電製品のロゴチップに適切なパッケージを使用しています。材料はセラミックスと分子複合プラスチックの2種類がある。ピン数64。

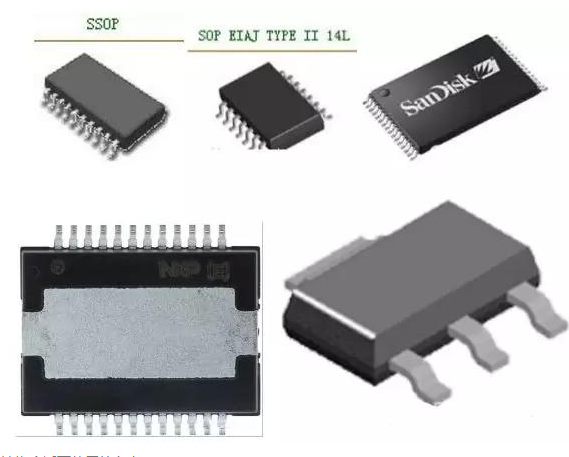

20.SOP(小型ライン外装)

小型包装。外装のパッケージとして、引脚がパッケージの両側から引き出され、カモメの羽の形(L形)をしている。材料は分子複合プラスチックとセラミックスの2種類がある。SOL(Small Out Line L Leaded Package)、DFP(Dual Flat Package)、SOIC(SmallOut Line Integrated Circuit)、DSO(Dual Small)Out lint)とも呼ばれ、多くの海外半導体メーカーがこの名称を使用している。

SOPはメモリLSIだけでなく、小型ASSP回路にも広く応用されている。SOPは、入出力端子が10〜40を超えない分野で最もポピュラーな表面実装パッケージである。ピン芯距離は1.27 mmで、ピン番号は8~44です。

SOPが進展するにつれて、それは徐々に納品される:

針芯距離が1.27 mm未満のSSOP(大S OPから小SOPまで)、

組立高さが1.27 mm TSOP未満(薄型小パッケージ)、

VSOP(超小型包装)、TSSOP(Thin from Large to Small SOP);

SOT(小型接合型トランジスタ)、ヒートシンク付きSOPはHSOPと呼ばれ、

現地の半導体メーカーはSOPをヒートシンクレスFin SONF(小型非ヒートシンク)と呼び、

現地メーカーによるワイドボディSOP(ワイドJタイプ)SOW

21.MFP(ミニフラットパッケージ)小型フラットパッケージ

分子複合プラスチックSOPまたはSSOP別名。地元半導体メーカーが適切と判断した名称。

22、SIMM(単列メモリモジュール)

シングルラインストレージコンポーネント。プリント基板の片側付近にのみ電極を備えたメモリモジュール。一般的にコンセントに差し込むコンポーネントを指します。標準SIMMには30電極があり、コアピッチは2.54 mm、72電極、コアピッチは1.27 mmである。プリント基板の片側または両側にSOJで1と4メガバイトDRAMをカプセル化したSIMMは、パーソナルコンピュータ、オフィスステーション、その他の施設に広く使用されている。少なくとも30〜40%のDRAMはSIMMに組み込まれている。

23、DIMM(2列直挿メモリモジュール

SIMMと非常に似ていますが、DIMMの金の指の両端はSIMMのように通信していません。逆に、DIMMのゴールドフィンガーの両端は互いに独立して通信しており、これは大量のデータ信号の伝送需要を満たすことができるためである。同様にDIMM、SDRAMインタフェースとDDRメモリインタフェースを適切に使用することも少し異なると考えられ、SDRAM DIMMは168 PIN DIMM構造で、金の指の各側は84 PINで、金の指の頭には2枚のカードがあり、スロットへの挿入を防止するために使用され、メモリが逆方向に正しく挿入されず、焼録破壊をもたらした、DDR DIMMは184 PIN DIMM構造を使用するのが適切だと考えており、金指の両側にはそれぞれ92 PINがあり、金指の頭部には引っ掛かりが1つしかない。銃剣の数が異なるのは、両者の最も浅い違いである。

DDR 2 DIMMは240 PIN DIMM構造で、金指の両側にはそれぞれ120 PINがある。DDR DIMMのように、金の指の頭にはカードが1枚しかありませんが、DDRメモリがDDR 2 DIMMに挿入できないため、カードの位置はDDR DIMMと少し異なります。DDR 2メモリはDDR DIMMとDDR 2 DIMMの両方を持つマザーボードにメモリ挿入エラースロットの問題が表示されないため、DDR DIMMを挿入できません。

24,SIP(単線パッケージ)

単一直列パッケージ。ほとんどの欧州半導体メーカーは、SIL(単線)という名称を適切だと考えて使用しています。ピンをパッケージの片側から描き、直線上に並べます。プリント基板に組み込まれると、パッケージは横方向の位置にある。ピン芯距離は一般的に2.54 mmで、ピンの数は2個から23個まで様々で、多くはカスタマイズ製品である。包装スタイルはそれぞれ違います。ZIPパッケージと同じスタイルをSIPと呼ぶ人もいる。

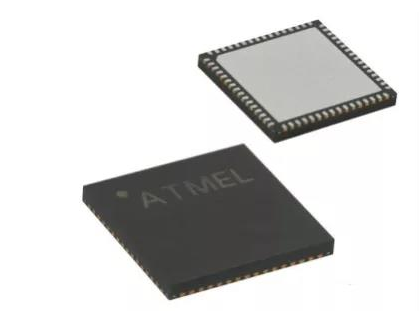

25.SMD(表面実装デバイス)

SMDチップ

外観実装部品。半導体メーカーの中には、SOPをSMDに分類するものもある。

26.SOI(スモールアウトIリードパッケージ)

私は小さな包装をします。外装の1つ。ピンはパッケージの両側から引き出され、下向きのI形をしており、コアピッチは1.27 mmである。ブラケットはSOPよりも小さい物体の平面または表面を占めている。日立は、ダミーIC(モータ駆動盗用IC)にこのパッケージを使用している。ピン数26。

27.SOJ(スモールアウトJリードパッケージ)

Jピン小型包装。外装の1つ。ピンがパッケージの両側から下にJ字になっていることから名付けられた。通常は分子プラスチックで作られ、主にDRAMやSRAMなどのメモリLSI回路に使用されていますが、主にDRAMに使用されています。SOJに実装されているDRAMコンポーネントの多くはSIMM上に組み込まれています。ピンコアの間隔は1.27 mmで、ピンの数は20~40です(SIMMを参照)。

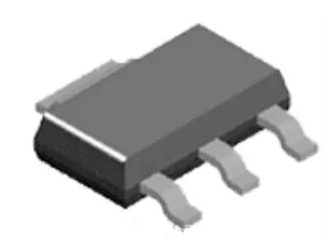

28、包装まで

To PackageTo

そのシャーシは円形の金属板で、それから小さなガラスを入れて加熱し、ガラスが溶融した後にリードを穴に固定し、穴とリードをヘッドセットと呼ぶので、まずヘッドセットの上でヘッドに金メッキを行う。集積回路シートの底部は金メッキされているので、金、ゲルマニウム溶接ワックスで溶接することができる。溶接時、ヘッドホルダを予熱し、そこに置いた溶接ワックスを絶対に溶融させ、その後回路基板を溶接ワックス上に置き、冷却後両者は良好な結合を形成する。