[ IC基板製造業] ICチップ設計から製造までの全工程

1, 複雑 ICチップ デザイン process

The process of チップ製造 is like building a house with LEGO. ウエハを基礎とした後, それから、チップ製造プロセスは、レイヤーによって、積み重ねられる, 必要 チップ can be produced (these will be introduced later). しかし, 設計図面なしで, 強い生産能力を持つことは役に立たない. したがって, 建築家の役割はとても重要だ. 年に建築家は誰ですか IC デザイン? 次, 本稿では IC デザイン.

に IC生産 process, 大部分 ICsは計画されて、専門家によって設計されます IC 設計会社, mediatekのような, クスクス, インテルと他の有名なメーカー, オールデザイン ICチップsと下流メーカーが選択するために異なる仕様と効率でチップを提供します. だって IC 各工場別設計, IC 設計は技術者の技術次第, そして、エンジニアの質は、企業の価値に影響を及ぼします. しかし, エンジニアが設計するとき ICチップ, ステップは何ですか? 設計プロセスは、単に以下に分けることができます.

IC製造工程

デザイン最初のステップと設定目標

イン アイシーデザイン, 最も重要なステップは仕様です. このステップは、建物を設計する前にどのように多くの部屋やバスルームを必要とするようなものです, どのような建築規則を遵守する必要があります, そして、すべての機能を決定した後に設計すること, その後の変更について追加の時間を過ごさないように. IC デザインも、設計されたチップがどんなエラーもないことを確実とするために、類似したステップを通過する必要があります.

仕様の定式化の第一歩は IC 一般向きを設定する. 次のステップはどのプロトコルを遵守するかを見ることです. 例えば, ワイヤレスネットワークカードのチップは、IEEE 802.11その他の仕様. Otherwise, チップは市販品と互換性がない, 他のデバイスと接続できないようにする. 最後に、 IC, 異なる単位に異なる関数を割り当てる, と異なる単位間の接続方法を確立する, 仕様の定式化を完了するために.

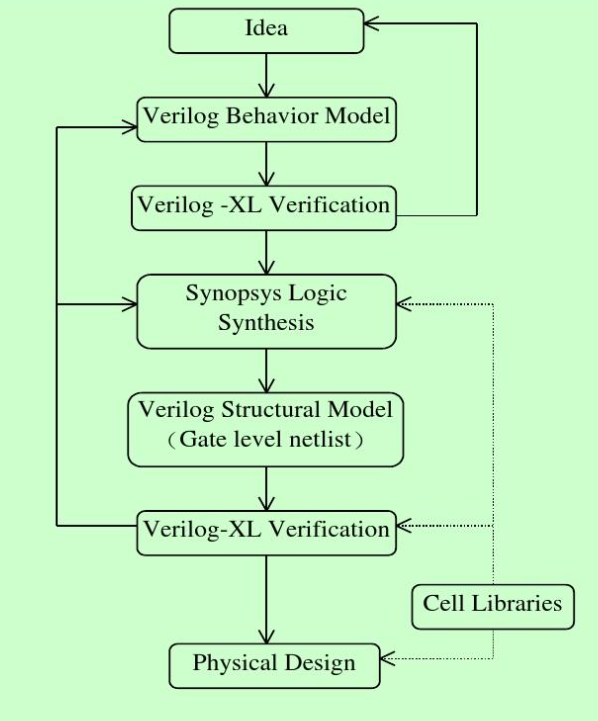

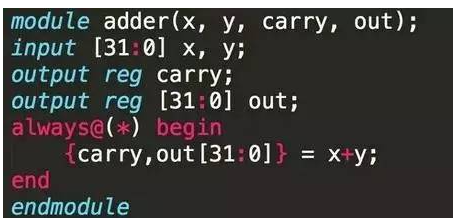

仕様設計後, チップ設計の詳細は以下の通りである. このステップは、最初に建築計画を書き留めて、その後の図面の便宜のために全体的なアウトラインを引き出しているようです. イン ICチップ, hardware description language (HDL) is used to describe the 回路. よく使われるHDLにはVerilogが含まれます, VHDL, etc. の機能 IC 簡単にコードで表現できる. その後、プログラム関数の正しさをチェックして、それが望ましい機能に会うまで、それを変更し続けます.

32ビット加算器のVerilog例

コンピュータではすべてが楽になる

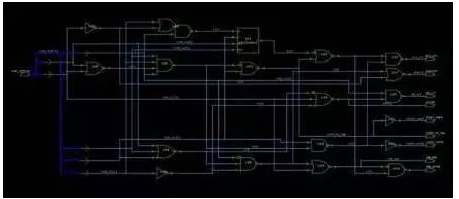

完全な計画では、次のステップは、ボードデザインの青写真を描くことです。IC設計において、論理合成のステップは決定されたHDLコードを電子設計自動化ツール(EDAツール)に入れ、コンピュータをHDLコードを論理回路に変換して次の回路図を生成することである。次に、論理ゲート設計図が仕様を満たしているかを繰り返し、その機能が正しいまで修正する。

制御ユニット合成の結果

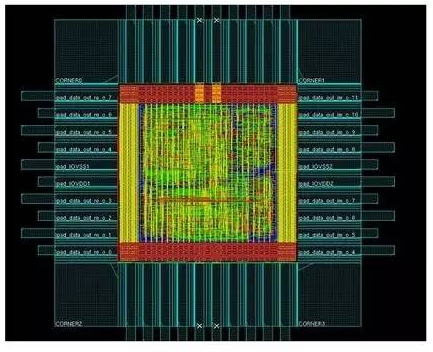

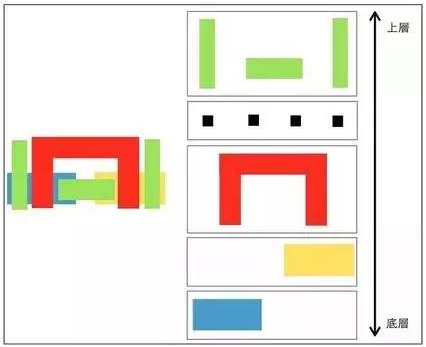

最後に、回路レイアウトと場所とルートのためのEDAツールの別のセットに合成コードを入れてください。連続検出後、以下の回路図を作成する。画像では、青、赤、緑、黄色などのさまざまな色を見ることができます。各々の異なる色は、軽いマスクを表示します。マスクの使い方は?

レイアウトと巻き

マスクの層は、チップを積層

まず第一に, それは知られている IC 複数のマスクを生成する. これらのマスクは上下の層を有する, そして、各レイヤーには独自のタスクがあります. 次の図は単純なマスクの例です. CMOSの取得, 集積回路における最も基本的な要素, 例として, CMOSの完全名称は相補型金属酸化物半導体である, それで, NMOSとPMOSを組み合わせてCMOSを形成する. As for what is metal oxide semiconductor (MOS)? この種のチップで広く使われているコンポーネントは説明するのが難しい, そして、普通の読者が理解するのは難しい. もっと勉強しない.

以下の図において、左側は回路レイアウトと巻線の後に形成される回路図である。各色はマスクを表すことが知られている。右側は各フードの広がりです。製造は底から出発して、ICチップの製造に関する前の記事で提案された方法に従って、それらを層ごとに作り、最終的に所望のチップを生産する。

今まで, 我々には予備的な理解が必要だ アイシーデザイン. 概して, 明らかに IC デザイン is a very complex specialty. コンピュータ支援ソフトウェアの成熟度, IC デザイン can be accelerated. The IC 設計工場はエンジニアの知恵に大きく依存する. ここで説明された各ステップは、独自の専門知識を持っており、独立して複数の専門コースに分割することができます. 例えば, ハードウェア記述言語の記述は単純ではない. それはプログラミング言語に精通している必要があるだけです, しかし、論理回路がどのように動作し、どのように合成ソフトウェアが論理ゲートにプログラムを変換するかプログラムに変換する方法を理解する必要もある.

2、どのようなウェーハですか?

イン the news of 半導体, 私たちはいつもサイズでマークされたウエハ工場に言及します, 8インチまたは12インチウエハ工場. しかし, いわゆるウエハーとは? どの部分が8インチですか? 大型ウエハ製造の難しさ? 以下は半導体の最も重要な基礎への段階的な導入です.

ウエハはあらゆる種類のコンピュータチップを製造するための基礎である。我々は、チップの製造を比較することができますレゴブロックの家を構築し、我々の希望の形状を完了する(すなわち、すべての種類のチップ)層の後に積層して。しかし、良い基盤がなければ、建てられた家は、あなたが望むものではない曲がっているでしょう。完璧な家を作るためには、安定したベースプレートが必要です。チップ製造のために、この基板は次に説明するウェハである。

まず第一に、我々が子供たちとして高層ブロックで遊ぶとき、ブロックの表面に小さな円形の突起があることを思い出しましょう。この構造では、接着剤を使用せずに安定に2つのブロックを積み重ねることができる。チップ製造はまた、同様の方法でその後追加された原子と基板を一緒に固定する。したがって、後の製造に必要な条件を満たすためには、きちんとした表面を有する基板を見つける必要がある。

固体材料中, 特別な結晶構造-単結晶. 原子が一つずつ密接に並ぶ特性, 平らな原子面を形成できる. したがって, 上記の要件は、単結晶を使用してウエハを製造することによって満たすことができる. しかし, そのような材料を生産する方法? つの主な手順:精製と結晶画, そうすると、そのような材料は完成することができます.

ハウツーとスタイル クリスタルウエハー

精製は2段階に分けられる. 第一段階は冶金的浄化である. このプロセスは、主に炭素を加えて、酸化還元によって、98 %以上の純度でシリコンに酸化シリコンを変換することである. 大部分の金属精製, 鉄または銅のような, 十分な純度の金属を得るために、この方法を使用する. しかし, 98 %はまだチップ製造のために十分でなくて、さらに改善されなければなりません. したがって, ジーメンスプロセスは、更なる浄化のために使われます. このように, 半導体プロセスで要求される高純度ポリシリコンが得られる.

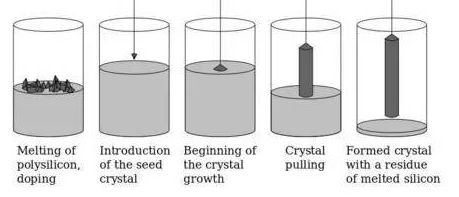

シリコンカラム製造工程

次のステップは結晶画です。まず、得られた高純度ポリシリコンを溶融してシリコンを形成する。その後、単結晶の種子と液体表面に接触し、ゆっくりと回転しながらプルアップします。単結晶シリコンが必要である理由は、シリコン原子の配列がラインの人と同じであるからである。それは、後で人々が正しく配置する方法を知っているように指導者を必要とします。シリコンシードは、後で原子をどのようにキューを知っているように重要なリーダーです。最後に、液体表面を残すシリコン原子が固化した後に、きちんと配置された単結晶シリコンカラムが完成する

単結晶シリコンカラム

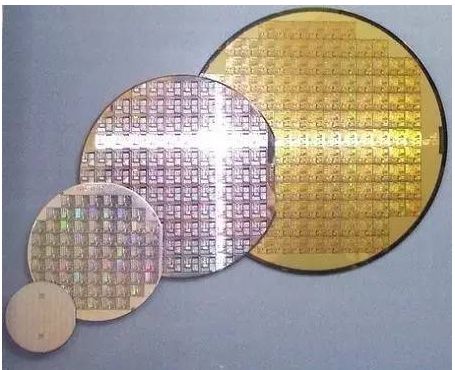

しかし、8インチと12インチは何を表しますか?彼は、鉛筆ホルダーの部分のように見える米国製の水晶柱の直径を指します。表面を処理し、薄い丸い部分にカット。大型ウェハの製作は難しいか

上記の通り, クリスタルコラムの製造工程は綿菓子を作るようなものである, 同時に回転すること. あなたがマシュマロを作ったならば, あなたはそれが非常に堅固なマシュマロを作るのは難しいことを知っている必要があります, そして、結晶画のプロセスは同じです. 回転速度と温度制御は、クリスタルコラムの品質に影響します. したがって, サイズが大きい, 速度と温度の要求が高い. したがって, 8インチウエハより高品質12インチウエハを作ることはより困難である.

しかし, チップ全体の製造のためにシリコン層全体を基板にできない. シリコンウェーハを1つずつ生産するために, シリコン柱をダイヤモンドナイフで水平に切断する必要がある, それから、ウェーハはチップ製造のために必要なシリコンウェーハを形成するために研磨されることができる. 非常に多くの手順, チップ基板の製造は完了する. 次のステップは家を積み重ねることです, それで, chip 製造. チップの作り方?

Layers of stacked chips

After introducing what silicon wafers are, 私も知っている チップ is like building a house with Lego blocks, レイヤーの後にレイヤーを積み重ねることによって、望ましい形をつくること. しかし, 家を建てるのにかなりのステップがある, そしてそうです IC manufacturing. 製造工程は何か IC? 本論文では、その過程を紹介する ICチップ manufacturing.

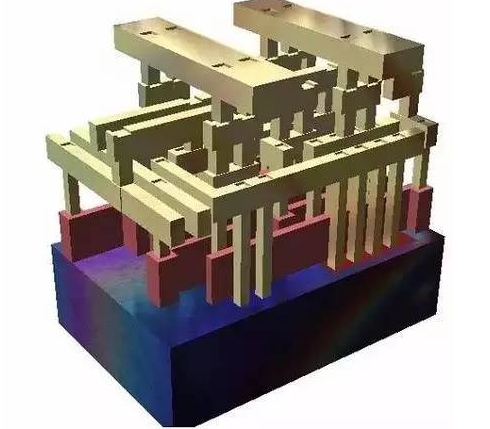

始める前に, まず何を理解すべきか ICチップ is. IC, 集積回路の完全名, 設計された回路を積み重ねて組み合わせるという名前から見ることができる. この方法で, 回路を接続するのに必要な面積を減らすことができます. 次の図は IC 回路. その構造は家の柱や柱のようである, 積み重ねられた層, 何故なら IC 製造は家を建てることと比較される.

ICチップの3 Dプロファイル

上の図のICチップの3 Dプロファイルから、下部の濃い青部分は前の記事で紹介されるウェーハです。この図から、ウェハ基板がチップ内でどのように重要かをより明確に知ることができる。赤とカーキの部品はIC製造中に完成される。

まず第一に, 赤の部分は高層ビルの1階のホールと比較することができる. 1階のホールは家の入り口です. 人が出入りするところだ. これは通常、トラフィックの制御下でより多くの機能があります. したがって, 他の床に比べて, 建設は、より複雑で、より多くのステップを必要とします. に IC circuit, このホールは論理ゲート層である, これが全体の中で最も重要な部分です IC. 様々な論理ゲートを組み合わせて完成させる ICチップ 完全な機能で.

黄色の部分は、一般的な床のようです. 一階と比べると, それはあまり複雑な構造を持ちません, そして、工事中に各フロアはあまり変更されません. この層の目的は論理ゲートを赤の部分に接続することである. それほど多くの層が必要である理由は、一緒に接続されるにはあまりに多くの線があるということです. 単一の層がすべての行に対応できない場合, この目標を達成するためにいくつかの層を積み重ねなければならない. この過程で, 異なる層のラインは、配線要件を満たすために上下に接続される.

Layered construction and layer by layer structure

After knowing the structure of IC, 作り方を紹介します. 我々はペイントスプレーを使用して微細な図面を作りたい場合は想像してください, 私たちは図の表紙を切り取り、紙の上に覆う必要があります. その後、紙に均等に塗料をスプレー. 塗装後ドライ, シャッターを外す. 繰り返す, きちんとした、そして、複雑なグラフィックスは完了することができます. 製造 IC 同じように覆うことによって層ごとに積み重ねること.

作るとき IC, それは単に上記の4つのステップに分けることができます. 実際の製造では製造工程と材料は異なるが, 一般的に同様の原理が採用されている. このプロセスはペイントペインティングと少し違う. IC 製造は、最初に被覆されて、それからカバーされます, ペイント塗装は、最初に覆われているし、塗装. 各々のプロセスは以下で説明されます.

金属スプラッシング:薄膜を形成するためにウエハ上で使用される金属材料を均一に撒く.

コーティングフォトレジスト:まず、フォトレジスト材料をウェハ上に置く, pass through the mask (the principle of the mask will be explained 次 time), 不要な部分にビームを当てる, フォトレジスト材料の構造を破壊する. Then, 破損した材料は化学薬品で洗い流される.

エッチング技術:フォトレジスト保護のないシリコンウエハをイオンビームでエッチングする.

-フォトレジスト除去:フォトレジスト除去液を用いて残留フォトレジストを溶解する, プロセスを完了するために.

最後に, 多く チップ will be completed on a whole wafer. 次, 完成した正方形の限り ICチップsを切る, それらは 包装 ファクトリー 包装. 何が 包装 ファクトリー? 後で説明します.

各種ウエハの比較

3、ナノ加工プロセスは何ですか?

先進的な半導体製造プロセスでは、SamsungとTSMCは非常に熱い. 彼らは両方の命令を得るために、ウェハの鋳造所でリードを取るか. それはほとんど14 nmと16 nmの間の論争になりました. しかし, 14 nmと16 nmの2つの数の意味は何か, そしてどの部分が? プロセスを減少させた後の将来の利益と問題点? 以下のナノプロセスを簡単に説明します.

どのように微妙な ナノ?

始める前に, まずナノが意味するものを理解すべきだ. 数学的に, ナノメータは0である.億分の1メートル, しかし、これは非常に貧しい例です. 結局, 小数点以下はゼロしか見えません, しかし、我々は実用的な感じを持っていない. 釘の厚さが比較されるならば, もっと明らかかもしれない.

あなたが支配者とゲージで実際に測定するならば, 爪の厚さは約0です.0001 meter (0.1 mm), それで, 10万の線に釘の側面を切るようにしなさい, そして、各々の線は、およそ1 nm. したがって, あなたはどのように小さな.

ナノがどれくらい小さいかを知った後, 我々はまた、プロセスを減らす意図を理解する必要があります. トランジスタを減らす主な目的は、より多くのトランジスタをより小さなチップに挿入することである, チップが技術的な改善のために大きくならないように第二に, それは、プロセッサの操作効率を増やすことができますMoreover, ボリュームを減らすことは、また、消費電力を減らすことができる最後に, チップのサイズが縮小された後, これは、将来的に軽量のニーズを満たすためにモバイルデバイスに接続するのは簡単です.

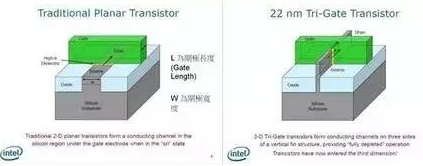

その後、ナノプロセスは何かを探るために戻ってくる. 例として14 nm. プロセスは、チップ内の最小ワイヤが14 nmであることを意味する. 以下の図は、例として従来のトランジスタの外観を示す. トランジスタを減らす主な目的は、消費電力を低減することである, しかし、この目的を達成するためにどの部分を削減すべきか?

下の左の図のLは、我々が縮小すると思っている部分です. ゲート長を減らすことによって, the current can use a shorter path from the drain end to the source end (if you are interested, あなたは、MOSFETを検索するGoogleを使用することができます, which will be explained in more detail).

また、コンピュータは0と1で動作する。どのように、トランジスタはこの目的を満たすことができますか?方法は、トランジスタが電流フローを有するかどうか判断することである。ゲート端子(緑の四角形)に電圧が供給されると、ドレイン端子からソース端子へ電流が流れる。電圧が供給されないならば、電流は流れません、したがって、我々が判断のために0と1を使う理由のために、それは1と0の1 / 4の1 / 5を表します。このメソッドを使ってコンピュータを作ります。

Size reduction has its physical limitations

しかし, 製造工程を無期限に減らすことはできない. トランジスタを約20 nmに減らすと, 量子物理学の問題に遭遇する, トランジスタが漏れているように, Lが減少するときに得られる利益を相殺する. 改善方法として, the concept of FinFET (tri gate) is introduced, 右上の図に示すように. インテルの以前の説明では, この技術の導入は物理現象による漏れを低減できることが知られている.

さらに重要なことに、この方法はゲート端と下層との間の接触面積を増大させることができる。従来の手法(左側)では、コンタクト面は1面のみであるが、FinFET(トライゲート)技術を用いた場合、コンタクト面は3次元となり、コンタクト面積を容易に増加させることができる。このようにして、同じドレイン面積を維持しつつ、ソースドレイン端を小さくすることができ、これにより、サイズを小さくするのに非常に役立つ。

最後に, それは、いくつかの人々は、主要な工場は、10 nmプロセスを入力するときに非常に厳しい課題に直面すると言う理由です. 主な理由は、原子の大きさが約0であるということです.1 nm. 10 nmの場合, 線には100原子しかない, 製造はかなり難しい, そして、一つの原子の欠陥がある限り, 原子が落ちたり不純物が生成したりする, 未知の現象がある, これは、製品の歩留まりに影響します.

あなたが困難を想像することができないならば, 小さな実験ができる. Line up a 10 with 100 beads on the table * 10 square, そして、ビーズを覆うために紙を切る, 次に、小さなブラシで次のビーズをオフブラシ, and finally make him form a 10 * A rectangle of 5. このように, 我々は、主要な工場が直面している困難や、この目標を達成するのがいかに難しいかを知ることができる.

As Samsung and TSMC will complete the mass 生産 of 14 nm and 16 nm FinFET in the near future, 彼らは両方のアップルの次世代iPhoneチップのOEMのために競争したい. 我々は非常に素晴らしい商業競争を見て、より多くの省電力と軽量携帯電話を入手して. ムーアの法則によってもたらされる利益のおかげで.

4カプセル化とは

包装, の最終的な保護と統合 ICチップ

長いプロセスの後, 設計から製造まで, やっと着いた ICチップ. しかし, チップはかなり小さくて細い. それが外側で保護されないならば, それは簡単に傷や破損されます. 加えて, チップのサイズが小さいから, それは手動で大きなシェルなしで回路基板上に配置することは容易ではない. したがって, 本論文では,この論文を紹介し紹介する 包装 next.

現在, つの共通パッケージがあります, 一つは電気玩具で共通のディップパッケージです, 黒のムカデに見える, そして、他のBGAのパッケージは、共通のCPUを購入するとき. 他に関して 包装 方法, PGA (pin grid array) used by early CPUs; Pin grid array) or improved QFP (plastic square flatpack) of dip. 沢山あるから 包装 方法, ディップとBGA 包装 以下で紹介します.

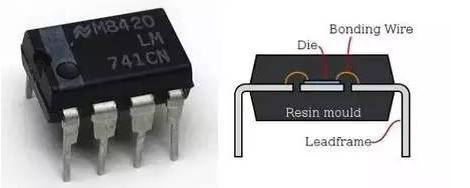

伝統的 包装, lasting

The first thing to introduce is the dual inline package; Dip), 下記の図からわかるように, the ICチップ このパッケージでは、二重列接続の足で黒いムカデのように見えます, どちらが印象的ですか. この 包装 メソッドが初期です IC 包装 テクノロジー, これは、低コストの利点があり、あまりにも多くのワイヤなしで小さなチップに適しています. しかし, 彼らの大部分はプラスチックだから, 放熱効果が悪い, 現在の高速チップの要件を満たすことができない. したがって, このパッケージを使用してチップのほとんどは永続的なチップです, 以下の図のOP 741のような, or ICチップ運転速度の要求が少ないS, 小さいチップとより少ない接続穴.

アンプ断面図

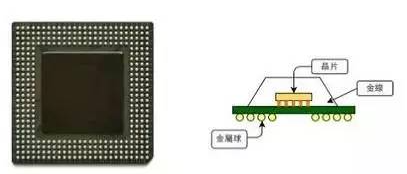

ボールグリッドアレイ(bga)パッケージはdipと比較して,パッケージ体積が小さく,より小型の装置に容易に投入できる。そのうえ、ピンがチップの下に位置するので、それはディップより多くの金属ピンを収容することができます。しかし、この梱包方法はコストが高く複雑な接続方法を有しており、単価の高い製品ではほとんど使用されている。

フリップチップ実装を用いたBGAの回路図

モバイルデバイスの台頭に伴い、新技術がステージに飛躍している

しかし, これらを使う 包装 メソッドはかなりのボリュームを消費します. 例えば, モバイルデバイスおよびウェアラブルデバイスは、現在、さまざまなコンポーネントを必要とする. 各コンポーネントが独立してカプセル化されるなら, それは結合する多くのスペースを消費するでしょう. したがって, 体積減少の要件を満たす2つの方法がある, namely SOC (system on chip) and SIP (system in packet).

スマートフォンの台頭, SOCという用語は主要な金融雑誌で見ることができる. しかし, SoCとは? 要するに, を統合することです IC つのチップに別の機能. このメソッドは、ボリュームを減らすことができません, しかし、別の間の距離を減らす ICsとチップのコンピューティング速度を改善します. 製造方法に関して, それは別の ICsは一緒に IC 設計段階, そして、以前に説明したデザインプロセスを通してマスクを作ります.

しかし, SoCには利点がない. SoCの設計は、かなりの技術協力を必要とする. 時 チップ are packaged, 彼らは外部から保護されている 包装, との間の距離 IC and IC 遠い, だから相互干渉はない. しかし, すべて ICSを包装する together, 悪夢の始まりです. The IC デザインファクトリーはオリジナルのシンプルなデザインから変更すべきである IC に IC これは様々な機能を理解し、統合する, 技術者の労働負担の増大. 加えて, 多くの状況があります, 通信チップの高周波信号のような IC その他の関数.

加えて, SOC also needs to obtain IP (intellectual property) authorization from other manufacturers to put components designed by others into SOC. SoCの製造は全体の設計詳細を必要とするので IC マスクを作る, また、これは、SoC. 何人かの人々はなぜ自分自身を設計しないのか? 様々なデザイン ICsは、関連する多くの知識を必要とします IC, アップルのような多くのお金を持った企業だけが、新しい技術を設計するために有名な企業からトップエンジニアを募集する予算を持つことができます IC. それは自分自身を開発するよりも協力し、認可するより費用対効果が高い IC.

妥協する, SIP appears

As an alternative, SIPは集積チップの段階に飛び込んだ. SoCとは異なる, いろいろ購入 ICsと最後の時間のカプセル化, したがって、IP認可のステップを排除して、設計コストを非常に減らす. 加えて, 独立しているから ICs, 互いの干渉の度合いは大いに減少する.

アップルは、SIP技術をパッケージに使います

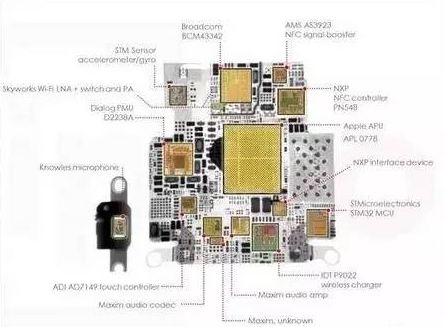

SIP技術を使用して最も有名な製品は、Appleの時計です。時計の内部空間が小さすぎるので従来技術を採用できず,socの設計コストが高すぎ,sipが第一選択となった。sip技術では,体積を減らすだけでなく,各ic間の距離を短縮でき,妥協可能となる。次の図は、Appleウォッチチップの構造図です。かなりの数のICが含まれていることがわかります。

S 1チップの内部構成図

アフター 包装 完了, 試験段階に入る必要がある. At この stage, 包装されたかどうか確認する必要がある IC 通常動作する. 正しい後, それは、我々が見る電子製品を作るために、アセンブリ工場に出荷されることができます. 今まで, 半導体産業は全体の生産作業を完了した.

プロだ 高精度PCB回路基板の研究開発. PCBボードの4 - 46層を大量生産できる, 回路基板, 回路基板, 高周波ボード, 高速ボード, HDIボード, PCB回路基板, 高周波ボード, IC 包装 キャリアボード, 半導体テストボード, 多層回路基板, HDI回路基板, 混合回路基板, 高周波回路基板, ソフトハードボード, などETC