イン PCBボード デザイン, 特に高周波回路, 接地線干渉による不規則現象と異常現象がしばしば発生する. 接地線干渉の原因を解析した, 3種類の接地線干渉の詳細を紹介する, 実用的な経験に基づく解決策を提案する. これらの妨害防止方法は、実際の適用において良好な結果を得ている, いくつかのシステムがフィールドで正常に動作できるようにする. シングルチップマイクロコンピュータシステム, the PCBボード (printed circuit board) is an iエムportant component used to support circuit components and provide electrical connections between circuit components and devices. 伝導プロセスには一定のインピーダンスがなければならない. ワイヤのインダクタンス成分は、電圧信号の伝送に影響を及ぼす, そして、抵抗成分は、電流信号の伝送に影響を及ぼす. インダクタンスの影響は、特に高周波線において深刻である. 接地インピーダンスの影響を注意しなければならない.

1. The reason for the interference

Resistance and impedance are two different concepts. 抵抗は、DC状態の電流に対するワイヤのインピーダンスを指す, そして、インピーダンスはAC状態の電流に対するワイヤの抵抗値を指す, これは主にワイヤのインダクタンスに起因する. 接地線は常にインピーダンスを持つので, マルチメータで接地線を測定する場合, 接地線の抵抗は、一般的には、mm. 長さ10 cmのワイヤーを取る, 1の幅.例として、PCB上の厚さ5 mm、厚さ50, インピーダンスは計算によって得られる. r = 1/s(Ω), where L is the length of the wire (m), s is the cross-sectional area of the wire (mm2), また、△△は抵抗率φ=0である.02, したがって、ワイヤの抵抗値は約0である.026. ワイヤーが他のワイヤーから遠く離れていて、その長さがその幅よりはるかに大きいとき, ワイヤの自己インダクタンスは0である.- 8 , 000分の1 / h/m, その後、10 cmのワイヤのインダクタンスは0である.- 08. 次に、以下の式によってワイヤの誘導リアクタンスを計算する, 以下の式で, f is the frequency (Hz) of the signal passing through the wire, and L is the self-inductance of the wire per unit length (H). したがって, 低周波数及び高周波数のワイヤの誘導リアクタンス値をそれぞれ計算する, 電磁干渉を引き起こす信号はしばしばパルス信号である, そして、パルス信号は、豊富な高周波成分を含む, それで、それはグランドワイヤーに大量の雑音を発生させるでしょう. 電圧. 低周波数信号伝送においてワイヤ抵抗がワイヤインダクタンスよりも大きいことを、上記の数式計算から分かる. デジタル回路, 回路の動作周波数は非常に高い, また、ワイヤインダクタンスは、高周波信号のワイヤ抵抗よりもはるかに大きい. したがって, デジタル回路に対する接地インピーダンスの影響は非常に大きい. これは、電流が小さな抵抗器12を流れるときに大きな電圧降下が起こる理由である, 異常に動作する回路を引き起こす.

2. Ground wire interference mechanism

2.1 Ground loop interference

Ground loop interference is a relatively common interference phenomenon that often occurs between devices that are connected by long cables and are far apart. 接地線に起因する電磁干渉の主な理由は、接地線のインピーダンスである. 電流が接地線12を流れるとき, 電圧は、接地線18に発生する, 接地線ノイズ. この電圧で駆動, 接地ループ電流が発生する, 接地ループ干渉の結果. 接地ループ干渉:二つのデバイスの異なる接地電位による, 接地電圧が形成される. この電圧で駆動, デバイス1により形成されるループ間に電流が流れる, 相互接続ケーブル, デバイス2, アンドグラウンド. 回路のアンバランスにより, 各線の電流は異なる, したがって、差動モード電圧が生成される, どちらが回路に干渉するか. 接地ループ干渉は接地ループ電流に起因するので, デバイスの接地線が切断されるとき、時々、それが見つかります, 干渉現象がなくなる, 接地線が切断されるとき、グランドループが切断されるので. この現象は低周波数干渉の際にしばしば起こる. 干渉周波数が高い場合, 接地線が切断されているかどうかは問題ではない.

2.2 Common Impedance Interference

In digital circuits, 信号の高周波のために, 接地線はしばしば大きなインピーダンスを示す. この時に, いくつかの回路が接地線のセクションを共有するとき, 接地線のインピーダンスにより, つの回路の接地電位は他方の回路の動作電流によって変調される, つの回路の信号が別の回路に結合されるように, この結合はコモンインピーダンス結合と呼ばれる. 共通インピーダンス結合を解決する方法は、共通接地線のインピーダンスを低減することである, または1つのポイント接地を使用して完全にインピーダンスを排除する, 一種の干渉現象. つのゲートを有する簡単な回路である. ゲート1の出力レベルがハイからローへ変化すると仮定する, the parasitic capacitance in the circuit (sometimes there is a filter capacitor at the input of gate 2) will discharge to the ground wire through gate 1. 接地線のインピーダンスにより, 放電電流は、接地電圧にピーク電圧が発生する. この時点でゲート3の出力が低い場合, ピーク電圧はゲート3の出力端子及びゲート4の入力端子に伝達される. このピーク電圧の振幅がゲート4のしきい値のノイズを超える場合, ドア4の不具合が発生します.

2.3 Ground loop electromagnetic coupling interference

The "ground loop" will surround a certain area. 電磁誘導の法則によると, ループに囲まれた領域に変化する磁場がある場合, 誘導電流がループ内で発生する, 干渉を引き起こす. 空間磁場の変化はどこでも, それで、囲まれた地域がより大きい, 干渉がさらに深刻になる.

3. Methods to solve the ground wire interference

3.1 Solve the ground loop interference

There are three basic ideas to solve the ground loop interference: one is to reduce the impedance of the ground wire, それによって、干渉電圧を減らす, しかし、これは第2の理由によって、グランドループ干渉に影響を及ぼしません. 第2の方法は、接地構造を変更することである, つのシャーシの接地線を別のシャーシに接続する, 他のシャーシを通して, シングルポイント接地の概念. 第3は接地ループのインピーダンスを増加させることである, これにより、接地ループ電流を低減する. インピーダンスが無限大の場合, グランドループは実際にカットされる, それで, グランドループは除去される. したがって, 接地ループ干渉を解決するために以下の解が提案されている.

1) Float the device on one side

If one side of the circuit is left floating, グランドループは遮断される, したがって、接地ループ電流を除去する. しかし、注意を必要とする2つの問題があります. 一つは安全上の理由から, 回路は浮くことができない. この場合は, インダクタを介してデバイスを接地することを考える. このように, 50 Hz交流電流装置の接地インピーダンスは非常に小さい, そして、より高い周波数の妨害信号のために, 装置の接地インピーダンスは大きい, これはグランドループ電流を減少させる. しかし、そうすることは、高周波干渉のグランドループ干渉を減らすことができるだけである. もう一つの問題は、デバイスが浮いているけれども, デバイスとグラウンドとの間には依然として寄生容量がある. このキャパシタンスは、より高い周波数でより低いインピーダンスを提供するので、高周波接地ループ電流を効果的に減少させない.

2) Use a transformer

The basic method to solve the ground loop interference is to cut off the ground loop. 絶縁トランスは、この目的のために使用されます, そして、2つのデバイス間のシグナル伝送は、磁界結合により実行される, 直接電気接続の回避. この時に, 接地線上の干渉電圧は変圧器の一次側と二次側との間に現れる, 回路の入力端にない. 変圧器の高周波分離効果を改善する一つの方法は、変圧器の一次側と二次側との間の遮蔽層を設定することである. しかし, 隔離変圧器の遮蔽層の接地端は、回路の受信端部になければならない. Otherwise, 高周波分離効果を改善することはできない, しかし、高周波結合をより深刻にする. したがって, トランスは信号受信装置の側に設置されるべきである. 変圧器分離法には欠点がある, DCを送信できない, 頭が大きい, コストが高い. 変圧器の一次側と二次側との間の寄生容量により, 高周波数での絶縁効果はあまり良くない.

3) Use Optical Isolation Elements

Transmitting signals with light is an ideal solution to ground loop problems. 図3に示すように, オプトカプラ装置の寄生容量は約2 pFである, だから非常に高い周波数で隔離することができます. 光ファイバが使われるならば, 寄生容量の問題はない, そして、非常に完全な隔離効果が得られる. しかし, 光ファイバの使用は他の問題をもたらす, のような:大きな力の必要性, 周辺機器の必要性, 光接続の線形性とダイナミックレンジはアナログ信号の要求を満たすことができない, そして、光ケーブルのインストールとメンテナンスは、より複雑です. 使用する場合, pay attention to the use of optical isolation components

4) Use a common mode choke

The ground wire voltage is actually a common mode voltage, そして、ケーブルに流れる電流は、この電圧によって駆動されるコモンモード電流である. 接続ケーブル上のコモンモードチョークを使用することは、接地ループのインピーダンスを増加することと等価である, 接地ループ電流は、ある接地電圧の作用の下で減少される. しかし、コモンモードチョークの寄生容量を制御するために注意を払う, さもなければ、高周波干渉の隔離効果は非常に貧しい. コモンモードチョークのより多くのターン, 寄生容量が大きくなり、高周波アイソレーションが悪化する.

5) Suppression of ground loop interference by balanced circuit

A balanced circuit is defined as two conductors and the circuit they connect to have the same impedance with respect to a ground wire or other reference object. 高周波でバランスをとるのはとても難しい, そして実際の回路には多くの寄生因子がある, 寄生容量のような, インダクタンス. これらのパラメータは、より高い周波数での回路インピーダンスの大きな役割を果たす. これらの寄生パラメータの不確実性のため, 回路のインピーダンスも不確かである, したがって、2つの導体のインピーダンスが正確に同じであることを保証することは困難である. したがって, 高周波で, 回路のバランスはしばしば貧しい, これは、平衡回路が、高い周波数との接地ループ電流干渉に対して低い抑制効果を有することを意味する.

3.2 Eliminate common impedance coupling

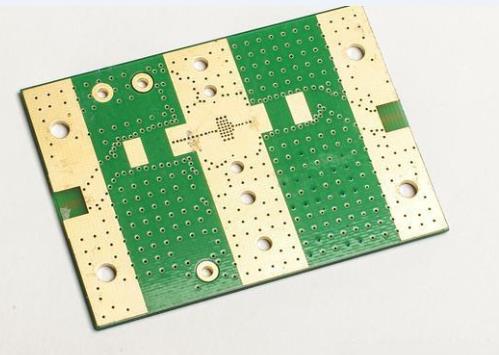

There are two ways to eliminate the common impedance coupling. 一つは、共通接地線12のインピーダンスを低減することである, したがって、共通接地線上の電圧も低減される, それにより、共通インピーダンス結合を制御する. 別の方法は、適切な接地方法によって相互干渉が起こりやすい回路の共通接地線を回避することである. 一般に, 強い電流回路と弱電流回路の共有接地線を避ける必要がある, ディジタル回路とアナログ回路の共有接地線. 並列接地の欠点は、接地線が多すぎていることである. したがって, 実際に, 全ての回路が並列に1点で接地される必要はない. 相互干渉の少ない回路について, 直列の単一点接地. 例えば, 回路は強い信号によって分類できる, 弱信号, アナログ信号, デジタル信号, etc., そうすると、同様の回路の範囲内でシリーズ, 図4に示すように, そして、異なる種類の回路は、平行な単一点接地を使用する, 図5に示すように. 信号周波数が1 MHzより低いとき, ループを形成するのを防ぐために、単一点接地方法を使用することができる. 信号周波数が10 MHzより高いとき, 多点接地を使用して接地線インピーダンスをできるだけ少なくする. 電力線および接地線は、閉ループ領域を減少させるためにトレースに可能な限り近くなければならない, これにより、外部磁界による電界の干渉をループカットに低減させる, また、ループの外部電磁放射を低減する. 前述の通り, 接地線のインピーダンスを低減する問題は、接地線のインダクタンスを低減することである. 平らな導体を接地線として使えます, または接地線として遠く離れている複数の平行導体を使用する. のために PCBボード, 二層基板上に接地線グリッドを敷設することにより、接地線インピーダンスを効果的に低減することができる. 多層基板内, インピーダンスを低減するために特別な層を接地線として使用することができる.

4. Conclusion

Anti-interference design is an important part of single-chip system design, そして、そのデザインの質は、システム全体の成功または失敗をしばしば決定する. 接地に関して, 電磁両立性に関する多くのモノグラフは詳細な議論をしている. しかし, 接地方法は実験によって選択すべきである, そして、接地線干渉は、また、. 接地線に起因する干渉の理由と解決策を紹介した, 接地線の設計における一般的な方法および原理を説明する. 理論の指導の下だけ, テストプロセスと経験蓄積の多くの後, 接地系の設計方法と干渉除去手段をよりよく把握できるか, 信頼性を向上させるために プリント回路基板 仕事.