今日、単層用超低価格ハイブリッドチューナテレビとビデオコンバーターボックスアプリケーションのデザインとほとんどのチューナーは、従来の単一の変換MOPLL概念を使います。そのようなチューナはアナログおよびデジタルTV信号の両方を処理できる。そのようなチューナを設計するときに考慮する主要な要因は、低コストを含む、低消費電力、小さいサイズ、外部コンポーネントの選択だ。この単一チップULCチューナは、RFおよびIF回路を集積し、5 Vまたは3 Vで動作することができる。34%低い消費電力で3Vデザインは単層を使用する。これによりシステムコストがさらに低下する。DVB - Tのような混合信号を扱うことができます。パル/セム、東大物性研/NTSC・ATSC/NTSCによって、ほぼすべての地域標準をサポートすることができます。チューナーは実際にはRFチューナー、またIFモジュールを含んでいるので、RF入力信号は、単純なハイパスフィルタによって分離され、IFおよび民生バンド(CB)ノッチフィルタの組み合わせに加えられる。周波数帯スイッチング用PINダイオードの代わりに、この設計は、周波数帯域切替用の非常に単純な三重回路を使用する。アンテナインピーダンスは、高いインダクタンス結合回路18を介して同調入力回路に変換される。BG5120 KデュアルMOSFETは、両方のVHFバンドだ。次の同調バンドパスフィルタ回路、隣接チャネルとビデオ周波数のような不要な信号のチャネル選択と抑圧が行われる。バンドパスフィルタの前段トラッキングノッチフィルタおよび容量性画像周波数補償回路は、画像周波数を抑えるために特別に使用される。

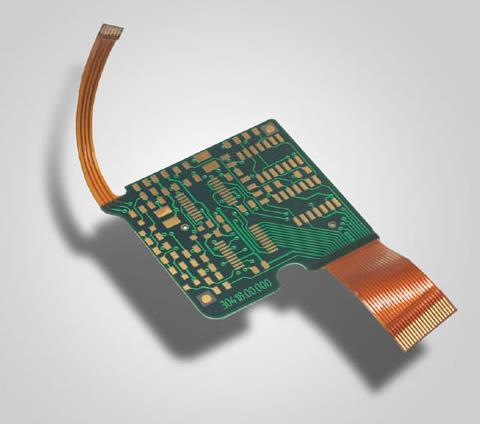

TAA6039 - 2は、3つのミキサー、3つの発振器、1台のSAWドライバーと増幅器のようなすべての必須の能動構成要素を含む完全なトライバンドチューナーICです。完全なPLL機能は、バンド・スイッチングのための4つのPNPポートと1つのNPNポートと内部のチューナーAGCとしての広帯域AGC検出器を含みます。ループフィルタ、4プログラマブルチャージポンプ電流回路、平衡水晶発振器および電圧制御発振器と組み合わせることで、この半ニムは、すべてのデジタル装置に適した位相雑音性能を実現する。TAA 6039−2の平衡IF出力信号は、次のIF回路で直接SAWフィルタを駆動することができる。そして、SAWによって出力された信号は、利得制御オンチップ増幅器によってさらに増幅され、その後の復調器で直接増幅された出力信号を使用することができる。RFのIFへの変換もチップ内部で行われます。この半nimの消費電力は、+5 vの電源電圧で130 ma以下であり、消費電力は650 mw以下である。+3.3 V電源を使用する場合、トータルパワーは429 MWである。電力消費におけるこの重要な節約は、携帯型又はハンドヘルド機器にとって大きな利点である。単層pcbを用いたulcチューナの設計は、顧客に広く受け入れられている。競争的TVチューナー市場では、どんなコスト改善でもさらに生産コストを減らすことができました。したがって、単層PCBボードと2層PCBボードとの間の任意のコスト差は、チューナの全体的なBOM(材料の材料)にとって非常に重要である。この半分のnimデザインは、厚さ1.6 mmの片面FR 4 PCBを使用します。

PALなどの標準テレビ信号の混合受信において/DVB - T、NTSC/ATSC、NTSC/東大物性研などのようなこのリファレンスデザインは単層で開発されたPCBボードパフォーマンスが良い。それは、T - DMBを扱うことができます。ダブ、DMB - TH、オープンケーブル及びその他の規格はこのデザインで、PLLループフィルタとポストフィルタ構成を使用する必要がある。基準周波数排除比は異なるループフィルタとそのポストフィルタの構成に依存する。ループフィルタは、166の2つの基準周波数をカバーするように変更することができるが、67 kHzと62.混合モード5 kHzの位相雑音の性能の間には常にトレードオフがある。基準周波数除去とPLLロック時間だ。したがって、デザイナーが基準周波数を選択することを強く推奨します。または対応するループフィルタとポストフィルタ構成を適用する前に、166.67 KHzまたはその両方だ。測定結果は単層 PCBボードチューナの設計は、60 dBまたはそれ以上の基準受信周波数除去性能を達成することができる。アナログ受信機の厳しい要件を満たすのに十分である。

リファレンスデザインを開発する際の課題の一つは、チップのVQFNパッケージをPCB上に配置する方法である。単層PCB上の接続と接地は接地柔軟性を低減する。RF設計において接地は非常に重要である。チューナデザイナーの挑戦. 地面に影響を受けるいくつかの主要な電気パラメータは、以下を含む。水晶から生じる偽信号の除去、PLL参照周波数とDC/また、ULCチューナに内蔵されたDCコンバータだ。この例の設計は、DC-DC周波数スプリアス除去の約52dBとVCO基準周波数スプリアス除去の60 dBを達成する。VQFNパッケージと単一層によってもたらされる別の問題だ。ICの放熱性、熱性能を高める。ICの裏面は参照設計で露出している。そうすることは熱性能を向上させることができる。チューナーのフレームを通して、チップは3Vで働くこともできます。3 Vの消費電力をさらに減らすだけではない。発熱を減らす。日常のマルチメディア応用におけるRFチューナエレクトロニクスの需要の増大はチューナ形状因子を低減するためのメーカーの要求を推進する。消費電力、コストについて、この記事で発表されたULCチューナーデザインは、コスト間のバランスを見つける試みです。パフォーマンス、消費電力、チューナのコンポーネントとしてTUA 6039 - 2を使用することは、エネルギー効率の高い3で高性能ハイブリッドチューナーを可能にします。ここに提示されたULCチューナーリファレンスデザインは、製品設計リスクを大幅に低減し、パフォーマンスと品質を犠牲にすることなく、市場に時間を短縮する。 PCBボード.

(株)iPCBはPCB&PCBAの設計、製造販売及びこれらの付随業務の電子相関事業を手掛けています。弊社の詳細はリンク:https://www.ipcb.jp/ 或いはhttps://www.ipcb.com/jp をご覧ください。