高速PCBボード相互接続設計技術には、テスト、シミュレーション、およびさまざまな関連規格が含まれており、テストはさまざまなシミュレーション分析結果を検証する方法と手段である。最も重要な試験方法と手段は相互接続設計分析を保証する必要条件である。従来の信号波形試験では、Pigtailによる不要なノイズの導入を回避するために、プローブリードの長さが主に注目されていた。本文は主に相互接続テスト技術の新しい応用と発展を論述した。近年、信号レートの向上に伴い、被験者に重大な変化が生じている。信号波形をテストするためにオシロスコープを使用する従来の方法に限定されない。電源接地ノイズ、同期スイッチングノイズ(SSN)、ジッタ(jitter)は相互接続設計エンジニアの関心の焦点となりつつあり、無線周波数分野のいくつかの機器は相互接続設計に応用されている。相互接続設計で一般的に使用される試験器具には、スペクトル分析器、ネットワーク分析器、オシロスコープ、およびこれらの器具に使用される様々なプローブと固定装置が含まれており、これらの器具は成長する信号速度に対応するために顕著な変化を遂げている。本文はこれらの試験器具をツールとして、主に以下のいくつかの方面から近年の相互接続設計試験技術の発展を紹介した:

1)試験の校正方法

2)受動デバイスのモデリング方法

3)電源完全性テスト

4)クロック信号のジッタ試験方法

3つの一般的な試験機器の中で、ネットワークアナライザの校正方法は厳格で、次にスペクトルアナライザであり、オシロスコープの校正方法は簡単である。そこで、ここでは主にネットワークアナライザのキャリブレーション方法について議論します。ネットワークアナライザには、Thru、TRL、SOLTの3つの一般的なキャリブレーション方法があります。Thruの本質は正規化である。キャリブレーション中、ネットワークアナライザは治具の試験結果を記録する(S 21 _ C)。実際の試験では、試験結果(S 21 _ M)とS 21 _ Cを直接除算してDUTの試験結果を得る(S 21 _ A)。Thruキャリブレーションは、試験治具中の不整合及び空間中の電磁結合による反射を無視するため、そのキャリブレーション精度を無視する。このキャリブレーション方法は、S 21のみをテストし、テスト精度を要求しない場合に使用することができる。PCBボードなどの非同軸構造では、トレース、ビア、コネクタなどの特性をテストする必要がある場合がある。この場合、テスト機器ベンダーは標準的な校正部品を提供しておらず、テストスタッフはテスト校正ポートで開路、短絡、整合負荷などの校正部品を作成するのが難しいため、従来のSOLT校正を行うことができない。TRLキャリブレーションを使用する利点は、標準キャリブレーション部品を必要とせず、テストキャリブレーションポートを必要な位置に拡張できることです。現在、TRLキャリブレーションはPCBボード構造試験に広く応用されている。SOLTは一般的に標準的なキャリブレーション方法と考えられている。キャリブレーションモデルには合計12個のキャリブレーション誤差パラメータがあり、短絡、開放、負荷、貫通を用いて各種誤差をキャリブレーションし、計算する。試験機器供給業者は通常同軸較正部品しか提供していないため、SOLT較正方法は非同軸構造には使用できない。以上の3つのキャリブレーション方法は、各誤差パラメータが信号フローチャートに対応するパラメータを持つ信号フローチャートによって詳細に分析することができる。信号フローチャートを通じて、様々な較正方法の誤差感度を明確に知ることができ、それによって実際の試験の誤差範囲を知ることができる。ここで指摘する点は、標準的なSOLTキャリブレーション方法であっても、キャリブレーションモデルにおける5つの誤差パラメータが無視されていることである。通常、この5つの誤差パラメータはキャリブレーション精度に影響しません。しかし、使用中にキャリブレーション治具の設計に注意しないと、キャリブレーションできない現象が発生します。スペクトルアナライザはキャリブレーションのための標準ソースを提供する。キャリブレーション中は、内部標準ソースをテスト治具を介して入力ポートに接続するだけです。キャリブレーションには約10分かかります。オシロスコープの較正はさらに簡単である。プローブを内部標準ソースに接続して確認します。較正には約1分かかります。

受動デバイスのテストとモデリング

信号レートが増加するにつれて、受動デバイスの信号チェーンにおける役割はますます重要になってきている。システム性能シミュレーション解析の精度は、受動デバイスのモデル精度に依存することが多い。したがって、受動部品のテストとモデリングは、さまざまなデバイスベンダーの相互接続設計の重要な構成要素となりつつあります。一般的に使用される受動デバイスは次のとおりです。

1)コネクタ

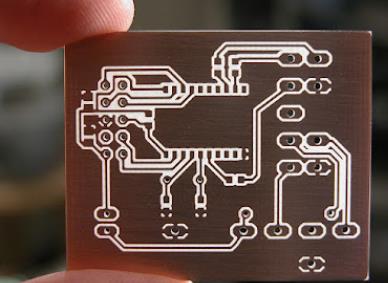

2)PCBボードトレースとビア

3)コンデンサ

4)インダクタンス(磁気ビーズ)

高速信号完全性設計では、コネクタが信号リンクに与える影響。一般的に使用される高速コネクタについては、通常、TRLキャリブレーション方法に基づいてキャリブレーション治具を作成し、コネクタをテストしてモデリングしてシミュレーション分析を行うことができます。PCBトレースとビアのテストモデリング方法はコネクタと類似している。TRL較正はまた、テストポートを必要な位置に移動し、テストモデリングを実行するために使用されます。

単板電源インピーダンス特性表

容量モデルは信号完全性解析に応用されており、より重要なのは電力完全性解析の面である。業界でよく使われている容量モデリング機器にはインピーダンスアナライザとネットワークアナライザがあり、それぞれ異なる周波数帯に適している。インピーダンスアナライザは低周波帯に適し、ネットワークアナライザは高周波帯に適している。実際のテストでネットワークアナライザを使用して電力整合性テストを行う場合は、モデル化とアプリケーションの整合性を確保するために、容量モデル化された帯域全体にネットワークアナライザを使用することをお勧めします。コンデンサのインピーダンスが低いため、ネットワークアナライザを使用したモデリングでは並列接続がよく使用されます。現在、業界の容量モデリングで解決されていない問題は、治具と容量の相互結合をどのように解消するかであり、治具がモデリング結果に与える影響を減らすことができる。従来の電源設計では、ノイズ干渉を低減するために、インダクタ(磁気ビーズ)を使用して電源を遮断することが一般的であった。実際の設計では、絶縁インダクタンス(磁気ビーズ)はしばしば除去され、逆に電源のノイズが低減される。これは、インダクタ(磁気ビーズ)と他のフィルタ部材との共振によるものである。これを回避するためには、共振を回避するためにインダクタンス(磁気ビーズ)をモデリングし、シミュレーションする必要があります。業界で一般的に使用されているインダクタンス(磁気ビーズ)モデリング方法もネットワークアナライザを使用しています。具体的な方法は容量モデリング方法と類似している。異なる点は、インダクタンス(磁気ビーズ)モデリング方法が直列モードであり、容量モデリング方法が並列モードであることである。上述の受動デバイスのモデリングは、主に信号完全性と電力完全性に用いられる。近年、EMIのシミュレーション分析は徐々に発展しており、EMI受動デバイスのテストモデリングは徐々に相互接続設計の重点となっている。図1はコンデンサのインピーダンス曲線を示している。

電源整合性テスト

チップ電力の増加と動作電圧の低下に伴い、電源のノイズは徐々に相互接続設計において注目の対象となっている。試験対象から見ると、電力完全性試験は2つのステップ、すなわち電力システム特性試験と電力接地ノイズ試験に分けることができる。前者はシステム電源の部分性能のテスト(受動テスト)であり、後者はシステム動作時の電源接地ノイズの直接テスト(能動テスト)であり、同期スイッチングノイズも電源接地ノイズに分類できる。電力システムの性能をテストする際には、通常、ネットワークアナライザが使用され、テスト対象は電力システムの自己インピーダンスと伝送インピーダンスである。通常の場合、電力系統のインピーダンスはネットワークアナライザ系統のインピーダンス(50オーム)よりはるかに小さいため、試験過程で直通校正を行うだけで、式S 21=Z/25を用いて電力系統の抵抗を得ることができる。スペクトルアナライザおよびオシロスコープは、電源の接地ノイズをテストするために使用することができる。スペクトルアナライザの入力ポートは直流コンポーネントに接続できません。したがって、電源の接地ノイズをテストする場合は、テスト治具に直列にDC Blockingを接続する必要があります。スペクトルアナライザの入力インピーダンスは50オームであり、電源接地ネットワークのインピーダンスは通常ミリオームレベルにあるため、試験治具は測定システムに影響しない。上記の方法は単板上で電源接地ノイズをテストすることであり、チップ中の電源接地ノイズこそチップの動作に影響を与える要素である。この場合、同期スイッチングノイズテストを用いてチップ中の電源接地ノイズを決定する必要がある。チップにはN個のIOポートがあり、一方は静的なままで、もう一方のN-1は同時に反転し、静的ネットワーク上の信号波形、すなわち同期スイッチングノイズをテストすると仮定する。同期スイッチングノイズは、電源接地ノイズとパッケージ内の異なる信号との間のクロストークを含む。この両者を完全に区別する方法はまだない。

オシロスコープ入力インピーダンスは設定によって変化する

一部のハイエンド製品では、ジグルが製品の性能に影響を与える重要な指標になりつつある。ここでは、クロック信号のジッタをテストし、問題を解決するためにスペクトル分析器を使用する方法を簡単に紹介します。データ信号のジッタ試験は当分含まれていない。ほとんどのシステムでは、クロックは結晶発振器または位相同期ループによって生成される。クロック信号のジッタテストは比較的簡単で、ハイエンドのテスト機器は必要ありません。汎用スペクトルアナライザを使用して問題を特定することができます。理想的なクロック信号のスペクトルはクリーンな離散スペクトルであり、その成分はクロック周波数の倍数にすぎない。クロック信号にジッタが存在する場合、サイドローブはこれらの乗算器の近くに現れ、ジッタの大きさはこれらのサイドローブの電力に比例する。スペクトルアナライザを使用してクロックジッタをテストする具体的な方法は、クロック信号チェーン上に任意のテスト可能な点を見つけ、DC Blockingを通じてその点の信号をスペクトルアナライザに接続し、テスト結果を観察することである。試験治具は線形系であるため、新たなスペクトル成分を生成する心配はない。上述したように、クロックはすべて結晶発振器または位相同期ループによって生成される。この場合、クロックジッタを導入する重要な理由の1つは、結晶発振器または位相同期リングの電源ノイズである。上述の方法を用いて、得られた結晶発振器または位相同期リングの電源ノイズを試験し、クロックスペクトル中のサイドローブと比較して、基本的にクロックジッタの原因を決定することができる。この問題を解決する方法は、クロックスペクトルのサイドローブに基づいて位相同期リング結晶発振器のフィルタ回路を再設計することである。一般的に、これらの問題はフィルタキャパシタを合理的に選択することによって解決することができる。

本文は現在の相互接続設計分野の試験対象と試験方法を簡単に紹介した。信号速度が増加するにつれて、電源対地上ノイズ、受動デバイスモデリング、ジッタなどの新しいテスト内容が発生しています。著者は自分の仕事の経験に基づいて、これらの新しいテスト内容に対してテスト方法を提案した。従来の信号波形試験では、尾びれがノイズに結合されないように、接地線の長さを減らし、試験精度を低下させることが主に考慮されてきた。将来の相互接続設計では、信号動作周波数の増加により、動作の重点はチップパッケージに移り、関連するテストとモデリング技術はPCBボードの動作の重点となる。