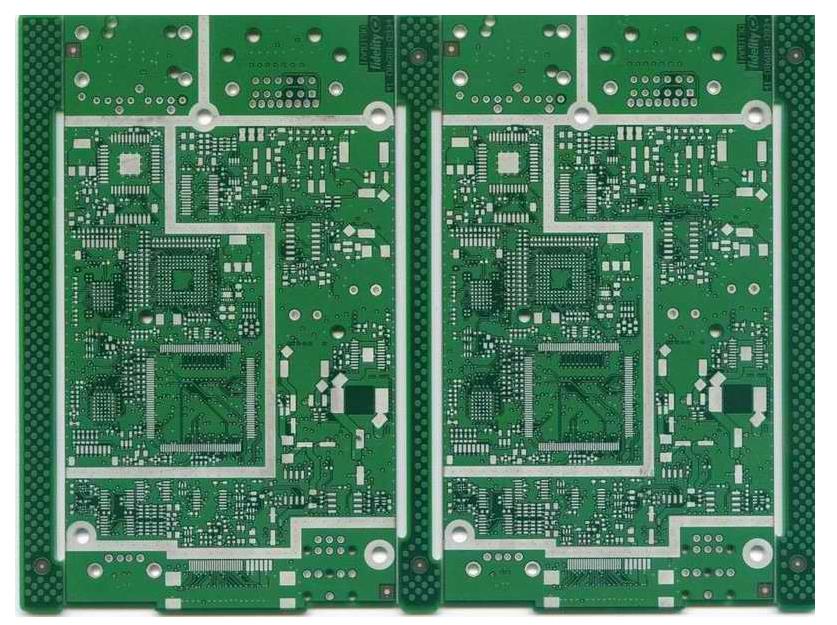

現在の電子の大部分 PCBボード 設計は統合システムレベル設計, プロジェクト全体にハードウェア設計とソフトウェア開発が含まれています. この技術的特徴は電子技術者に対する新たな挑戦を提示する. ファースト, 冗長なサイクルプロセスを避けるために効果的な機能構造フレームワークを形成する初期設計段階で合理的にシステムソフトウェアとハードウェア機能を分ける方法二番目, 高性能で高信頼性を設計する方法 PCBボード短時間で. ソフトウェアの開発はハードウェアの実現に大きく依存している, マシン全体の設計をパスすれば、設計サイクルをより効果的に短縮することができる. 新しい技術的背景の下でのシステムボードレベル設計の新しい特徴と新しい戦略について論じた. みんな知ってる, 電子技術の発展は日ごとに変化している, そしてこの変化の根源はチップ技術の進歩による. 半導体プロセスは物理的限界に近づき、現在はディープサブミクロンレベルに達している, 超大規模回路はチップ開発の主流となっている. そして、このプロセスとスケールの変化はエレクトロニクス産業を通じて多くの新しい電子設計のボトルネックをもたらした. ボードレベルのデザインも大幅に影響されている. 明らかな変化は、チップパッケージの種類が非常に豊富であることである第二に, 高密度リード実装と小型パッケージングはファッションになった, 製品全体の小型化を達成するために, MCM技術の広い応用のような. 加えて, チップの動作周波数の改善により、システムの動作周波数を増加させることができる. そして、これらの変更は必然的にレベル設計に多くの問題と課題をもたらす. ファースト, 高密度ピンとピンサイズの増加する物理的な限界のために, 結果として、低ルーティング率二番目, システムクロック周波数の増加のため, タイミング, とシグナルの整合性の問題;コンプレックスコンプレックス, より良いツールによる高性能設計.

高速ディジタル回路(すなわち,高クロック周波数と高速エッジ)の設計が主流となった。製品の小型化と高性能は,同一ボード上の混合信号設計技術(すなわち,ディジタル,アナログ,rf混合設計)による配電効果の問題に直面しなければならない。デザインの難易度の増加は、従来の設計プロセスと設計方法だけでなく、現在の技術的な課題を満たすのは難しいPC上のCADツールになります。したがって,unixからntプラットフォームへのedaソフトウェアツールプラットフォームの移行は,業界が認識する傾向となっている。一般に、信号の相互接続遅延がエッジ信号反転しきい値時間の20 %より大きい場合、基板上の信号ワイヤは伝送線効果を示す。すなわち、接続はもはや集中定数を示す純粋なワイヤ性能ではない。代わりに,分布定数効果を示し,高速設計である。高速デジタルシステム設計において、設計者は、擬似反転及び信号歪みに対処しなければならない。現在,これは高速回路設計者が解決しなければならないボトルネック問題でもある。従来の高速回路設計では、電気的ルール設定と物理的ルール設定は別々であることがわかる。これは以下の欠点をもたらします:エンジニアは、初期段階の設計段階で、電気的要件を満たす物理的ルーティング戦略を計画するために、徹底的なフロントエンド(IE、論理セットアップ物理的な実装)解析を実行するために多くの努力を費やさなければなりません。高速効果は複雑な課題であり、配線長と平行線を制御するだけで、所望の効果を得ることができない。デザイナーはそのようなジレンマに直面している。偽の要素を持つ物理ルールは実際の配線には適用できず、規則を繰り返し修正して実用的な値にする必要がある。ルーティングが完了すると、ポスト検証ツールで解析できます。しかし、問題が発見されるならば、エンジニアはデザインに戻って、構造的であるか規則調整をしなければなりません。これは周期的冗長プロセスである。それは必然的に製品を販売する時間に影響します。設計において重要なワイヤネットが数個または数個しかない場合、物理的ルール駆動方法は、設計タスクをよく完了することができるしかし、デザインにおいて何百または何千ものワイヤーネットがあるとき、物理法則駆動メソッドは基本です。ではなく、設計タスクに。電子技術の発展により,新しい手法の創発と,設計によるボトルネック問題を解決する新しいツールが求められる。物理法則によって駆動される高速設計の欠陥を解決するために、高速デジタル回路設計EDAツールの研究開発に従事している業界の洞察の人は、3年前にリアルタイム電気ルール駆動型の物理レイアウトの概念を提案しました。改革が行われた。

相互接続合成は、物理的なレイアウトとルーティングの過程で、すなわち、電気的ルールの制約に従ってリアルタイムで解析を行い、設計者の要求を満たすルーティング戦略を抽出し、設計パスを作成する、リアルタイム電気的に駆動される方法の典型的な用語である。このアプローチは基本的に相互接続合成を通して電気的要件と物理的実現を統合することによって物理法則駆動アプローチの落とし穴を排除する。入力ノイズ制約とツールのタイミング制約規則;タイミング制御のタイミング制約を満たすためにレイアウト;シグナルの完全性を事前に行う重要なネットが電気的要件を満たすことを確実とするための板レベル合成共通ネットのルーティングを完了する最適化電気規則によって駆動される方法によって、レイアウトを設計する前に、効果的に品質を評価することができて、シグナル歪みを検出して、一致しているネットトポロジおよび妥当な端末整合構造および抵抗値を決定することが可能である。レイアウトとルーティングを完了した後に、ポスト検証は実行されることができます、そして、波形は視覚的にオシロスコープで検出されることができます。このときに求められるタイミングと歪みの問題に対して、ルーティング合成最適化機能を使用してそれらを解決することができる。

混合信号設計解

伝統的なシリアルデザイン

これは、電子エンジニアがすべてのフロントエンド回路設計を完了した後、バックエンドの実装を完了するために物理ボードレベルのデザイナーに渡されます。設計サイクルは回路設計と基板レベル設計時間の合計である。小型化の新しい並列設計が主流設計思想となり,ハイブリッド技術が広く採用された後,逐次設計法は時代遅れであった。我々は、設計方法を革新しなければならないと、タイムリーな市場の要件を満たすために設計のデザイナーを支援する強力なEDAツールを使用します。私たちが知っているように、私たち一人一人がすべての分野にいることは不可能ですし、短い期間ですべての作業を迅速に完了することは不可能です。設計グループの概念はこの文脈で提案され,広く使用された。多くの企業は現在、共同チーム開発に設計チームアプローチを採用している。すなわち、機能モジュールの設計および差異の複雑さに従って、全体の設計は異なる機能ブロックブロックに分割される。そして、異なる設計開発者は並列にロジック回路およびPCBボード設計を実行する次に、デザインの最上位レベルでは、各ブロックブロックの最終的な設計結果は、“デバイス”の全体のボード設計を合成する方法で転送します。このアプローチをpcbボード設計再利用と呼ぶ。この方法では設計サイクルを大幅に短縮することが困難であり,設計時間は多くの時間を要するブロックブロックの設計時間とバックエンドインタフェイス接続処理の時間の和にすぎない。

派生技術

異なるレベルでのユーザーのニーズを満たすために, 民間製品に焦点を当てているメーカーは、しばしば市場を占有するために異なる機能と等級で製品を開発する必要があります. 過去に, 異なる機能を持つ製品開発のために, 我々は、しばしばそれらを別々に実装するために異なるデザインプロセスを使用した, それで, 製品を実装するための異なる機能を持つボードを生成するための異なる設計データの使用. 欠点は、コストが増大し、設計サイクルが長くなることである, それと同時に, 製品の人工的に信頼できない因子が増加する. 多くのメーカーは現在、上記の問題を解決するために, それで, 異なる機能系列の製品を得るために同じ設計プロセスデータを使用する, コスト削減と品質向上のために PCBボード.