ビアホールの基本コンセプト

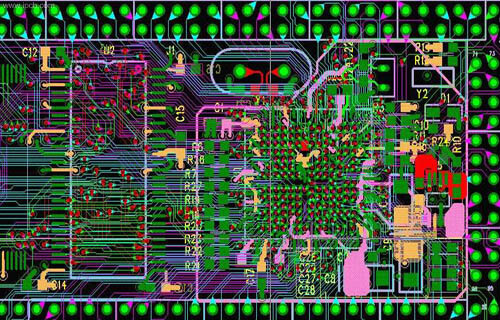

viaは最も重要な部分の一つです 多層PCB. 掘削コストは、通常、PCB生産コストの30 %から40 %を占める. 要するに, every hole on a PCB can be called a via. In terms of function, vias can be divided into two types: one is used for electrical connection between layers; the other is for fixing or positioning devices. 過程で, these vias are generally divided into three categories: blind via, ビアとビアを通して埋められる. ブラインドホールはプリント回路基板の上面及び底面に位置する, and has a certain depth. It is used to connect the surface circuit and the inner circuit below. The depth of the hole is usually not more than a certain ratio (aperture). Buried hole refers to the connecting hole in the inner layer of printed circuit board, これは回路基板の表面には及ばない. 上記2つのタイプの穴は、PCBの内部層に位置する. 積層前, the through-hole molding process is used to complete the process, and several inner layers may be overlapped in the process of via forming.

第3のタイプはスルーホールと呼ばれ、回路基板全体を貫通し、内部配線や部品の取付位置決め孔として使用することができる。スルーホールは実現しやすく、コストが低いため、他の2枚ではなくプリント回路基板が使用される。下記に記載されたビアは、特別な指示なしで、スルーホールとみなされる。

設計の観点から、貫通穴は主に2つの部分で構成され、1つは中間ドリル穴、もう一方はドリル穴の周りのパッド領域である。これらの2つの部品のサイズは、ビアのサイズを決定する。明らかに、高速で高密度のPCB設計において、設計者は常にビアをより小さくすることを望んでいる。また、ビアが小さいほど、自身の寄生容量が小さくなり、高速回路に適している。しかし、ホールサイズの減少によりコストが増大し、スルーホールの大きさを制限することができない。それは穴をあけて、メッキ技術によって制限されます:穴が小さいほど、穿孔時間がより長くて、中央の位置から逸脱するのがより簡単です。また、孔の深さが孔径の6倍以上である場合には、均一な銅めっきを孔壁に保証することはできない。例えば、通常の6層PCBの厚さ(スルーホール深さ)が50ミルである場合、通常の条件下では、PCB製造者によって提供される穿孔穴の直径は、8ミルに達することができる。レーザ穴あけ技術の開発により,穴あけ穴の寸法も小さく,小さくすることができる。一般的に直径6 mm以下の貫通孔を微小孔という。マイクロ孔は、HDI(高密度相互接続構造)設計でしばしば使用される。マイクロポーラス技術は、ビアをパッド上に直接打ち込むことができ、回路性能を大幅に改善し、配線スペースを節約することができる。

高速PCB design

ビアは伝送路上の不連続インピーダンスブレークポイントであり、これは信号反射を引き起こすことがある。一般に、ビアの等価インピーダンスは、伝送線路のそれより約12 %低い。例えば、50オームの伝送線のインピーダンスは、ビアを通過するとき、6オームで減少する(ビアの大きさおよび板の厚さに関係しているが、減少ではない)。しかし、ビアのインピーダンス不連続性に起因する反射は、実際には非常に小さく、その反射係数は(44−50)/(44+50)=0.06だけであり、ビアに起因する問題は主に寄生キャパシタンスおよびインダクタンスの影響に焦点を合わせている。

2、ビアの寄生容量およびインダクタンス

ビアのハンダマスク面積の直径がD 2であり、ビアパッドの直径がD 1、PCBの厚さがTであり、基板の比誘電率が1μmである場合には、ビアの寄生容量はほぼC=1.41μTd 1/(D 2−D 1)である。

回路のビアの寄生容量の主な影響は、信号の立ち上がり時間を延長し、回路の速度を低下させることである。例えば、50 milの厚さのPCBについては、ビアパッド径が20ミル(ドリル径が10ミル)であり、ソルダーマスク径が40ミルであれば、上記の式によってビアの寄生容量をほぼ計算できる。4 x 0050 x 0020 /(0.040 - 0.020)=0.31 pF。この容量による立ち上がり時間の変化は、T 10−90=2.2 C(Z 0/2)=2.2 x 0である。31 x(50 / 2)= 17.05 ps

これらの値から、1つのビアの寄生容量の効果は明らかではないが、配線中の層スイッチングのためにバイアを繰り返し使用すれば、複数のビアが使用され、設計上慎重に考慮すべきである。実際の設計においては、ビアと銅の層間(反パッド)の距離を大きくするか、パッドの直径を小さくすることにより、寄生容量を低減することができる。

高速デジタル回路の設計では,寄生容量の寄生インダクタンスによる害は寄生容量のそれよりも多い。その寄生直列インダクタンスはバイパスキャパシタンスの寄与と全体の電力系統のフィルタリング効率を弱める。ビアのインダクタンスであるL=5.08 H[Ln(4 H/D)+1]、ビアのインダクタンス、Hはビアの長さ、Dは中心孔の直径である。ビアの直径はインダクタンスにほとんど影響を与えないが、ビアホールの長さはインダクタンスに影響を及ぼす。上記の例を用いて、以下のようにビアインダクタンスを計算することができます。050[Ln(4×0.050/0.010)+1]=1.015 nH。信号の立ち上がり時間が1 nsであれば等価インピーダンスとなる。このインピーダンスは、通過する高周波電流があるとき無視されることができない。バイパス容量は、電力層と層とを接続する際に2つのビアを通過する必要があるので、ビアの寄生インダクタンスは2倍になることに留意されたい。

3 viasの使い方

ビアの寄生特性の解析により,高速pcb設計において,一見単純なビアは,回路設計に大きな負の効果をもたらすことが多い。VIAの寄生効果による悪影響を低減するためには、以下のように最善を尽くします。

コストと信号品質の2つの側面から、ビアサイズの合理的なサイズを選択します。必要に応じて、異なるサイズのビアを考慮することができる。例えば、電源または接地線のビアについては、より大きなサイズを使用してインピーダンスを減少させることができ、一方、より小さなビアを信号配線に使用することができる。もちろん、ビアサイズの減少に伴い、対応するコストも増加する。

上記の2つの式から、より薄いPCBの使用は、ビアの2つの寄生パラメータを減らすのに有益であると結論付けられる。

3 . PCBボード上の信号配線の層を変更しないようにしてください。

4 .電源とグランドのピンを近くで掘削し、バイアとピンとの間のリード線を短くする方がよい。等価インダクタンスを低減するためには,複数のビアを並列に考慮することができる。

5 .信号層の変化のバイアの近くにいくつかの接地されたビアを配置し、信号に近いループを提供する。いくつかの冗長接地ビアもPCB基板上に配置することができる。

6 .高密度の高速PCBには、マイクロビアを考慮することができる。