PCB設計エンジニアとして、いくつかの高速知識を身につけることは非常に必要であり、さらに必要である。信号の場合、高速信号は通常、様々なパラレルバスやシリアルバスに存在する。バスとは何かを知っている場合にのみ、その動作速度を知ることができ、PCB配線を開始することができます。

バス台

バスは、2つ以上のデバイス間の通信のための共有物理チャネルである。これは信号線の集合であり、各コンポーネント間で情報を転送するための複数のコンポーネント間の共通接続でもあります。動作モードによっては、バスにはパラレルバスとシリアルバスの2種類があります。

へいれつぼせん

複数のビットのデータを同時に転送することができます。これは、複数の車を並べて走ることができる広い道路のようなもので、双方向と片方向のポイントもあります。

シリアルバス

1台の車だけが許される狭い道のように、データを次々と転送しなければならず、長いデータ列のように見えるため、「シリアル」と呼ばれています。

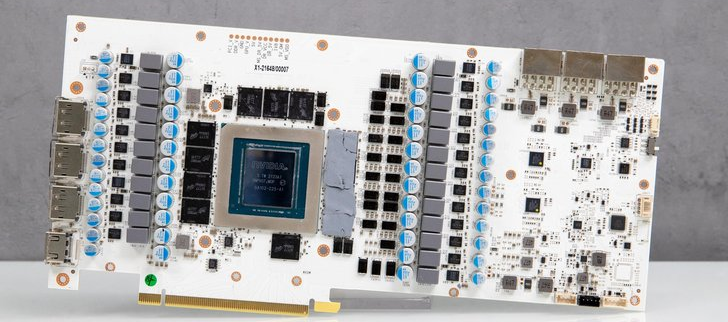

並列転送の最良の例は、メモリチップDDRである。DQSとDQMを加えたデータ線D 0-D 7のセットがあります。このグループの回線は一緒に転送されます。どちらにエラーがあっても、データは正しく転送されません。再送信のみ。したがって、データケーブルの各ケーブルは等しい長さを持ち、複数回巻き取らなければなりません。

シリアルデータが異なります。データは次から次へと転送され、ビット間には接続されていません。このビットにはエラーがなく、次のビットは転送できません。並列データは、データセット全体が動作しなくなるエラーのセットです。

PCB配線要件

並列バス配線の要件:

(1)バスは内部配線であることが好ましく、バスと他の配線との距離はできるだけ長くすることをお勧めします。

(2)特殊要求のほか、単線設計インピーダンスは50オーム、差分設計インピーダンスは100オームを保証する。

(3)同じグループのバスは同じ配線長を維持し、クロック線と一定のタイミング関係に従うことを提案し、タイミング解析の強力な結果を参照して配線長を制御する。

(4)参照平面の完全性を確保するために、このバスのI/O電源またはGND参照平面にできるだけ近づけることをお勧めします。

(5)立ち上がり時間が1 ns未満のバスは完全な参照平面を必要とし、パーティションを通過することはできない。

(6)下部アドレスバス基準クロック配線要求を提案する。

(7)蛇行巻線の間隔は線路幅の3倍未満であってはならない。

高速PCBシリアルバス配線要件

100 Mbps以上の周波数を有するシリアルバスについては、パラレルバスの汎用クロストーク制御と配線規則に従うほか、配線設計においていくつかの追加要件を考慮する必要がある:

(1)高速PCBシリアルバスは配線損失を考慮し、線幅と回線長を決定する必要がある。

(2)通常の場合、線幅は5 mil以上で、配線はできるだけ短くすることを提案する。

(3)Fanotビアを除く高速シリアルバスは、ピアシングや交換をしてはならない。

(4)シリアルバスにおけるピン挿入速度が3.125 Gbpsを超える場合、不連続インピーダンスによる非放射影響を低減するために、半田付け防止ディスクを最適化しなければならない。

(5)高速シリアルバス配線層を交換する際に、最小ビアスタブを有する配線層を選択することを提案する。コネクタへの信号については、配線空間が限られている場合には、短ビアスタブを有する配線層が送信側に優先的に割り当てられる。

(6)速度が3.125 Gbps以上の場合、信号通過孔のそばに接地孔を掘削し、交流結合コンデンサも溶接防止盤の特殊な処理を行うことを提案する。

(7)高速信号ビアを逆ドリル処理する場合、電流ボトルネックが狭くなった後の電源接地面の電流容量減少とフィルタループインダクタンス増加の影響を考慮する必要がある。

(8)高速信号は平面層の境界線を避け、信号線エッジと境界線エッジ間の水平距離を3 Wに保証する。

(9)2方向の高速信号は交差及び配線してはならない。