間の関係 PCBボード ルーティング長整合と差分対の周波数

トレース長と周波数の正しいマッチングは、トレースに沿って伝搬する信号の帯域幅を考慮に入れるべきである。これは過去数年間の差動シリアルプロトコルの研究の対象であった。USB 4のような規格は広帯域信号完全性指標に特定の要件を置いている。いくつかのサンプル広帯域信号完全性指標は以下の通りです。

積分微分クロストーク

積分差挿入損失

積分差分リターン損失

積分差インピーダンス偏差

「積分」によって,信号整合性の特定の局面が適切な周波数範囲にわたることを意味する。言い換えれば、例えば、差動クロストークをとる場合、シグナリング規格で指定されるように、2つの差分ペア間の差動クロストークをある限度より小さくすることを望む。私たちはなぜこれが長さマッチを一瞬で追跡するために重要である理由を見るでしょう。

散乱

時間領域では、HIとロー状態を交差する差分ペアの2つの端の間の半分の遷移についてのみ注意します。明らかに、ジッターはここで問題を提起します、そこで、それは特定の寛容にあなたの線長を制限します。周波数領域では、以下のソースから分散を考慮する必要があります。

幾何学的分散:これは、相互接続のインピーダンスがどのように異なるかを決定する境界条件および相互接続の幾何学によって引き起こされる。

誘電拡散:これは、PCB基板において起こり、PCB上の相互接続の形状とは無関係である。それは、DK分散と損失を含みます。

粗さ分散:この追加の分散源は、銅粗さモデルの因果性および高周波数での表皮効果に起因する。

繊維編みの分散PCB積層材における繊維編組は相互接続を通して周期的分散変化を生じる

これらの分散源は常に配線中に存在するため、インピーダンス、速度が生じる。

そして、実際のPCB配線の信号完全性の他のすべてのインジケータは、周波数の機能である。dkの実部のばらつきがマイクロストリップ配線のインピーダンスにどのように影響するかを示す例を以下に示す。

速度信号

伝送線理論に精通しているならば、あなたはインピーダンスが信号速度と密接に関連しているということを知っています。PCB配線の信号速度を例にとりましょう。以下の図は粗さと分散を持つ模擬バンドの群速度と位相速度を示した。

銅粗さと誘電分散による試料リボンライン信号の群速度と位相速度

ここで、位相速度は広い周波数範囲にわたって大きく、1 MHzから20 GHzの2倍まで変化することが分かる。位相速度の変化は、異なる周波数成分が相互接続に沿って伝搬する速度であるので、ここで重要なパラメータである。この変化により,実用的な相互接続に対して,pcbトレース長整合と周波数整合がいかに困難になるかを見ることができる。我々は、任意の周波数だけでなく、任意の個々の周波数を説明するいくつかの方法が必要です。

ブロードバンド長マッチングと周波数

長さマッチングの尺度を開発するためには,与えられた信号規格の許容長偏差を考慮する必要がある。今回は偏差tlimと呼ぶ。長さ公差と許容タイミング不整合について以下の式を記述できる。

許容時間的変化による長さの変化。

ここで、関数kは配線上の信号の伝搬定数であり、分散による周波数の関数でもある。“LP NORM”と呼ばれる何かを使用して許容長不一致を扱うために統計的方法を使用することができる。あまりにも深く数学に関与することなく、この測定は、定数とは異なる関数と平均の間のRMSの違いを計算するのと等価であることを知っている。このように、これは特定の目標設計値およびシグナル完全性措置(インピーダンス、インパルス応答減衰/遅延、漏話強度など)間の変動に対処するための理想的な数学的道具となる。

lp‐normを用いて,timmにより定義された幾つかの上限値に基づいて,許容誤差の不一致を書き換えることができる。

許容時間的変化による長さの変化。

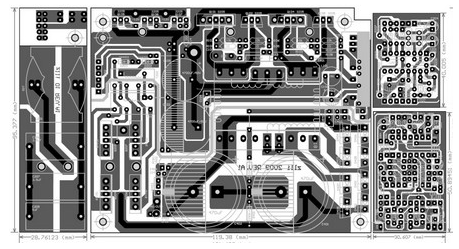

広帯域信号完全性メトリックスを使用してPCBを設計するとき、上記の式は、制約として考慮することができます:伝送線のサイズを決定するとき、これは、差対の端の中、または、の間のどんな2つの線の間の完全な許容長さ偏差に影響を及ぼすかもしれません。高速並列プロトコル.積分は伝送線路の伝搬定数を知る限り計算が容易である。この値は、フィールドソルバーを使用して、標準的な伝送線ジオメトリを持つ解析モデルによって手動で計算することができます。

上記のアナログストリップの位相速度を使用する場合、計算のための数を与えるためには、並列シングルエンド完全孤立トレース間の許容長不整合が2.07 mmであり、許容誤差が許容される場合、タイミング不整合が10 psであることを見出している。10 psに関しては、これは多くの高速デジタル信号のエッジ率の大部分であることに留意されたい。上でシミュレートしたリボン線の場合、これは許容長さ不一致の1.3041 mmに等しい