1.ハウツーとスタイル PCBボード

PCBボードの選択は、会議設計要件と量産とコストのバランスを取らなければならない。設計要件は、電気および機械部品の両方を含む。この材料の問題は、通常、非常に高速なPCBボード(GHzより大きい周波数)を設計するときに重要である。例えば、一般的に使用されるFR−4材料では、数GHzの周波数での誘電損失は、信号減衰に大きな影響を与え、適切でない場合がある。電気に関する限り、誘電率と誘電損失が設計された周波数に適しているかどうかについて注意してください。

2 .高周波妨害を避ける方法

高周波妨害を避けるための基本的な考え方は、いわゆるクロストーク(クロストーク)である高周波信号の電磁界の干渉を最小にすることである。高速信号とアナログ信号との間の距離を増大させることができるか、またはアナログ信号の他に接地ガード/シャントトレースを加えることができる。また、デジタルグラウンドからアナロググランドへのノイズ干渉に注意を払う。

3.高速設計における信号完全性の問題の解決法

信号の完全性は基本的にインピーダンス整合の問題である。インピーダンス整合に影響する要因は、信号源の構造インピーダンス、トレースの特性インピーダンス、負荷端の特性、およびトレースのトポロジを含む。解決策は、終了(終了)し、配線のトポロジを調整することである。

4.差分配線法はどうなっているか

差動対のレイアウトに注意を払う2点がある。一つは、2本のワイヤの長さができるだけ長くなければならないことであり、もう一方は、2つのワイヤ(この距離が差動インピーダンスによって決定される)間の距離が一定に保たれなければならないこと、すなわち並列に保たれることである。つの平行な方法があります、1つは2つのワイヤーが同じ側の側で動くということです、そして、もう一方は2つのワイヤーが上下に2つの隣接した層で動くということです。一般的に、前者はよりサイドバイサイドの実装を有する。

5.一つの出力端子を持つクロック信号線の差動配線の実装方法

差動配線を用いるためには、信号源と受信端の両方が差動信号であることを意味する。したがって、1つの出力端子のみを有するクロック信号に対して差動配線を使用することはできない。

6.受信端での差動線対の間に整合抵抗を付加することができるか。

受信端の差動線路対の間の整合抵抗は通常加算され、その値は差動インピーダンスの値と等しくなければならない。信号品質がよりよくなるこの方法。

7.なぜ、差動対の配線は、最も近い並列になるのか。

差動対の配線方法は、適切に近接して並列にすべきである。いわゆる適切な距離は、距離が微分インピーダンスの値に影響するので、差動対を設計するための重要なパラメータである。並列性の必要性はまた、差動インピーダンスの整合性を維持することである。つの線が突然遠く近くにある場合、差動インピーダンスは矛盾しています。そして、それはシグナル完全性とタイミング遅れに影響を及ぼします。

8.実配線における理論的コンフリクト

基本的には、アナログ/デジタルグランドを分割して分離するのが正しい。なお、信号トレースは、分割された場所(濠)をできるだけ交差させてはならず、電源および信号の戻り電流経路が大きすぎることはない。

水晶発振器はアナログ正帰還発振回路である。安定した発振信号を得るためにはループゲインと位相仕様を満たす必要がある。このアナログ信号の発振仕様は容易に乱される。地面ガード跡が加えられるとしても、干渉を完全に隔離することができないかもしれません。そして、それがあまり遠く離れている場合、グランドプレーン上のノイズはまた、正帰還発振回路に影響を及ぼす。したがって、水晶発振器とチップの間の距離は、できるだけ近くなければならない。

高速配線とEMI要求の間に多くの競合があることは事実である。しかし、基本的な原理は、EMIによって加えられた抵抗、キャパシタンスまたはフェライトビーズが信号のいくつかの電気的特性が仕様を満たすことができないことであるということである。したがって、内部層に行く高速信号のようなEMI問題を解決または低減するためにトレースおよびPCB積層を配置する技術を使用することが最善である。最後に、抵抗コンデンサまたはフェライトビーズ方法は、信号に対する損傷を減らすために用いる。

9 .マニュアル配線と高速信号の自動配線の矛盾の解決法

現在,強い配線ソフトウェアの自動ルータの多くは,巻線方法とビア数を制御するための制約を設定している。様々なeda企業の巻線エンジン機能と制約設定項目は,時々大きく異なる。例えば、蛇行巻線の方法を制御するのに十分な制約があるかどうか、差動ペアのトレース間隔を制御することが可能であるかどうかにかかわらず、これは自動ルーティングのルーティング方法がデザイナーの考えを満たすことができるかどうかに影響します。また、配線を手動で調整することの難しさも、巻き取りエンジンの能力に絶対的に関連している。例えば、トレースの押し付け能力、ビアの押し付け能力、トレースの押圧能力等も、銅コーティング等に適用する。したがって、強力な巻線エンジン能力を持つルータを選ぶことは解決です。

10 .テストクーポンについて。

テストクーポンは、製造されたPCBボードの特性インピーダンスがTDR(Time Domain Reflattometer)により設計要件を満たしているかを測定するために使用される。一般的に、制御するインピーダンスは2つの場合である。したがって、テストクーポン(差動ペアがある場合)の線幅と線間隔は、制御する線と同じであるべきです。最も重要なことは測定中の接地点の位置である。接地リードのインダクタンスを低減するために、TDRプローブの接地場所は通常プローブ先端に非常に近い。したがって、テストクーポン上の信号測定点と接地点との間の距離および方法は、使用されるプローブと一致しなければならない。

11 .高速PCB設計においては、信号層のブランク領域を銅で被覆することができ、多層信号層の銅被覆をどのようにして地上と電源に分配するか。

一般に、ブランク領域の銅めっきはほとんど接地されている。銅が高速信号線の隣に銅を塗布するとき、銅と信号線の間の距離に注意を払うだけである。なぜなら、適用された銅は、トレースの特性インピーダンスを少し減らすからである。また、デュアルストリップラインの構造など、他の層の特性インピーダンスに影響を与えないように注意する。

12 .マイクロストリップラインモデルを使用して、パワープレーン上の信号線の特性インピーダンスを計算することができるか。電源と接地面の間の信号はストリップラインモデルを用いて計算できるか?

はい、特性インピーダンスを計算するとき、パワープレーンおよびグランドプレーンは基準面とみなされなければならない。例えば、4層ボード:トップ層パワー層の接地層の底層。このとき、トップ層の特性インピーダンスモデルは、パワープレーンを基準面とするマイクロストリップラインモデルである。

13 .大量生産のテスト要件を満たすために、通常の状況下で高密度プリントボード上のソフトウェアによって自動的にテストポイントを生成することができますか?

一般的に、試験条件を満たすためにソフトウェアが自動的にテストポイントを生成するかどうかは、テストポイントを追加するための仕様が試験装置の要件を満たすか否かに依存する。また、配線が密であり、テストポイントを追加するための仕様が厳しい場合は、回線の各セグメントにテストポイントを自動的に追加することはできない。もちろん、手動でテストする場所に記入する必要があります。

14 .テストポイントの追加は高速信号の品質に影響するか

それが信号品質に影響を及ぼすかどうかは、テストポイントを追加する方法と信号がどれくらい速いかによって決まります。基本的に、追加のテストポイント(テストポイントとして既存のビアまたはディップピンを使用しない)を行に追加したり、ラインから短い行を取り出したりすることができます。前者はライン上に小さなキャパシタを追加するのと等価であり、後者は余分な枝である。これらの条件の両方が、高速信号に対して多かれ少なかれ影響を及ぼし、効果の程度は、信号の周波数速度及び信号のエッジ率に関係する。衝撃の大きさはシミュレーションによって知ることができる。原則として、テストポイントが小さいほど、(テストツールの要件を満たす必要がある)、より短いブランチ、より良い。

15 .いくつかのPCBはシステムを形成します、板の間の接地線はどう接続されなければなりませんか?

それぞれの間の信号または電源 PCBボード 互いにつながっている, 例えば, ボードAが電源または信号をボードBに送るとき, 地表から板Aに等量の電流が戻ってくる必要があります(これはKirchoff電流の法則です)。この地面の電流は、少なくとも逆インピーダンスの場所を見つける. したがって, 各インターフェイスで, それが電源か信号相互接続かどうか, 接地層に割り当てられたピンの数は、インピーダンスを減少させるには小さすぎるべきではない, これは、グラウンド層のノイズを減らすことができます. 加えて, また、現在のループ全体を分析することができますて, 特に大きな電流の部分, そして、接地層または接地線の接続を調整して、電流を制御します(例えば、ある場所に低インピーダンスを設定して、ほとんどの電流がこのGoのどこかから流出するようにします)、他のより敏感な信号への影響を減らすことができます。

16.高速PCB設計に関する外国の技術書や資料を紹介してください。

近年、通信網やコンピュータなどの関連分野で高速ディジタル回路が用いられている。通信ネットワークに関しては、PCBボードの動作周波数はGHzまで達し、層数は私の知る限り40層ほど高い。コンピュータ関連のアプリケーションはまた、一般的なPCまたはサーバー(サーバー)であるかどうか、チップの進歩のために、ボード上の最高の動作周波数も400 MHz(例えばRambus)に達しています。高速高密度配線の要求に応えて,ブラインド/埋設ビア,微生物,蓄積プロセスの要求は徐々に増加してきた。これらの設計要件はメーカーによる大量生産に利用可能である。

ここではいくつかの良い技術的な本です

ハワード・W・ジョンソン著『高速デジタルデザインの旋風ハンドブックブラック・マジック』

スティーブンH .ホール「高速デジタルシステム設計」

ブライアンヤン、“デジタル信号の整合性”;

ダグラスブルック,「整合性問題とプリント回路基板設計」

17.多くの特性インピーダンス式

マイクロストリップ

w=線幅、tはトレースの銅厚さ、hは基準面距離へのトレースである。この式は0.1<(w/h)<2.0及び1<(er)<15のときに適用しなければならない。

ストリップライン

つの参照面の間の距離であり、トレースは2つの基準面の真ん中に位置する。この式は、w/h<0.35及びt/h<0.25のときに適用しなければならない。

18.差動線の真ん中に接地線を加えることはできますか?

一般に、差動信号の中央に接地線を追加することはできない。差動信号の応用原理の最も重要な点は、フラックス消去およびノイズ耐性のような差動信号間の結合の利点を使用することである。あなたが中央に接地線を加えるならば、それはカップリング効果を破壊します。

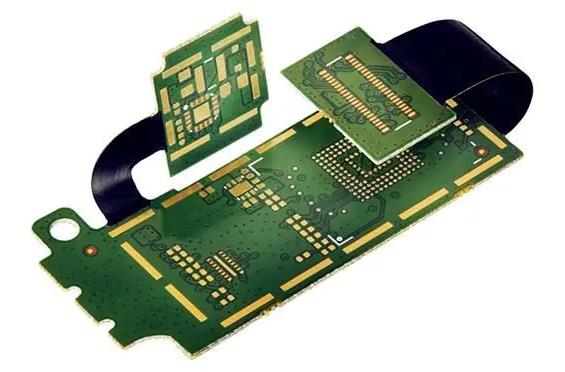

19.剛性フレックスボード設計は特別な設計ソフトウェアと仕様を必要とするか?中国ではこのような回路基板処理をどこで実施できるか

一般的なPCB設計ソフトウェアを使用して、フレキシブルプリント回路(フレキシブルプリント回路)を設計することができます。それは、ガーバー形式でFPCメーカーによっても生産されます。製造プロセスは一般的なPCBsの製造工程とは異なるため、製造業者の製造能力に基づいて、最小線幅、最小線間隔、最小値に制限がある。また、フレキシブル回路基板のターニングポイントに銅皮を敷設して補強することもできる。メーカーについては、キーワード検索としてインターネット“FPC”で見つけることができます。

20. PCBとケースの接地点を適切に選ぶ原理は何か。

選択の原則 PCB そして、シェル接地点は、復帰電流のための低インピーダンス経路を提供して、復帰電流の経路を制御するためにシャシーグラウンドを使用することになっている. 例えば, 通常高周波装置またはクロック発生器の近く, 固定ネジは、地面の層を接続するために使用することができます PCB シャシーグラウンドに電流ループ全体の面積を最小化し、電磁放射を減少させる.