基地局システム(BTS)は、様々な基準を満たしながら信号リンクの指標要件を満たす必要がある。本文はデジタル無線周波受信機における動的高性能ADC及び無線周波数デバイスのいくつかの信号リンクデバイス、例えば高動的性能ADC、可変利得増幅器、ミキサ及び局部発振器を紹介し、そして典型的な基地局におけるそれらの応用を詳しく紹介し、基地局システムの高動的性能、高インターセプト性能及び低雑音に対する要求を満たす。

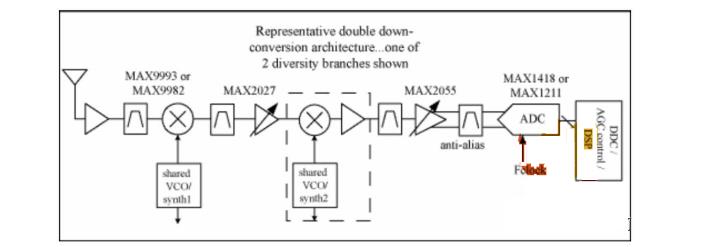

ほとんどのデジタル受信機は高性能アナログデジタル変換器(ADC)とシミュレータに高い要求を持っている。例えば、セルラ基地局デジタル受信機は、低レベルの有用な信号を復調するために、大きな干渉信号を処理するのに十分なダイナミックレンジを必要とする。Maximの15ビット65 mspsアナログデジタル変換器max 1418または12ビット65 mspアナログデジタル変換器max 1211は、2 GHz max 9993または900 MHz max 9982集積ミキサと結合され、受信機の2段キー回路に優れた動的特性を提供することができる。さらに、Maximの中間周波数(if)デジタル可変利得増幅器(DVGA)max 2027およびmax 2055は、多くのシステムにおいて高い3次出力カットオフ(OIP 3)を提供し、システムに必要な利得調整範囲を満たすことができる。

Max 1418 ADCチップ及び回路

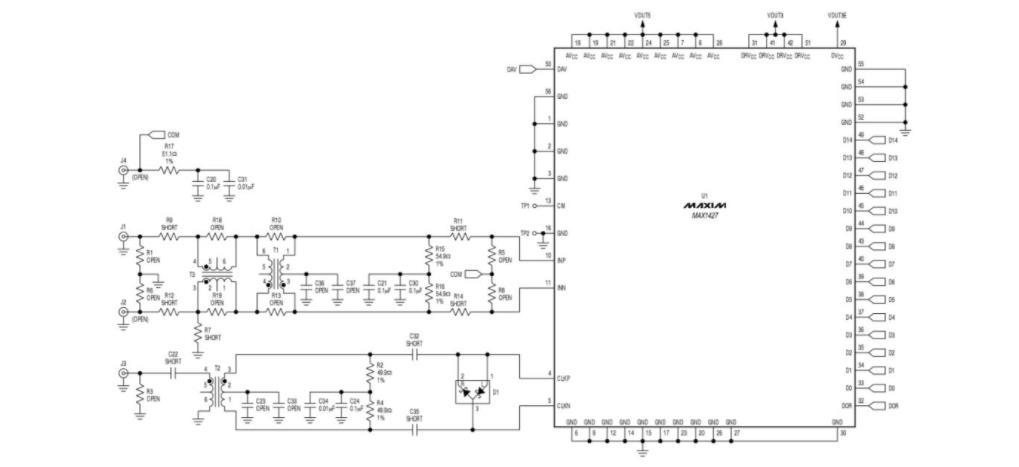

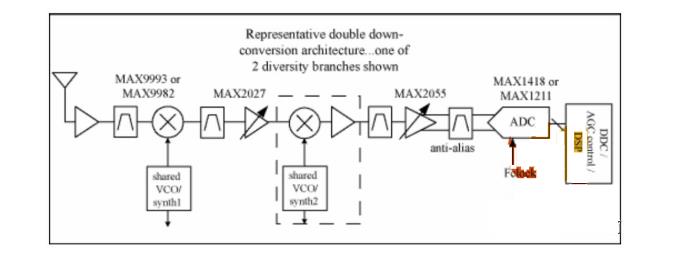

セルラ基地局(BTS:基地局トランシーバ)は、RF受信(Rx)および送信(TX)機能を実行するトランシーバ(TRX)モジュールであるいくつかの異なるハードウェアモジュールから構成される。古いアナログ増幅器とTACs BTSでは、トランシーバは1つの全二重RXとTX RF搬送波を処理するためにしか使用できません。必要な呼カバレッジを実現するためには、十分なキャリアを提供するために多くのトランシーバが必要である。今日、世界的にシミュレーション技術はCDMAとWCDMAに取って代わられ、GSMは10年前に欧州で採用された。CDMAでは、複数の発呼ユーザが同じRF周波数を使用するので、1つのトランシーバが複数の発呼ユーザの信号を同時に処理することができる。これまでにも、CDMAやGSMの設計案はさまざまなものがありました。BTSメーカーもコストと消費電力を削減する方法を模索してきた。シングルキャリアソリューションを最適化するか、マルチキャリア受信機を開発することが有効なソリューションです。【図1】BTS装置で一般的に使用されるアンダーサンプリング受信機の構成ブロック図である。

図1。アンダサンプリング受信機構成ブロック図

図1では、Maximの2 GHz max 9993と900 MHz max 9982ミキサは、多くの設計に必要な利得と線形性を提供することができ、非常に低い結合雑音を有するので、高損失の受動ミキサは不要である。Max 2027およびmax 2055は、受信機の第1および第2の中間周波数段で動作する。これら2つのデバイスのOIP 3は、利得調整範囲全体で+40 dbmに達することができる。図1に示す回路では、データ変換器としてmax 1418(15ビット、65 msps)とmax 1211(12ビット、65 ms)が使用される。また、Maximのデータ変換器製品にはサンプリングレートを持つ他のデバイスもあり、設計要件のほとんどを満たすことができます。図1の2番目のダウンコンバータ(破線で示す)を省略すると、図1に示す回路は単一のダウンコンバータ構造になる。Maximの低雑音ADC:max 1418。

図1に示すアンダーサンプリング受信機の構成は、ADCのノイズ及び歪みに対して厳しい要件を有する。受信機では、低レベルの有用な信号が個別にデジタル化されたり、より多くの関心を必要とする不要な大幅な信号が伴ったりします。したがって、受信機を正常に動作させるためには、ADCの有効ノイズ係数は、これら2つの信号の極限条件(すなわち、最小有用信号と最大不要信号)に基づいて計算されるべきである。小さいアナログ入力信号に対して、熱雑音及び量子化雑音はADCの雑音基底であり、これはADCの雑音係数を決定する。

実際には、小信号条件下でのADCの有効ノイズ係数は決定され、アナログ回路(RFまたはif)のカスケードノイズ係数も対応して決定される。ADC前段回路の最小電力利得は、受信回路のノイズ係数要件を満たすべきである。一般に、電力利得値は、ADC過負荷前に受信機によって許可される最大ブロッキングレベルまたは最大干渉レベルの上限である。BTSでは、AGCを使用しない場合、ADCのダイナミックレンジは回路ノイズ係数(受信機感度)と最大ブロッキングの要件を満たすことができない。AGC回路は、無線周波数または中間周波数レベル回路またはAGC回路の2段回路に配置することができる。

max 1418シリーズの他の製品は、特にfeinput=fclock/2のベースバンドアプリケーションに適しています。変換器がこの周波数範囲で動作している場合、ベースバンド特性に優れたこれらのデバイスを使用すると、最適なダイナミックレンジが得られます。これらの製品には、65 mspsクロックレートのmax 1419および80 mspsクロックレートのmax 1427が含まれる。ベースバンドSFDR(ランダムダイナミックレンジ)は94.5 dbcに達することができる。

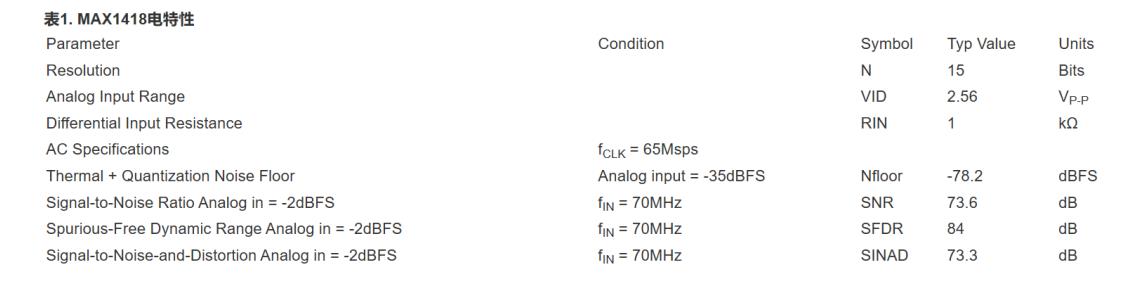

表1にmax 1418の主な技術パラメータを示す

LSBが接続されていない場合、max 1418は14ビットインタフェースデバイスと一緒に動作することもできる。これにより、SNRはわずかに損失するが、SFDRは影響を受けない。

図2は、ブロックされていない場合のADCのノイズ分布を示す。ここでは、ADC以前のすべてのアナログ回路の全カスケード雑音係数を3.5 dbと仮定し、CDMA基地局受信機の感度要件を満たすために、設計目標は、ADCによる全雑音係数の劣化が0.2 dbを超えないことである。このようなノイズ係数値は、空中インタフェースに十分なマージンを残すべきであるが、最終的な結果は、最終的な検出器のEB/no(ビットエネルギーとノイズ電力スペクトル密度の比)の要件に依存する。表1のmax 1418の熱雑音+量子化雑音基板に基づいて、デバイスクロックが61.44 msps(50倍チップレート)の場合、その等価雑音係数は26.9 dbである。プロセス利得制御のため、1.23 mhzCDMAチャネル帯域幅におけるADCノイズはナイキスト広帯域におけるADCより14 dB低い。一般に、3.7 dB受信機のカスケード雑音係数を得るためには、総利得は36 dBに達するべきである。

図2:ブロッキングフリーADCノイズ分布

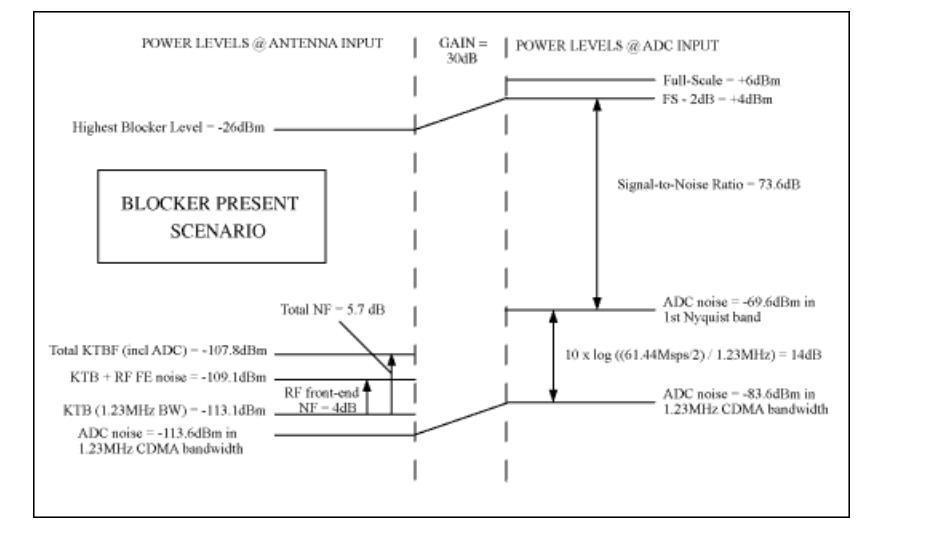

ADCフロントエンド利得が36 dBの場合、アンテナ端が−30 dBmを超える単音ブロッキングレベルはADCの入力範囲を超えることになる。cdma 2000®セルラ基地局規格では、アンテナ端で許容される最大ブロッキングレベルは-30 dBmである。この場合、ADCに追加される最大ブロッキング信号が標準仕様で許容されるマージン範囲内でより大きくなるように、フロントエンド利得を6 dB下げる必要がある。残りの2 dBのマージンを仮定すると、カレントエンド利得が6 dB減少すると、アンテナ端の最大ブロッキングレベルは−26 dbmになり、ADCの最大許容入力信号は+4 dbmになる(図3参照)。単音閉塞が発生した場合、ハニカム規格は、基準感度に対して全干渉(ノイズ+歪み)が3 dB悪化することを可能にしたが、ノイズと歪みの間に3 dBを割り当てる方法を設計者に残した。

仮定:ブロッキング信号の場合、AGC利得は6 dBであり、この設計によりRFフロントエンドカスケード雑音加歪がNFを1 dB(公称値3.5 db)低減することができる。ADCフロントエンド利得が30 dBにすぎない場合、ADCの信号対雑音比はその有効雑音係数を29.4 dbと決定し、カスケード受信機の「ブロッキング条件」における雑音係数は5.7 dbであり、受信機感度に基づいて計算された3.7 db雑音係数より2 dB低い。この計算では分散特性が考慮されていないため、ADCの非分散ダイナミックレンジ(SFDR)により、1 dBの追加的な減少が可能になる。ブロッキング信号がある場合、SINADを使用して有効NFを計算することができ、ノイズとSFDRベース値を別々に計算することはできません。

図3。ブロックされた場合のADCノイズ応答

Max 11211はダウンコンバート構造を可能にする

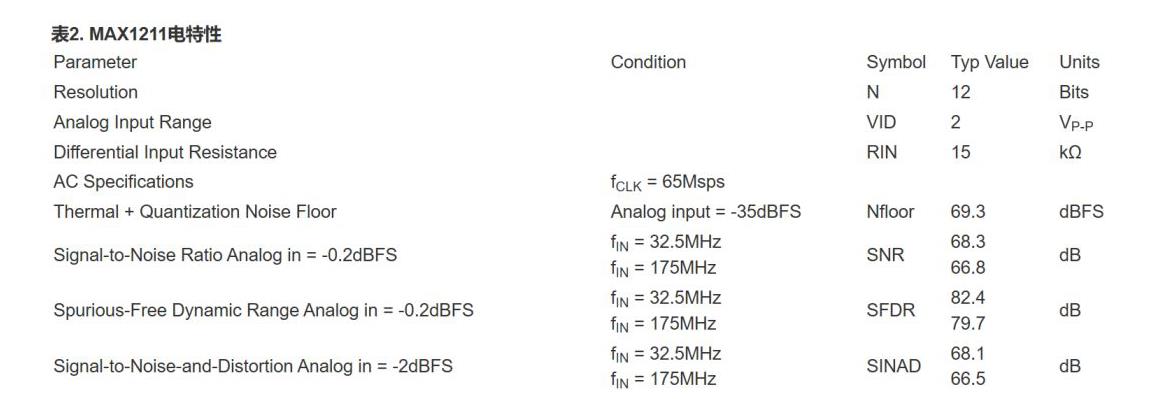

高いIfセグメントで十分なSNRおよびSFDR指標が得られる場合、プライマリダウンコンバート構造においてアンダサンプリング回路を使用することができる。この構造を用いてMax 11211 12ビット65 msps変換器を設計した。そのピンは、間もなく発売される80 mspsおよび95 mspsコンバータと互換性があります。これらの一連のデバイスは、入力信号を直接サンプリングすることができ、数が多い場合は400 MHzまでの周波数を持つことができます。また、クロック入力は差動信号またはシングルエンド信号であってもよく、クロックのデューティサイクルは20%から80%の間であってもよく、また、データ有効インジケータ(クロックとデータ系列を簡略化)があり、小型40ピンQFN(6 mmx 6 mmx 0.8 mm)パッケージ、バイナリ補完、グレコードデジタル出力フォーマットを採用している。表2に、175 mhzのアナログ入力周波数を有するmax 11211の典型的な交流特性を示す。

図表2.MAX 1211電気特性

二次周波数変換の構造に比べて、一次周波数変換には明らかな利点がある。第2のダウンコンバートミキサ、第2の中間周波利得回路、第2のLO合成器を排除することで、部品の数と回路基板のスペースを約10%削減でき、10 ~ 20ドルのコストを節約できる。

異なる構造の分散を考慮する。部品点数、ボードスペース、消費電力、コストをさらに節約する必要がある場合は、以下に示す1次周波数変換構造を採用することができます。設計されたCDMA 2000受信機はPC周波数帯で動作し、サンプリングレートは61.44 msps、合成器基準周波数は30.72 mhz、第1中間周波数の中心は169 MHzの第6ナイキスト周波数帯、帯域幅は約1.24 mhzを選択したと仮定する。DDS構造では、同じ169 MHzの第1の中間周波数と第2の中間周波数中心周波数は、2次ナイキスト周波数帯域の46.08 mhzである。

SDCとDDCアーキテクチャの仮想的な分散特性

表3は、シングルキャリア、メインダウンコンバート(SDC)、およびダブルダウンコンバート(DDC)構造を使用した場合に、PC帯域上端付近でRFキャリアのスプリアス探索を行う仮定条件を示す。SDC構造では、RF受信周波数、受信ミラー周波数帯域、if周波数帯域、およびifミラー周波数帯域に134の高調波成分を見つけることができる。これらのスプリアス信号の多くは高次を持ち、受信性能を低下させることはありません。DDC構造については、スプリアス探索により、SDC構造の18倍以上の2400以上の高調波が発見される。これらの高調波は、RF受信帯域、受信ミラー帯域、帯域であれば第1レベル、ミラー帯域であれば1レベル、帯域であれば第2レベル、ミラー帯域であれば2レベルに分布する。高次クロック高調波と合成器の基準周波数からのスプリアス信号については、回路基板のレイアウトをよく考慮するか、設計にフィルタを追加することで抑制することができる。しかし、より低い次数を有する大量の浮遊成分を抑制することは困難である。

マキシム中間周波増幅器:max 2027とmax 2055

Maximはまた、各ステージ1 dBのデジタル制御利得と高性能if増幅器を提供する。Max 2027はデジタル制御利得増幅器(DVGA)である。単一入力/単一出力モードを採用し、50 MHzから400 MHzの周波数範囲で動作することができ、その最大利得ノイズ係数はわずか5 dBである。Max 2055は単一入力/差分出力のDVGAで、30 MHzから300 MHzの周波数範囲内の高性能ADCを駆動することができる。max 2055の差分出力とADC差分入力との間に昇圧トランスを使用することができる。変圧器は差動駆動を提供し、出力信号間のバランスを容易にする。2つのDVGAは5 Vバイアスで動作し、利得設定全体で+40 dbmのOIP 3を有する。詳細については、格言サイト(china.maximantegraded.com)を参照してください。マキシムの高線形ミキサー:max 9993とmax 9982。

受信回路では、ミキサはしばしば大きな入力信号に耐え、その性能に対する要求が高い。理想的な状態では、ミキサ出力信号の振幅及び位相は入力信号の振幅及び位相に比例し、この比例関係はLO信号に依存しない。この仮定によれば、ミキサの振幅応答はRF入力と線形関係にあり、Lo入力信号とは無関係である。

しかし、ミキサの非線形性は、ミキサRFポートに到達した信号によって生成される中間周波数帯域の応答であり、発生しないことが予想される不純応答と呼ばれる不要なミキサ信号を生成する。不要なスプリアス信号は有用な無線周波数信号の動作を妨害する。ミキサの周波数を次の式で指定できる場合は、

=±MRF±nfloの場合、RFとloはそれぞれのポートの信号周波数であり、mとNはRFとlo信号を混合した高調波次数である。

統合(またはアクティブ)平衡ミキサ(例えば、max 9993およびmax 9982)は、パッシブミキサ方式よりも性能が優れていることで注目されている。mまたはnが偶数である場合、平衡ミキサは一定の浮遊応答を抑制でき、第二高調波性能が良い。理想的な二重平衡ミキサは、偶数のMまたはn(または両方)のすべての応答を抑制することができる。デュアルバランスミキサでは、if、RF、およびloポートは互いに分離される。合理的に設計された不平衡変圧器を使用することにより、ミキサはif、RF、LO周波数帯域で重複することができる。Max 9993とmax 9982の特徴は、低雑音係数、LOバッファ、低LO駆動、2つのLO入力を許可するLOスイッチ、優れたLO雑音特性などである。また、RF不平衡変圧器もRFとLOポートに統合されている。

Maximのこれらのミキサは、低ノイズ性能に優れた低ノイズバッファを組み込み、低ノイズ電源への要求を低減しています。一般に、低ノイズと高レベルの入力ブロッキング信号との組み合わせは、受信感度を低下させる。Max 9993とmax 9982は低雑音Loバッファを含み、ブロックされた場合に受信感度への影響を低減することができる。例えば、VCO入力信号のサイドバンドノイズが−145 dbc/hzであり、max 9993の典型的なLoノイズ特性が−164 dbc/hzであると仮定すると、複合サイドバンドノイズは0.05 dbc/hzから−144.95 dbc/hzだけ低下する。このようにして、ユーザはミキサにローレベルのLO信号を提供するだけでなく、max 9993に内蔵されたLOバッファの性能によって受信機のミキサ特性が低下しないことを保証する。

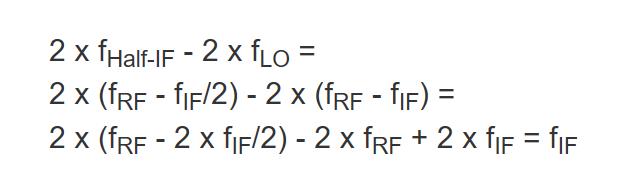

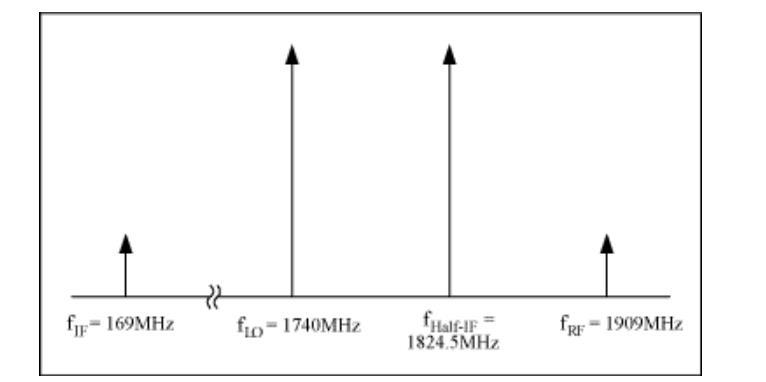

また、半if(1/2 if)スプリアス応答とも呼ばれる、厄介な二次スプリアス応答がある。ローエンド射出の場合、ミキサーの順序はM=2、n=-2、ハイエンドジェットの場合、ミキサーの順序はM=-2、n=2です。低注入が低い場合、半虚寄生応答の入力周波数は所望のRF周波数より低くなる(図4)。必要なRF周波数は1909 mhzと1740 mhzのLO周波数であり、IF周波数は169 MHzである。CDMAのRFおよびifキャリア帯域幅は1.24 mhzであるが、ここでは中心キャリア周波数を有する単一周波数信号として表される。この例では、1824.5 mhzの不要な信号は、169 MHzの半中間周波数不純物成分をもたらす:

これにより、次のことができます。

2 x 1824.5MHz-2 x 1740MHz=169MHz

図4。FRF、Flo、FIF、不要なfhalfがある場所(周波数の場合)

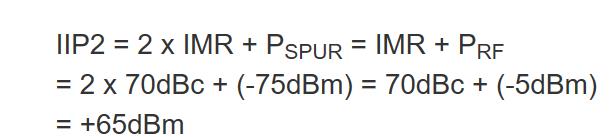

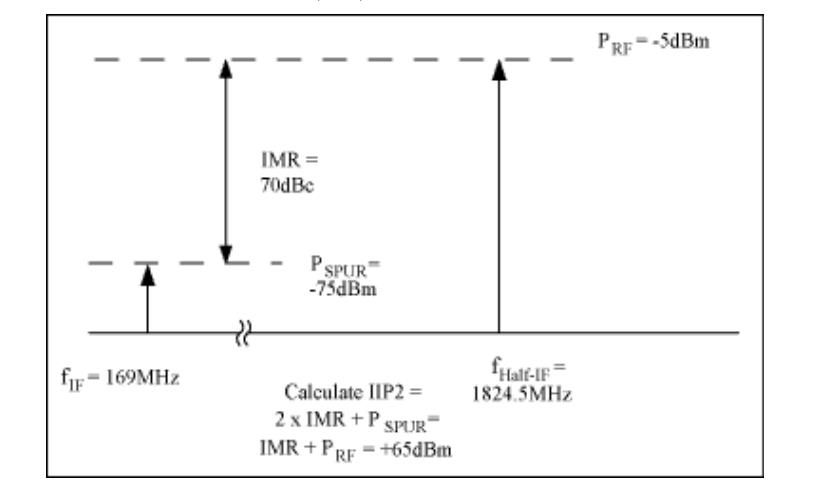

総抑制(2 x 2スプリアス応答とも呼ばれる)は、ミキサの第2のカットオフポイントIP 2に基づいて予測することができる。図5は、2 x 2 IMRまたは分散値(Maximのmax 9993データ)を示す。注意:図中の信号レベルは入力IP 2(IIP 2)の性能に基づいて計算されたミキサ入力レベルである。具体的な計算式は次のとおりです。

Maxim max 9982 900 MHzアクティブフィルタによって提供される典型的なスプリアス応答2 rf−2 loは65 dbcであるため、そのIIP 2の計算方法は以下の通りである:

図5。ミキサ入力信号の第2のカットオフ点IIP 2を計算する

受信機の利得要件が高くない場合、Maximの15ビットADC max 1418は優れたノイズ性能を持つため、大きなブロッキングレベルまたは干渉レベルを最小のAGCで受けることができる。Max 1211 ADCシリーズ製品は、最初の中間周波数入力周波数が400 MHzに達する1次周波数変換受信構造に適している。さらに、Maximのmax 9993およびmax 9982ミキサは、所望の線形度、低雑音係数、および高電力利得を提供することができ、したがって、受信機設計中に受動フィルタを省略することができる。利得調整可能範囲全体で、最大2027と最大2055 DVGAのOIP 3の典型的な値は約+40 dbmである。これらの構成部品からなる受信機は、低コストソリューションのパフォーマンスをより高いレベルに高めることができます。本文はデジタル無線周波受信機の中のいくつかの高動態性能ADCと無線周波装置の信号リンク装置を紹介して、もしあなたが何か問題があれば、iPCBと交流することを歓迎します。