概要:現在のSOCを成功裏に使用するためには、ボードレベルとシステムレベルの設計者は、コンポーネントの配置、トレースのレイアウト、保護コンポーネントの使用方法を理解する必要があります。

これらはデジタル携帯電話と呼ばれていますが、以前のいわゆるアナログ携帯電話よりもアナログ機能が多く含まれています。実際には、音声、画像、温度、圧力などの連続した状態値を処理する必要があるシステムには、名前に数字が表示されてもシミュレーション機能があります。今日のマルチメディアPCも例外ではありません。音声とビデオの入出力、暖房中央処理ユニットの緊急温度監視、高性能モデムがあります。これらのシステムもハイブリッド信号機能リストの項目である。も増えてきています。

この2つのシステムの傾向は、ハイブリッド車を設計する人に新たな挑戦をもたらした。携帯通信や計算装置の体積や重量は減少し続けているが、その機能は増加し続けている。デスクトップシステムは、中央プロセッサの容量と通信周辺機器の速度を向上させ続けています。現代のデジタル回路基板を設計しながら、リンギング、ノイズによる誤差、接地電位リバウンドを回避することは非常に困難であることは間違いない。しかし、ノイズの影響を受けやすいアナログ信号線を方形波励起デジタルデータ線の近くに追加すると、問題はさらに深刻になります。

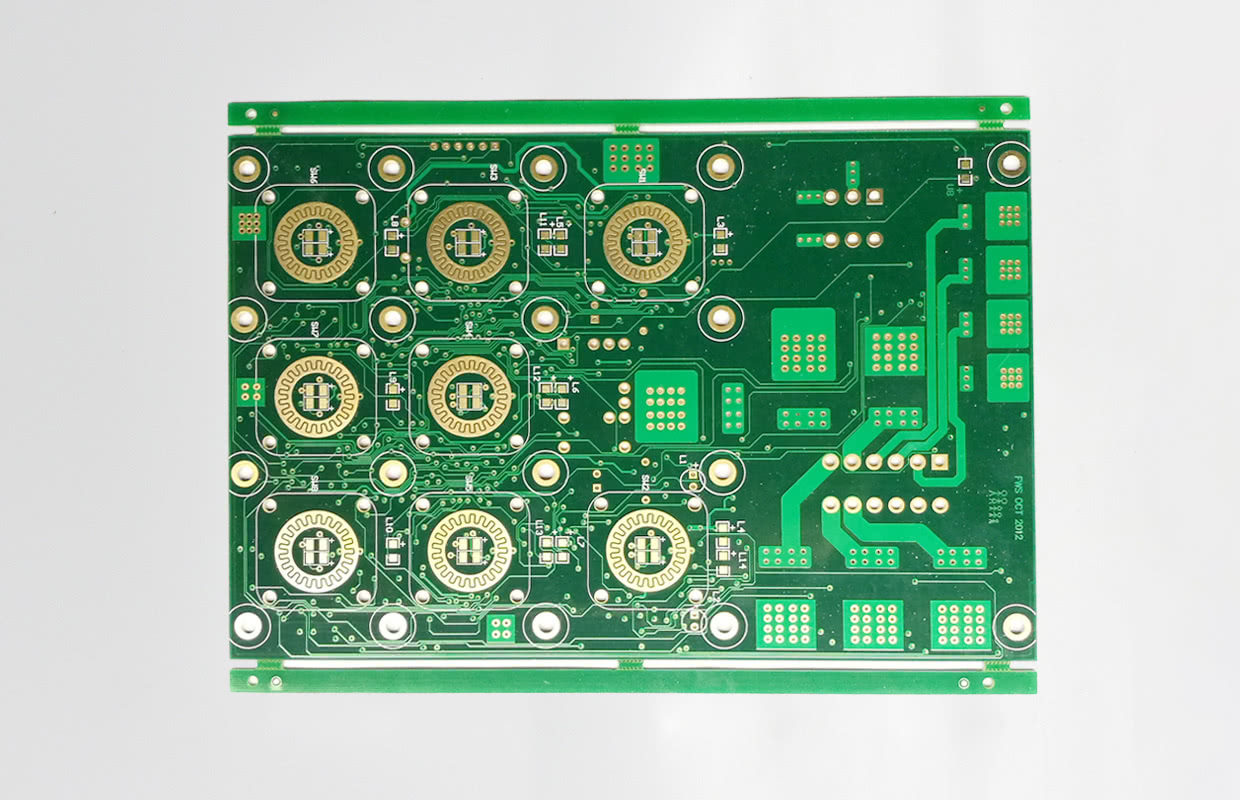

チップレベルでは、現在のSOC(オンチップシステム)には、論理回路、アナログ回路、熱力学設計に関する専門知識が必要です。これらのICを成功裏に使用するためには、パネルレベルとシステムレベルの設計者は、コンポーネントの配置、配線トレース、および保護コンポーネントの使用方法を理解する必要があります。

本論文では、現在のハイブリッド信号システム設計における一般的なトラップについて説明し、これらのトラップを除去または除去するためのガイドラインを提供します。しかし、具体的な問題を議論し、提案する前に、システム設計の小型化と高速化の2つの傾向がこれらの問題にどのように影響するかを詳細に理解することが役立ちます。

1.「高速化」の傾向

1999年のミッドレンジPCの仕様を5年前の仕様と比較したところ、中央プロセッサの速度は約1桁増加し、CPUの消費電流も約数桁増加した。高速と大電流を結合すると、V=L(di/dt)関係の「di/dt」部分が大きく改善されます。実際には、回路基板の長さ半インチの接地線に1ボルトを超える電圧が誘起される可能性があります。コンバータにとって接地電位基準線は電圧を誘起し、動作が停止する可能性があります。

これらのより高い速度を実現するために、ICの設計と製造は深さサブミクロンサイズ(例えば、0.35μm)を有する。これは幾何学的なサイズを減少させ、より速い性能をもたらしたが、これらの装置は過渡的に引き起こされるラッチと損傷を引き起こす可能性が高い。さらに、これらのデバイスは、ますます厳しい許容電圧範囲に適合するために、より厳格なエネルギー管理を必要とする。

現在の10/100イーサネットネットワークインタフェースカード(NIC)が良い例です。従来の10 Base-Tチップは大規模なCMOSデバイスであり、過電圧損傷には相対的に敏感ではなかった。しかし、新しいチップは0.35 Isla 188 mの線幅を使用しており、これは電気エネルギーと稲妻による瞬変によるロックと故障に非常に敏感である。

SMP(対称マルチプロセッサ機能)アーキテクチャを持つ現代のサーバと、500 MHz以上の周波数で動作するCPUは、エネルギー分配の課題の好例である。5 V電源を簡単に構築し、適切なバスに配線することはできません。500 MHzで20 Aまたは30 Aまでの電流でスイッチングするには、実際には使用点ごとに独立したコンバータが必要であり、これらのコンバータのすべてのより大きな主電圧源から電力を供給する必要があります。

この傾向にはホットプラグ機能が必要であり、現在のシステムに基板を挿入または除去する必要があることを意味します。これも瞬変を予測するためである。これにより、挿入されたマザーボードとマザーボードの両方に適切な保護が必要になります。

小型化と高速化の傾向には独特の問題がある。例えば、高電流エネルギー分布は、小型、携帯型及びハンドヘルド装置にとって大きな問題ではない。デスクトップPCやサーバの場合、バッテリ寿命の延長は問題になりません。しかし、ロックと過渡による損傷はこの2つの分野で問題となっている。

2.「小型化」の傾向

5年前の製品に比べて、1999年の携帯電話チップの数はずっと少なく、重量と体積は大幅に減少し、電池の寿命も大幅に延長された。この過程で、主な要因はハイブリッド信号ICソリューションの大きな進歩である。しかし、チップの幾何形状が減少するにつれて、回路基板上の配線の間隔が近くなり、物理法則が現れ始めた。

平行トレースはますます近くなり、距離の2乗に反比例した結果としてますます大きな寄生容量結合が生じる。昔はわずかな空間的痕跡しかなかったが、今では多くの痕跡が含まれている。そのため、非隣接トレース間の容量結合であっても問題が生じる。

携帯電話はその性質によって決定され、人々が所有し、使用する設備である。低温の日にカーペットの上を歩いてきて、携帯電話を手に取って、「パチン」と音を立てます。これはデバイスに高圧静電放電(ESD)パルスを送信します。適切なESD保護がなければ、1つまたは複数のICが破損する可能性があります。しかし、ESDの損傷を防ぐために外部コンポーネントを追加することは、小型化の傾向に反する可能性があります。

もう1つの問題はエネルギー管理です。携帯電話ユーザーは、バッテリーの2回の充電間隔が長いほど良いことを望んでいる。これは、DC-DCコンバータが非常に効率的でなければならないことを意味します。スイッチ技術がその答えだが、この場合、コンバータは自身の潜在的なノイズ源にもなる。そのため、コンバータは慎重に選択し、配置し、相互接続する必要があります。また、体積は無視できない要素であるため、物理的なサイズが最も小さいパッシブコンポーネントを使用できるコンポーネントタイプを選択する必要があります。リニアレギュレータを使用する場合は、出力を最小バッテリ電圧に維持できる超低電圧降下タイプを選択する必要があります。これにより、バッテリが十分な電力を供給しなくなる前にできるだけ多くの電力を放電することができます。

3.ロックと過渡

線幅から深サブミクロンICへの過渡状態は過電圧条件への感受性を悪化させ、性能に影響を与えずにこれらのデバイスをよりスマートに保護しなければならないことを意味します。

保護入力では、任意の保護要素は通常の動作下で高インピーダンス回路として表現されなければならない。例えば、通常の入力信号に小さな影響を与えるには、できるだけ小さな容量負荷を負荷しなければなりません。しかし、過電圧の時点では、同じデバイスは保護されたデバイスの入力から遠ざかるように、過渡エネルギーの主要な経路にならなければならない。さらに、保護装置の耐圧は、保護されたピン上の最大許容電圧より高くなければならない。同様に、クランプ電圧は保護されたデバイスの損傷を防ぐために十分に低くなければならない。これは、過渡的な条件下では、入力上の電圧が保護装置のクランプ電圧になるからである。

従来、過渡電圧抑制(TVS)ダイオードはプリント基板上の過渡を効果的にクランプしていた。従来の(TVS)ダイオードは固体PN接合素子であり、5 Vまで低い電圧でよく動作する。これらは高速応答時間、低クランプ電圧、高電流サージ能力を有し、これらはすべて必要な特性である。しかし、従来のTVSダイオードの問題は、5 V未満では頭が上がることである。ここでは、彼らが使用している雪崩技術が障害となっています。5 V未満のカットオフ電圧を実現するためには、高度なドーピング(1018/cm−3以上)が必要である。これは逆に、より高い容量とリーク電流をもたらし、どちらも高性能を損なうことになります。従来のTVSダイオードは、電圧が低下するにつれて増加する電圧依存容量を有する。例えば、5 Vでは、典型的なESD保護ダイオードは400 pFの接合容量を有する。このような容量性負荷が100 Base−TEthernet送信機または受信機の入力ノードに印加されたり、汎用シリアルバス(USB)入力に印加されたりすると、何が起こるか想像することができます。また、これらはまさに過渡的保護が最も必要な回路タイプです。

電圧が5 V未満の場合、従来のTVSダイオードは実際には選択されていない。しかし、これはあなたが選択の余地がないことを意味するわけではありません。カリフォルニア大学バークレー校とSemtech(カリフォルニア州ニューベリーパーク)が共同で開発した新技術により、2.8 Vまでの低瞬時およびESD保護が可能になりました。一連のTVSデバイスから適切な容量、カットオフ電圧、クランプ電圧を選択して、独自のシステムの要件を満たすことができます。その後、デバイスをボードの上に置くべき場所や、回路基板をどのように配線するかも考えなければなりません。

保護経路中の寄生インダクタンスは高電圧オーバーシュートを引き起こし、ICを損傷する。ESDなどの急速上昇時間過渡については、特にそうである。IEC 1000−4−2の定義によれば、ESDによる過渡状態は1ナノ秒(ns)未満の時間でピークに達する。20 nH/インチのトレースインダクタンス計算によると、10 Aパルスの4つの1インチトレースは50 Vのオーバーシュートを引き起こす。

接地回路、TVS、保護回路間のパス、コネクタからTVSデバイスへのパスなど、可能なすべてのインダクタンスパスを考慮する必要があります。さらに、TVSデバイスは、近くの他のトレースに過渡的に結合するために、できるだけコネクタに近づく必要があります。

10/100イーサネットボードは、過渡的な保護が必要なサブシステムです。イーサネットスイッチとルータで使用されているデバイスは、高エネルギー稲妻誘導の過渡状態にさらされています。使用される深さサブミクロンICは、設計において過電圧ロックに極めて敏感である。典型的なシステムでは、各ポートで使用されるツイストペアインタフェースは、2つの異なる信号ペアで構成され、1対は送信機用、もう1対は受信機用である。トランスミッタ入力は通常、最も損傷を受けやすい。線対には異なる致命的な放電があり、変圧器容量を介してイーサネットICに結合されます。

信号周波数が非常に高く(100 Mbit/s)、電源電圧が低い(通常3.3 V)場合があり、保護装置は非常に低い容量性負荷を有し、その遮断電圧は5 Vよりはるかに低い必要がある。また、保護経路中の寄生インダクタンスが大きな電圧オーバーシュートを引き起こす場合もある。効率を最大限に高めるためには、回路基板の配線は、プロテクタと被保護回路との間の経路を最小化しなければならず、RJ 45コネクタとプロテクタとの間の経路長も最小化しなければならない。

4.熱交換/プラグアンドプレイ

システムに電源が投入されたままプラグやプラグをいつでも挿入して引き抜くことができるように設計されているシステムが増えています。これらのプラグやプラグは、キャリア信号、電源線、アース線のソケットを挿入したり引き抜いたりして、瞬時に変化する可能性が高い。さらに、システムは、電流負荷の急激な増加または減少に対応するように動的に電源を調整することができる。

充電中に、携帯電話や他の携帯型電子機器が充電システムから誤って挿入されたり抜き取られたりします。これも過渡的になります。ここで、過渡的保護に加えて、電流負荷の急激な増加または減少に対応するためのエネルギー管理が必要である。

USBインタフェースは、デスクトップシステムと周辺機器間の高速シリアルインタフェースを改善することを目的としている。また、UBインタフェースには、接続された周辺機器に電力を供給するための電圧供給ラインがあります。USBソケットに負荷が挿入されていない場合は、ソケットがオープンソケットであることを示します。ソケットに人体の静電気を感知したESDパルス放電は回路基板に伝導し、USBコントローラを損傷しやすい。

この高速バスでは、データ線と電源線が保護されていることを確認する必要があります。さらに、エネルギー管理はUSB仕様に書き込まれているが、ESD保護は提供されていない。

TVSデバイスは、適切なESD保護を提供するために使用することができる。コンポーネントの配置とパスの長さは依然として重要な設計問題である。同じレイアウトガイドをよく見てください。TVSと保護された回線間の経路を短縮し、TVSデバイスがポートコネクタにできるだけ近いことを確認します。

USB仕様の必要に応じて、固体回路のエネルギー分配スイッチを使用してエネルギー管理を行うべきである。PCホストでは、コントローラICに短絡電流保護とエラー報告を提供します。USB周辺機器では、ポート切り替え、エラー報告、電源電圧ランプ降下制御に使用されています。

5.エネルギー分配

PCの電気流量の変化を10年前と比較すると、その伸び幅は本当に驚くべきものです。さらにクロック周波数の大幅な増加により、PCとサーバは非常に高いdi/dt環境にある。例えば、Lが2.5°Hで、Cが4*1500°Fに等しい場合、負荷上の過渡状態は200 mVピークからピークまでのオーダーであり、回復時間は50マイクロ秒である。問題をさらに複雑にするのは、CPUがスリープモードに入り、すばやく目を覚ますことです。発生する過渡はマイクロ秒当たり20〜30 Aの範囲であり、エネルギー管理の頭痛の問題となっている。

コンバータの観点から見ると、di/dtの値は出力コンデンサの選択に影響し、より具体的には、コンデンサの等価直列抵抗(ESR)と等価直列インダクタンス(ESL)に影響する。低周波で動作するコンバータは、電解コンデンサを使用する必要がある2つの動作サイクル間の電荷を格納するために大きな容量を必要とする。これらの電解コンデンサは大きな容量を持っているが、設計者の意図に反する大きなESRとESLも持っている。また、電解コンデンサは体積が大きく、表面実装技術やコンパクトパッケージには適していない。

ESRとESLの値を下げ、生産プロセスを簡略化し、実際の体積を減らす代替方法がある。方法はやや高いインバータを使用し、電解コンデンサではなくセラミックコンデンサを選択し、上記の利点を得ることができる。同時に、多相コンバータのソリューションを採用することで、負荷要件を共有することもできます。各コンバータは、同じ総電流容量を提供しながら、より少ない入力容量を必要とします。もう1つの利点は、入力リップル電流を低減することです。単相変換方式では、入力リップル電流は出力リップル電流の半分に等しい。したがって、20 Aシステムでは、入力リップル電流は10 Aである。しかし、例えば、4相変換器ソリューションの場合、出力電流は4つの変換器の間で平均的に分配される。現在、各電源は5 Aで、入力リップル電流は2 Aです。これにより、より小型で安価な入力キャパシタを使用することができます。

DellComputers(テキサス州RoundRock)は、その高速コンピュータとサーバシリーズのために離散的、多相パルス幅変調(PWM)コントローラと逆直流−直流変換器を開発した。インテルの先進的なPentiumCPUの緊急電源/エネルギー管理要件を満たすように設計されています。その後、Semtechはデルの要求に応じて回路を統合しました。多相コントローラとコンバータソリューションの後は、回路基板の配線に特に注意する必要があります。高周波での高電流スイッチは接地面の電圧差に影響する。

回路の高電流部分はまず配線しなければならない。接地面を使用するか、特定の領域への接地電流の進入を制限するために、分離または半分離接地面領域を導入する必要があります。入力キャパシタおよびハイサイドおよびローサイドドライバ出力FETによって形成される回路は、すべての高電流、高速過渡スイッチを含む。接続は、ループインダクタンスを低減するために、幅または幅、短または短にする必要があります。これにより、電磁干渉(EMI)を低減し、地面に注入される電流を低減し、ソースリンギングを最大限に低減して、より信頼性の高いゲート回路スイッチング信号を得ることができる。

2つのFETの接合と出力インダクタ間の接続は、できるだけ短い間に広い軌道であるべきである。出力コンデンサはできるだけ負荷に近づけなければならない。このキャパシタは急速な過渡負荷電流を提供するので、接続線は広く短くして、インダクタンスと抵抗を最大限に減らすべきである。

コントローラは、入力キャパシタおよびFET回路内のパルス電流がこの領域に流入するのを防ぐために、静かな接地面領域に配置することが好ましい。高接地基準ピンと低接地基準ピンは、制御増幅器アセンブリに非常に近い位置で接地に戻る必要があります。小信号アナログ接地とデジタル接地は、出力コンデンサの1つの接地に接続されるべきである。入力コンデンサ/FET回路内には絶対に接地しないでください。電流誘導抵抗器回路はできるだけ短く維持しなければならない。

6.賢い仕事

上記の例は、ハイブリッド信号システムのいくつかのトラップを予測し回避する方法を説明したが、それらは決して詳細には残されていない。各システムには独自の課題があり、デザイナーごとに独自の障害を乗り越える必要があります。より困難な保護に対処するにしても、より厳格なエネルギー管理にしても、正しいコンポーネントを選択することは最初のことです。コンバータ、コンバータコントローラ、TVS保護デバイスに挑戦する上で、幅広い選択肢があります。回路基板上の適切な位置に配置すると、エネルギー管理と保護の違いが表示されます。熟考された配線と接地面の配置は第3の側面の重要な問題である。低圧回路のTVS

電圧が5 V未満の場合、従来のPN接合TVSは実際には全く機能しない。しかし、カリフォルニア大学バークレー校とSemtechが開発した強化型貫通ダイオード(EPD)がある。

アバランシェTVSダイオードの従来のPN構造とは異なり、EPDデバイスはより複雑なn+p+p-n+4層構造を使用している。p+及びp−層に光ドーピングを用いて逆バイアスしたn+p+接合がアバランシェ状態に入るのを防止した。

pnp構造の代わりにnpn構造を選択したのは、より高い電子移動度と改良されたクランプ特性を有するためである。Pベース領域を注意深く製造することにより、得られたデバイスは2.8 Vから3.3 Vの電圧範囲で優れた漏洩、クランプ、容量特性を有する。

7.Pentium、食欲が旺盛

インテルのPentium II仕様では、電流を500 ns内で5 Aから20 Aに増加させ、変換率をマイクロ秒当たり30 Aにする必要があります。Semiteck SC 1144多相PWMコントローラは、タスクに必要な能力よりも優れています。必要な速度と精度を得るために、最大4つの逆直流変換器の制御を提供します。内蔵の5ビットDACは、出力電圧をプログラムして出力することができ、1.8から2.05 V、50 mV、20から3.5 V、100 mVの増分があります。

この多相技術は、90度離れた位相シフトを持つ4つの正確な出力電圧を生成する。次に、4つのデジタル位相シフト出力を加算して、所望の出力電圧と電流容量を得る。

各コンバータは2 MHzで動作し、設計者は電解コンデンサの代わりにセラミックコンデンサを使用することができ、小型、表面実装性、低ESRとESLの利点を得ることができる。