【集成電路基板製造商】從集成電路晶片設計、製造到封裝的全過程

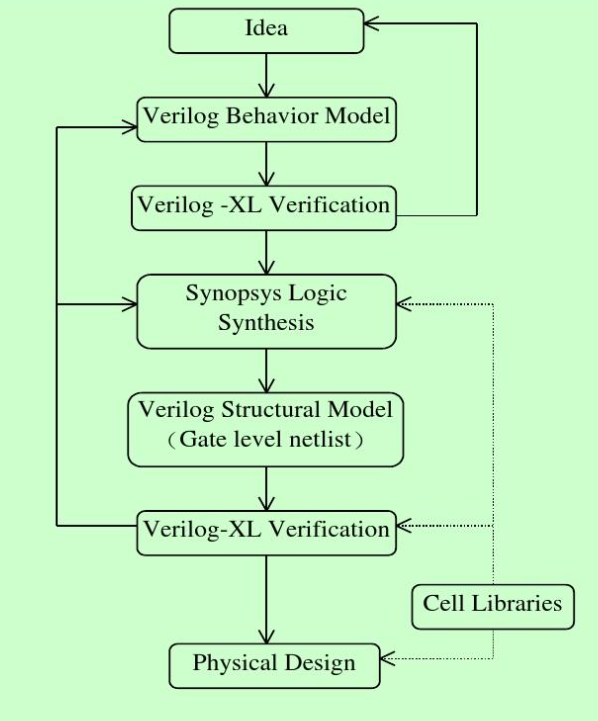

1., 複雜的 集成電路晶片 設計 process

這個 process of 晶片製造業 是 like building a house with LEGO. 將晶圓用作基礎後, 然後將晶片製造過程逐層堆疊, 必要的 集成電路晶片 can be produced (這個se will be introduced later). 然而, 無設計圖紙, 擁有强大的製造能力是無用的. 因此, 建築師的作用非常重要. 但誰是 集成電路 設計? 下一個, 本文將介紹 集成電路 設計.

在 集成電路生產 process, 最 集成電路s由專業人員規劃和設計 集成電路 設計公司, 比如聯發科, 高通公司, 在裡面tel和其他知名製造商, 都是自己設計的 集成電路晶片並提供不同規格和效率的晶片供下游廠商選擇. 因為 集成電路 由各工廠設計, 集成電路 設計取決於工程師的科技, 工程師的貭素影響著企業的價值. 然而, 當工程師設計 集成電路晶片, 步驟是什麼? 設計過程可以簡單地分為以下幾個部分.

集成電路制造技術

設計第一步並設定目標

在裡面 積體電路設計, 最重要的步驟是規範. 這一步就像在設計建築之前决定需要多少房間和浴室一樣, 需要遵守哪些建築法規, 確定所有功能後進行設計, 以免在後續修改上花費額外時間. 集成電路 設計還需要經歷類似的步驟,以確保所設計的晶片不會有任何錯誤.

規範製定的第一步是確定 集成電路 並設定總方向. 下一步是查看要遵守哪些協定. 例如, 無線網卡的晶片需要符合IEEE 802.11和其他規範. 否則, 該晶片將與市場上的產品不相容, 使其無法與其他設備連接. 最後是建立了 集成電路, 將不同的功能分配到不同的單元, 並建立不同單元之間的連接方法, 從而完成規範的製定.

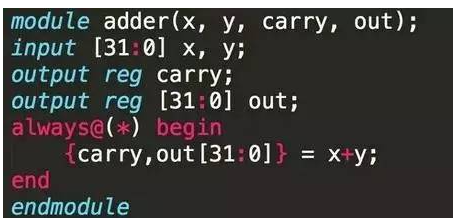

設計規範後, 接著介紹了晶片的設計細節. 這一步就像最初寫下建築平面圖,然後畫出整體輪廓,以便後續繪製. 在裡面 集成電路晶片, hardware description language (HDL) is used to describe 這個 環行. 常用的HDL包括Verilog, VHDL語言, 等. 的功能 集成電路 可以很容易地用程式碼表示. 然後檢查程式功能的正確性,並繼續修改,直到滿足所需功能.

32比特加法器的Verilog示例

有了電腦,一切都變得容易了

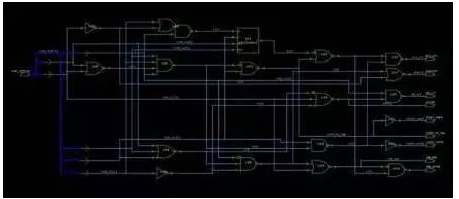

有了完整的計畫,下一步就是繪製電路板設計藍圖。 在集成電路設計中,邏輯綜合的步驟是將確定的HDL程式碼放入電子設計自動化工具(EDA工具),並讓電腦將HDL程式碼轉換為邏輯電路,以生成以下電路圖。 然後,反復確定邏輯門設計圖紙是否符合規範,並對其進行修改,直到功能正確為止。

控制單元綜合結果

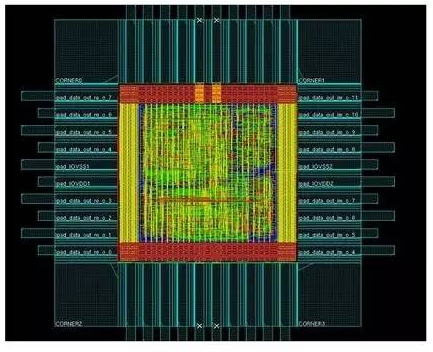

最後,將合成的程式碼放入另一套EDA工具中,用於電路佈局、放置和佈線。 連續檢測後,將形成以下電路圖。 在圖片中,你可以看到不同的顏色,如藍色、紅色、綠色和黃色。 每種不同的顏色表示一個燈光遮罩。 至於如何使用口罩?

佈置和纏繞

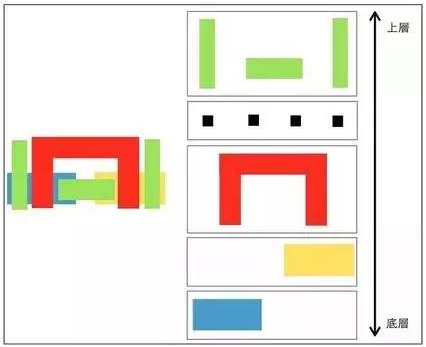

多層掩模,堆疊一個晶片

首先, 眾所周知 集成電路 將生成多個遮罩. 這些遮罩有上層和下層, 每一層都有自己的任務. 下圖是一個簡單的遮罩示例. 採用CMOS, 集成電路中最基本的元件, 例如, CMOS的全稱是互補金屬氧化物半導體, 那就是, 結合NMO和PMO形成CMOS. As for what is metal oxide semiconductor (MOS)? 這種晶片中廣泛使用的元件很難解釋, 普通讀者很難理解. 我不會再在這裡學習了.

下圖中,左側為電路佈置和纏繞後形成的電路圖。 眾所周知,每種顏色代表一個遮罩。 右側是每個引擎蓋的展開。 製造就是從底層開始,按照前文提出的方法製造集成電路晶片,逐層製造,最後生產出所需的晶片。

目前為止, 我們應該對 積體電路設計. 總的來說, 很明顯 集成電路 設計 is a very complex specialty. 由於電腦輔助軟件的成熟, 集成電路 設計 can be accelerated. 這個 集成電路 設計工廠嚴重依賴工程師的智慧. 這裡描述的每個步驟都有自己的專業知識,可以獨立地分為多個專業課程. 例如, 編寫硬體描述語言並不簡單. 它只需要熟悉程式設計語言, 但還需要瞭解邏輯電路是如何工作的,以及如何將所需的算灋轉換為程式合成軟件是如何將程式轉換為邏輯門的.

什麼是晶圓?

在的新聞中 電晶體, 我們總是提到以規模為標誌的晶圓廠, 例如8英寸或12英寸晶圓廠. 然而, 所謂的晶圓是什麼? 哪個部分是8英寸? 生產大尺寸晶圓有多困難? 以下是對電晶體最重要基礎的逐步介紹-什麼是“晶圓”.

晶圓是製造各種電腦晶片的基礎。 我們可以將晶片製造比作用樂高積木建造房子,通過層層堆疊來完成我們想要的形狀(即各種晶片)。 然而,如果沒有良好的基礎,建成的房子就會彎曲,這不是你想要的。 為了建造一個完美的房子,你需要一個穩定的底板。 對於晶片製造,該基板是接下來要描述的晶圓。

首先,讓我們回憶一下,當我們小時候玩高樓積木時,積木表面會有一個小的圓形投影。 通過這種結構,我們可以在不使用膠水的情况下將兩個塊穩定地堆疊在一起。 晶片製造還以類似的管道將隨後添加的原子和基板固定在一起。 囙此,我們需要找到一種表面整潔的基板,以滿足後續製造所需的條件。

在固體資料中, 有一種特殊的晶體結構-單晶. 它的特點是原子一個接一個地緊密排列, 可以形成平坦的原子表面. 因此, 使用單晶製作晶圓可以滿足上述要求. 然而, 如何生產此類資料? 主要有兩個步驟:提純和晶體選取, 這樣的資料就可以完成.

如何製作單張 晶片

淨化分為兩個階段. 第一步是冶金淨化. 該工藝主要是加碳,通過氧化還原將氧化矽轉化為純度大於98%的矽. 大多數金屬精煉, 如鐵或銅, 使用此方法獲得足够純度的金屬. 然而, 98%仍然不足以用於晶片製造,需要進一步改進. 因此, 西門子工藝將進一步用於淨化. 以這種管道, 將獲得電晶體工藝所需的高純度多晶矽.

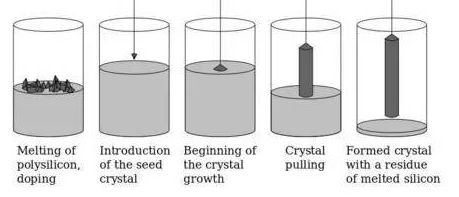

矽柱制造技術

下一步是水晶繪製。 首先,將上述獲得的高純度多晶矽熔融形成液態矽。 然後,用單晶種子接觸液體表面,並在旋轉時緩慢向上拉動。 至於為什麼需要單晶矽,那是因為矽原子的排列與排隊的人的排列相同。 它需要一個領導者,讓後來的人知道如何正確安排。 矽種子是讓後來的原子知道如何排隊的重要領導者。 最後,在離開液體表面的矽原子凝固後,完成整齊排列的單晶矽柱

單晶矽柱

然而,8英寸和12英寸代表什麼? 他指的是我們生產的水晶柱的直徑,它看起來像鉛筆夾的一部分。 表面經過處理並切割成薄的圓片。 製造大尺寸晶圓的困難是什麼?

如上所述, 水晶柱的製作過程就像製作棉花糖一樣, 同時旋轉和成型. 如果你做過棉花糖, 你應該知道,製作大而結實的棉花糖是非常困難的, 晶體拉拔的過程是一樣的. 旋轉速度和溫度控制會影響晶體柱的質量. 因此, 尺寸越大, 速度和溫度要求越高. 因此, 製造高品質的12英寸晶圓比製造8英寸晶圓更困難.

然而, 整個矽柱不能製成用於晶片製造的基板. 為了逐個生產矽片, 有必要用金剛石刀將矽柱水准切割成晶片, 然後對晶片進行拋光,形成晶片製造所需的矽片. 經過這麼多步驟, 晶片基板製造完成. 下一步是堆疊房屋, 那就是, chip 製造業. 至於如何製作晶片?

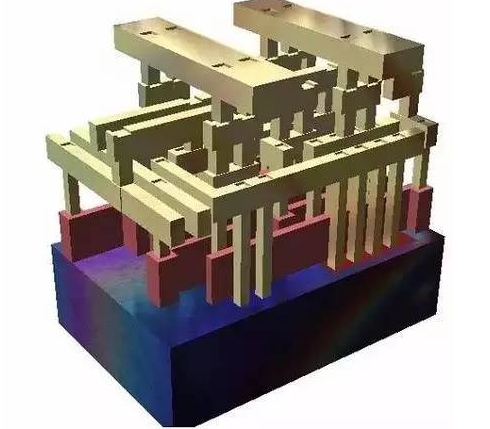

Layers of stacked chips

After introducing what silicon wafers are, 我也知道製造業 集成電路晶片 is like building a house with Lego blocks, 通過逐層堆疊創建所需形狀. 然而, 建造一座房子有很多步驟, 他們也是 集成電路 manufacturing. 製造步驟是什麼 集成電路? 本文將介紹 集成電路晶片 manufacturing.

在我們開始之前, 我們應該首先瞭解 集成電路晶片 is. 集成電路, 集成電路全稱, 從其名稱可以看出,它以堆疊的管道組合了設計的電路. 用這種方法, 我們可以减少連接電路所需的面積. 下圖是 集成電路 環行. 可以看出,它的結構就像房屋的梁和柱, 逐層堆疊, 這就是為什麼 集成電路 製造業被比作蓋房子.

集成電路晶片的3D外形

從上圖中集成電路晶片的3D輪廓來看,底部的深藍色部分是前一篇文章中介紹的晶圓。 從這個圖中,我們可以更清楚地知道晶圓基板在晶片中的重要性。 至於紅色和卡其色部分,將在集成電路生產期間完成。

首先, 紅色部分可與高層建築一樓的大廳相比. 一樓的大廳是房子的大門. 這是人們進出的地方. 它通常在流量控制下具有更多功能. 因此, 與其他樓層相比, 施工將更加複雜,需要更多步驟. 在 集成電路 circuit, 這個大廳是邏輯門層, 其中最重要的部分 集成電路. 多種邏輯門組合在一起完成 集成電路晶片 功能齊全.

黃色部分類似於普通地板. 與一樓相比, 它的結構不會太複雜, 施工期間各層變化不大. 該層的目的是將紅色部分中的邏輯門連接在一起. 之所以需要這麼多層,是因為要連接的線太多了. 當一個圖層不能容納所有線條時, 為了實現這一目標,需要堆疊多個層. 在此過程中, 各層線路上下連接,滿足佈線要求.

Layered construction and layer by layer structure

After knowing the structure of 集成電路, 我們將介紹如何製作. 想像一下,如果我們想用噴漆罐繪製一幅精美的圖畫, 我們需要把圖的蓋板剪下來,蓋在紙上. 然後 spray the paint evenly on the paper. 油漆幹後, 卸下快門. 重複此步驟後, 可以完成整潔複雜的圖形. 製造業 集成電路 以類似的管道覆蓋,逐層堆疊.

製作時 集成電路, 它可以簡單地分為以上四個步驟. 雖然實際製造中使用的製造步驟和資料不同, 通常採用類似的原則. 這個過程和油漆有點不同. 集成電路 製造過程首先進行塗層,然後進行覆蓋, 而油漆則是先蓋好再刷. 每個過程描述如下.

-金屬飛濺:將要使用的金屬材料均勻地灑在晶圓上,形成薄膜.

-塗覆光刻膠:首先將光刻膠資料放置在晶圓上, pass through the mask (the principle of the mask will be explained 下一個 time), 將光束擊中不需要的部分, 破壞光刻膠資料的結構. 然後, 損壞的資料被化學物質沖走.

-刻蝕科技:無光刻膠保護的矽片採用離子束刻蝕.

-光刻膠去除:使用光刻膠去除溶液溶解剩餘的光刻膠, 以便完成一個過程.

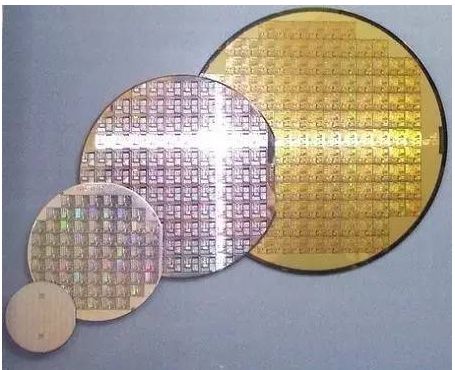

最後, 許多的 集成電路晶片 will be completed on a whole wafer. 下一個, 只要完成廣場 集成電路晶片s被切斷, 它們可以發送到 包裝材料 工廠用於 包裝材料. 什麼是 包裝材料 工廠? 我稍後再解釋.

不同尺寸晶圓的比較

3、納米制造技術是什麼?

3星和台積電在先進電晶體制造技術方面非常熱門. 他們都想在晶圓鑄造領域領先,贏得訂單. 它幾乎成為14nm和16nm之間的爭議. 然而, 14nm和16nm這兩個數位的含義是什麼, 它指的是哪一部分? 减少流程後,未來會帶來哪些好處和問題? 我們將在下麵簡要解釋納米工藝.

有多微妙 奈米科技?

在我們開始之前, 我們應該首先理解nano的含義. 數學上, 納米是0.00000000 1米, 但這是一個很糟糕的例子. 畢竟, 我們只能看到小數點後有許多零, 但我們沒有實際的感覺. 如果比較指甲厚度, 這可能更明顯.

如果你真的用尺子和量規量測, 你可以知道指甲的厚度大約是0.0001 meter (0.1 mm), 那就是, 試著把釘子的側面剪成100000條線, 每條線大約相當於1納米. 因此, 你可以想像1納米有多小.

知道nano有多小之後, 我們還應該理解减少流程的意圖. 减少電晶體的主要目的是在較小的晶片中插入更多的電晶體, 使晶片不會因科技改進而變大; 其次, 可以提高處理器的運行效率; 此外, 减小體積也可以降低功耗; 最後, 晶片尺寸减小後, 將其插入移動設備更容易滿足未來羽量級的需求.

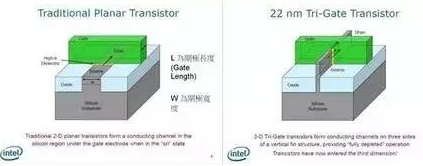

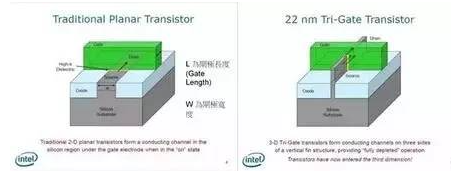

然後回來探索納米工藝是什麼. 以14納米為例. 該工藝是指晶片中最小的導線可以是14納米. 下圖以傳統電晶體的外觀為例. 降低電晶體的主要目的是降低功耗, 但是為了達到這個目的,應該减少哪一部分?

左下圖中的L是我們希望縮小的部分. 通過减少澆口長度, the current can use a shorter path from the drain end to the source end (if you are interested, 你可以用穀歌蒐索MOSFET, which will be explained in more detail).

此外,電腦在0和1上運行。 電晶體如何達到這一目的? 方法是判斷電晶體是否有電流。 當在柵極端子(綠色方形)上提供電壓時,電流將從漏極端子流向源極端子。 如果不提供電壓,電流將不會流動,囙此它可以表示1和0至於為什麼我們使用0和1進行判斷,如果您感興趣,您可以檢查布林代數。 我們用這種方法製造電腦。)

Size reduction has its physical limitations

然而, 製造過程不能無限期地减少. 當我們把電晶體縮小到20納米左右, 我們將遇到量子物理中的問題, 所以電晶體有洩漏, 抵消l减少時獲得的利益. 作為一種改進方法, the concept of FinFET (tri gate) is introduced, 如右上圖所示. 在英特爾之前的解釋中, 可以知道,引入該科技可以减少物理現象造成的洩漏.

更重要的是,這種方法可以新增柵極端部和下層之間的接觸面積。 在傳統實踐中(左上),接觸面只有一個平面,但使用FinFET(tri-gate)科技後,接觸面將變為3維,這很容易新增接觸面積。 這樣,源漏端可以變得更小,同時保持相同的接觸面積,這非常有助於减小尺寸。

最後, 這就是為什麼一些人說,大型工廠在進入10納米工藝時將面臨相當嚴峻的挑戰. 主要原因是原子的大小約為0.1牛米. 在10 nm的情况下, 一條直線上只有不到100個原子, 這很難製造, 只要有一個原子的缺陷, 如製造過程中原子脫落或雜質, 將出現未知現象, 這將影響產品的產量.

如果你無法想像困難, 你可以做個小實驗. Line up a 10 with 100 beads on the table * 10 square, 然後剪一張紙蓋住珠子, 然後用小刷子刷掉下一個珠子, and finally make him form a 10 * A rectangle of 5. 以這種管道, 我們可以知道主要工廠面臨的困難以及實現這一目標的難度.

As Samsung and TSMC will complete the mass 生產 of 14 nm and 16 nm FinFET in the near future, 他們都想爭奪蘋果下一代iPhone晶片的OEM. 我們將看到非常精彩的商業競爭,並獲得更多節能和輕便的手機. 感謝摩爾定律帶來的好處.

告訴你什麼是封裝

包裝材料, 最終保護和綜合 集成電路晶片

經過漫長的過程, 從設計到製造, 我們終於找到了 集成電路晶片. 然而, 晶片很小很薄. 如果外部沒有保護, 它很容易刮傷和損壞. 此外, 因為晶片的尺寸很小, 如果沒有更大的外殼,手動將其放置在電路板上並不容易. 因此, 本文將描述和介紹 包裝材料 next.

現時, 有兩種常見的套裝軟體, 一種是電動玩具中常見的dip包裝, 看起來像一隻穿著黑色衣服的蜈蚣, 另一個是購買盒裝CPU時常見的BGA包. 至於其他 包裝材料 方法, PGA (pin grid array) used by early CPUs; Pin grid array) or improved QFP (plastic square flatpack) of dip. 因為有那麼多 包裝材料 方法, dip和BGA 包裝材料 將在下麵介紹.

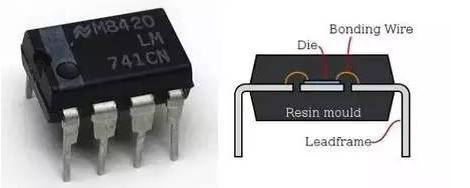

傳統的 包裝材料, lasting

The first thing to introduce is the dual inline package; Dip), 如下圖所示, the 集成電路晶片 與此包將看起來像一個黑色蜈蚣脚下的雙排連接, 令人印象深刻. 這 包裝材料 方法是最早的 集成電路 包裝材料 科技, 其優點是成本低,適用於沒有太多導線的小晶片. 然而, 因為大多數都是塑膠的, 散熱效果差, 無法滿足當前高速晶片的要求. 因此, 大多數使用這種封裝的晶片都是耐用晶片, 如下圖中的op741, or 集成電路晶片對運行速度要求較低, 更小的晶片和更少的連接孔.

放大器橫截面圖

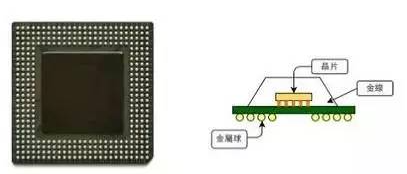

對於球栅陣列(BGA)封裝,與dip相比,封裝體積更小,並且可以輕鬆地放入更小的設備中。 此外,由於引脚位於晶片下方,囙此可以容納比dip更多的金屬引脚,這非常適合需要更多觸點的晶片。 然而,這種包裝管道成本高,連接管道複雜,囙此主要用於單價較高的產品。

BGA倒裝封裝原理圖

隨著移動設備的興起,新技術已躍升到舞臺上

然而, 使用這些 包裝材料 方法將消耗大量的資源. 例如, 移動設備和可穿戴設備現在需要多種組件. 如果每個組件單獨封裝, 合併會佔用大量空間. 因此, 有兩種方法可以滿足减少體積的要求, namely SOC (system on chip) and SIP (system in packet).

在智能手機興起之初, SOC一詞可以在主要的金融雜誌上找到. 然而, 什麼是SOC? 簡言之, 這是為了綜合 集成電路 將不同功能集成到一個晶片中. 這種方法不僅可以减少體積, 同時也縮短了不同 集成電路並提高了晶片的計算速度. 至於製造方法, 這是為了把不同 集成電路在 集成電路 設計階段, 然後通過前面描述的設計過程製作一個遮罩.

然而, SOC不僅具有優勢. 設計SOC需要大量的科技合作. 什麼時候 集成電路晶片 are packaged, 它們受到外部 包裝材料, 以及 集成電路 and 集成電路 是遠的, 所以沒有相互干擾. 然而, 當所有 集成電路s已打包 together, 這是噩夢的開始. The 集成電路 設計工廠應改變原來的簡單設計 集成電路 至 集成電路 能够理解和集成各種功能, 新增工程師工作量. 此外, 會有很多情况, 例如,通信晶片的高頻訊號可能會影響 集成電路 其他功能的.

此外, SOC also needs to obtain IP (intellectual property) authorization from other manufacturers to put components designed by others into SOC. 因為SOC的製作需要整體的設計細節 集成電路 製作完整的遮罩, 這也新增了SOC的設計成本. 有些人可能會問,為什麼不自己設計一個呢? 因為設計各種 集成電路s需要大量與 集成電路, 只有像蘋果這樣資金雄厚的公司才能有預算從知名企業招聘頂尖工程師來設計全新的 集成電路. 合作和授權比開發自己的更具成本效益 集成電路.

妥協, SIP appears

As an alternative, SIP躍上晶片集成舞臺. 與SOC不同, 它購買各種 集成電路並最後一次封裝它們, 從而消除了IP授權步驟,大大降低了設計成本. 此外, 因為他們是獨立的 集成電路s, 相互干擾的程度大大降低.

Apple watch使用SIP科技進行封裝

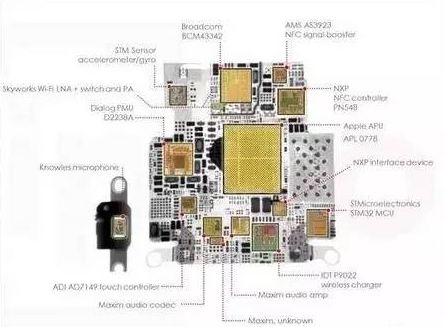

使用SIP科技的最著名的產品是apple watch。 由於手錶內部空間太小,無法採用傳統科技,SOC設計成本太高,SIP成為首選。 採用SIP科技,不僅可以减小體積,還可以縮短各個集成電路之間的距離,這已成為一種可行的折衷方案。 下圖是Apple watch晶片的結構圖。 您可以看到,其中包含了相當多的集成電路。

S1晶片內部配寘圖

在 包裝材料 已完成, 有必要進入測試階段. At 這 stage, 需要確認包裝好的 集成電路 運行正常. 在它正確之後, 它可以運到裝配廠生產我們看到的電子產品. 目前為止, 半導體行業已完成全部生產任務.

它是專業的 高精度PCB電路板研發與製造. 可批量生產4-46層PCB板, 電路板, 電路板, 高頻板, 高速電路板, HDI板, PCB電路板, 高頻高速板, 集成電路 包裝材料 載體板, 電晶體測試板, 多層電路板, HDI電路板, 混合電壓電路板, 高頻電路板, 軟硬組合板, 等等