La conception du signal LVDS sur la carte PCB n'est pas seulement un signal différentiel, mais aussi un signal numérique à haute vitesse. Par conséquent, que le support de transmission LVDS utilise un fil ou un câble de carte PCB, il est essentiel de prendre des mesures pour empêcher la réflexion du signal sur le terminal du support et réduire les interférences électromagnétiques pour assurer l'intégrité du signal. Tant que nous prenons en compte ces éléments lors du câblage, il n'est pas très difficile de concevoir une carte de circuit différentiel à haute vitesse. Voici un bref aperçu de la conception des signaux LVDS sur une carte PCB: 2.1 disposition des signaux LVDS en une carte multicouche une carte avec des signaux LVDS est généralement disposée en une carte multicouche. Étant donné que le signal LVDS est un signal à grande vitesse, les couches adjacentes devraient être des couches de terre pour masquer le signal LVDS contre les interférences. Pour les plaques de faible densité, les signaux LVDS et autres signaux sont placés sur différentes couches si les conditions spatiales physiques le permettent. Par example, dans un panneau à quatre couches, les couches peuvent généralement être agencées de la manière suivante: couche de signal LVDS, couche de terre, couche d'alimentation et autres couches de signal. 2.2 calcul et contrôle de l'impédance du signal LVDS. Le signal LVDS a une oscillation de tension de seulement 350mv, ce qui est approprié pour un fonctionnement de signal différentiel commandé par courant. Pour s'assurer que le signal n'est pas affecté par le signal réfléchi lorsqu'il se propage sur la ligne de transmission, le signal LVDS doit contrôler l'impédance de la ligne de transmission, l'impédance différentielle étant typiquement de 100 + / - 10°. La qualité du contrôle d'impédance affecte directement l'intégrité et le retard du signal.

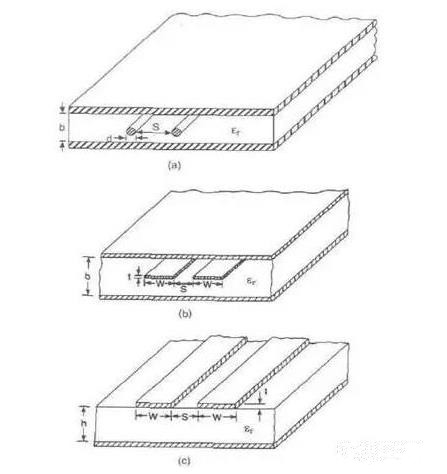

1. Comment contrôler son impédance de carte PCB? 1.1 déterminer le mode de câblage, les paramètres et le calcul de l'impédance. LVDS est divisé en mode différentiel de ligne microruban externe et mode différentiel de ligne ruban interne. L'impédance peut être calculée en définissant raisonnablement les paramètres et en utilisant le logiciel associé. Par calcul, les valeurs d'impédance sont directement proportionnelles à l'épaisseur de la couche isolante et inversement proportionnelles à la constante diélectrique, à l'épaisseur et à la largeur du fil. 1.2 Les principes de lignes parallèles équidistantes et de couplage serré sont respectés. Après avoir déterminé la largeur et l'espacement des lignes, le câblage se fait strictement selon la largeur et l'espacement calculés et l'espacement entre les deux lignes doit toujours être constant, c'est - à - dire qu'il doit être parallèle (des images peuvent être placées). Simultanément, dans le calcul de la largeur et de l'espacement des lignes, on observe le principe du couplage serré, c'est - à - dire que l'espacement des paires différentielles est inférieur ou égal à la largeur des lignes. Lorsque les deux lignes de signal différentiel sont très proches, le sens de transmission du courant est inversé, les champs magnétiques s'annulent, les champs électriques sont couplés et le rayonnement électromagnétique est beaucoup plus faible. De plus, les deux fils doivent être sur la même couche pour éviter le câblage en couches. En effet, dans l'usinage proprement dit d'une plaque PCB, le degré de laminage entre empilements est bien inférieur à la précision de gravure de cette même couche et les pertes diélectriques lors du laminage ne garantissent pas que la distance entre les lignes différentielles soit égale à l'épaisseur du diélectrique inter - couches, Il en résultera une variation d'impédance différentielle des paires différentielles entre les couches.

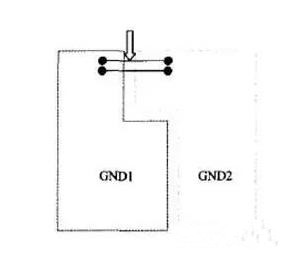

1.3 courte et rapide. Pour assurer la qualité du signal, les traces de paire différentielle LVDS doivent être aussi courtes et droites que possible, réduire le nombre de trous dans le câblage et éviter le câblage de paire différentielle trop long et le nombre excessif de tours. Essayez d'utiliser 45 ° ou un arc de cercle dans les coins. Évitez les virages à 90°. Il n'y a aucune restriction sur le choix de la méthode de routage LVDS entre les différentes paires de lignes différentielles. Les lignes microruban et ruban peuvent être utilisées, mais il faut veiller à avoir un bon plan de référence. L'espacement entre les différentes lignes de différence ne doit pas être trop petit, au moins 3 à 5 fois l'espacement des lignes de différence. Si nécessaire, ajoutez une isolation des trous de terre entre les différentes paires de lignes différentielles pour éviter toute diaphonie mutuelle. Gardez le signal LVDS aussi loin que possible des autres signaux. Les signaux différentiels LVDS ne peuvent pas être divisés entre les plans. Bien que ces deux signaux différentiels soient des trajets de retour l'un vers l'autre, la Division croisée ne coupe pas le retour du signal, mais la ligne de transmission traversant la Division entraînerait une discontinuité d'impédance due à l'absence de plan de référence (comme représenté sur la figure où gnd1 et gnd2 sont adjacents au plan de masse LVDS). La distance entre la résistance adaptée à l'extrémité de réception et la broche de réception doit être aussi proche que possible. Dans le même temps, la précision de la résistance adaptée doit être contrôlée. Pour les topologies point à point, l'impédance des traces est généralement contrôlée à 100 îles, mais la résistance d'adaptation peut être ajustée en fonction de la situation réelle. Le degré de résistance est de 1 à 2%. Car, par expérience, une désadaptation d'impédance de 10% produirait une réflexion de 5%.

Analyse de simulation du signal LVDS série ce qui précède analyse les éléments à prendre en compte lors de la conception du signal LVDS. Bien que les règles ci - dessus soient généralement suivies dans le processus de conception de PCB, pour améliorer l'exactitude et la précision de la conception, une simulation complète du signal du PCB par simulation est nécessaire. Obtenez la diaphonie, le retard, la réflexion et la forme d'onde de l'oculogramme du signal pour atteindre le but de la conception correcte. Le processus de simulation d'un problème d'intégrité du signal consiste d'abord à établir un modèle de simulation du composant, puis à effectuer une pré - simulation pour déterminer les paramètres et les contraintes du processus de câblage. La phase de mise en œuvre physique est conçue en fonction des contraintes et une post - simulation est effectuée pour vérifier la conformité de la conception aux exigences de conception. La nature du modèle tout au long du processus influe directement sur les résultats de la simulation, et les méthodes d'analyse de simulation utilisées dans les phases pré et post - simulation sont également essentielles pour les résultats de la simulation, avec un degré plus élevé de modèle Spice utilisé dans cette conception. Ce qui suit illustre le processus d'implémentation simulé dans cette conception en combinaison avec des projets réels. 2.1 configuration de l'empilement de la carte PCB l'analyse ci - dessus montre que la configuration de l'empilement de la carte PCB est étroitement liée au couplage du signal et au calcul de l'impédance. Par conséquent, la conception de l'empilement doit être effectuée avant la conception de la carte PCB, puis le calcul de l'impédance du signal est effectué. 2.2 réglage de la valeur de la tension continue cette étape consiste principalement à spécifier la valeur de la tension continue de certains réseaux spécifiques (généralement une alimentation à la terre, etc.), à déterminer la tension continue à appliquer au réseau, Et effectuer une simulation EMI nécessite de déterminer une ou plusieurs broches de source de tension. Ces valeurs de tension comprennent des informations sur la tension de référence utilisée par le modèle lors de la simulation. 2.3 réglage de l'appareil lors de la simulation Allegro, Allegro classe les appareils en trois catégories: les circuits intégrés, les connecteurs et les appareils discrets (condensateurs résistifs, etc.), Allegro répartira les attributs analogiques en fonction des broches du type d'appareil, Les propriétés des broches des dispositifs discrets et des connecteurs sont upspec et les propriétés des broches des circuits intégrés peuvent être in, out, bi, etc. 2.4 affectation de modèles les principaux modèles utilisés dans le processus de simulation de carte PCB haute vitesse au niveau de la carte sont le modèle de dispositif et le modèle de ligne de transmission. Le modèle de l'appareil est généralement fourni par le fabricant de l'appareil. Pour les signaux série à grande vitesse, nous avons utilisé le modèle Spice avec une plus grande précision pour l'analyse de simulation. Le modèle de ligne de transmission est formé par modélisation logicielle de simulation. Lorsqu'un signal est transmis, la ligne de transmission met en évidence les problèmes d'intégrité du signal, de sorte que la capacité du logiciel de simulation à modéliser la ligne de transmission influe directement sur les résultats de la simulation. 2.5 vérification de l'is la fonction de vérification de l'is permet de vérifier si un réseau particulier ou un groupe de réseaux peut être extrait pour analyse. En règle générale, nous devons faire attention à la mise en place d'un réseau à haut débit. Cette conception vise principalement les signaux série LVDS. 2.6 topologie du réseau d'extraction la topologie du signal d'intérêt est extraite de la carte PCB, qui comprend généralement une extrémité pilote et une extrémité de réception, ainsi que des lignes de transmission et des résistances et condensateurs adaptés associés. Comme on peut le voir à partir de la topologie, le réseau passe par ces chemins, ce qui entraîne des effets sur la transmission du signal. Cet article ne prend comme exemple qu'un diagramme de topologie de réseau pour l'un des signaux: Comme dans la figure 4: 2.7, une fois que la forme d'onde a été configurée avec les étapes pertinentes ci - dessus, la simulation est prête. Allegro peut effectuer des simulations de réflexion du signal et des simulations de diaphonie, et les lignes différentielles nécessitent également une analyse de diagramme oculaire. Bien sûr, la simulation est également divisée en pré - simulation et post - simulation. Lors de la conception de cartes PCB avec Allegro, la conception doit être modifiée en temps réel pour répondre aux exigences en fonction des résultats de simulation. Parce que le processus de simulation est complexe et que les étapes sont fastidieuses, je ne les décrirai pas toutes. Il y a deux points à noter dans le câblage des paires différentielles. L'une est que la longueur des deux lignes doit être aussi longue que possible, tandis que des longueurs égales sont nécessaires pour s'assurer que les deux signaux différentiels restent toujours opposés. Polarité pour réduire la composante de mode commun. L'autre est que la distance entre les deux lignes (cette distance étant déterminée par l'impédance différentielle) doit toujours être constante, c'est - à - dire qu'elle doit rester parallèle. Il y a deux façons parallèles, l'une où deux fils circulent côte à côte sur la même couche, et l'autre où ces deux fils circulent sur deux couches adjacentes, supérieure et inférieure (supérieure et inférieure). En général, le premier a plus d'implémentations parallèles. L'équidistance vise principalement à assurer la même impédance différentielle entre les deux et à réduire la réflexion. Les méthodes de câblage des paires différentielles doivent être convenablement proches et parallèles. Une proximité dite appropriée est due au fait que cette distance affecte la valeur de l'impédance différentielle, qui est un paramètre important dans la conception d'une paire différentielle. Le parallélisme est également nécessaire pour maintenir la cohérence de l'impédance différentielle. Si les deux lignes sont soudainement proches et éloignées, l'impédance différentielle ne sera pas cohérente, ce qui affectera l'intégrité du signal et le retard temporel. A partir d'un diagramme simulé de paramètres S, il est possible d'analyser l'impédance différentielle et l'intégrité du signal d'une paire différentielle. Les formes d'onde analogiques des signaux clés dans cette conception sont présentées ci - dessous pour illustration. Comme on peut le voir sur la figure 5 de la légende de simulation, l'indice de dégradation de S11 dans le domaine de fréquences 0 - 3,0 GHz est le suivant: