Aujourd'hui, la technologie CMOS permet aux appareils FPGA d'avoir plusieurs interfaces E / S. Dans le même temps, ces dernières années, la faible consommation d'énergie a commencé à devenir le concept dominant des interfaces d'E / s haute vitesse. Le moyen le plus efficace de réduire la consommation d'énergie est de réduire la tension, tandis qu'une diminution de la tension entraînera une moindre tolérance au bruit permise par l'interface E / S. Il est donc très important pour les utilisateurs de FPGA de quantifier le bruit de commutation synchrone (SSN) au niveau du système dans les environnements de puce, d'encapsulation et de PCB.

Cet article présente systématiquement le SSN, en mettant l'accent sur le SSN causé par la mise en mémoire tampon de sortie FPGA. Ce bruit est souvent appelé bruit de sortie de commutation synchrone (SSO) et est différent du SSN causé par le tampon d'entrée. Cet article décrit les raisons de la génération de SSO au niveau du système et propose une approche hiérarchique de la modélisation de SSO au niveau du système. Dans le même temps, cet article explique également comment associer un modèle SSO à des mesures dans le domaine fréquentiel et temporel, et donne plusieurs méthodes de conception de PCB pour réduire le SSO.

Mécanisme de formation des SSO au niveau du système

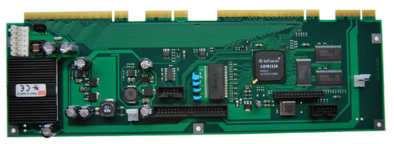

Un circuit imprimé avec FPGA est un système complexe qui peut être divisé en une partie de la puce contenant le circuit actif, une partie d'encapsulation avec des éléments passifs embarqués supportant les traces et une partie de la carte qui fournit la connexion du FPGA à l'extérieur. Dans ce type de système, il est difficile de comprendre les caractéristiques de bruit à l'intérieur de la puce. Il est donc très intéressant de quantifier le SSO aux extrémités proximale et distale des pistes PCB connectées au FPGA. Deux facteurs principaux contribuent au SSO: l'impédance du réseau de distribution (PDN) et le couplage inductif mutuel entre les interrupteurs I / O.

Du point de vue du système, le PDN comprend des composants au niveau de la plaquette, de l'encapsulation et de la carte qui, ensemble, alimentent le circuit CMOS. Lorsqu'un certain nombre de circuits de commande de sortie CMOS sont simultanément conducteurs, un courant important circulera instantanément dans les éléments du circuit inductif du PDN, provoquant une chute de tension delta - I. La structure d'interconnexion génère des inductances parasites, telles que des billes de soudage de puissance sur un boîtier à grille à billes et des trous de puissance dans le PCB. Ce courant à variation rapide excite également les ondes électromagnétiques radiales entre les couples puissance / plan de masse. Les ondes électromagnétiques sont réfléchies par les bords plans du PCB, créant une résonance entre le plan d'alimentation / masse et provoquant des fluctuations de tension.

Une autre raison importante pour SSO est le couplage inductif mutuel, en particulier autour de l'encapsulation de la puce / bord du PCB. Les billes de soudure sur le boîtier BGA de la puce et les trous sur le PCB appartiennent à une structure multifilaire étroitement couplée. Chaque bille de soudage d'E / s et son perçage PCB correspondent, ainsi que ses billes de soudage de terre et ses perçages de terre les plus proches, forment une boucle fermée. Lorsque l'état de plusieurs ports d'E / s change simultanément, un courant d'E / s transitoire circule dans ces boucles de signal. Ce courant d'E / s transitoire va générer un champ magnétique variable dans le temps qui envahit les boucles de signal adjacentes et provoque un bruit de tension induit.

Un excellent modèle SSO devrait être capable de refléter les mécanismes de formation de base du SSO. Modèle hiérarchique utilisé pour prédire le SSO dans un PCB. Au niveau de la puce, ce dont nous avons besoin est un modèle de tampon de sortie qui peut fournir une distribution de courant précise sur les lignes d'alimentation et de signal de complexité limitée. Au niveau de l'encapsulation, des outils de modélisation peuvent être utilisés pour obtenir le modèle PDN et le modèle de couplage du signal par souci de simplicité, mais l'interaction entre le modèle PDN et le modèle de couplage du signal doit être soigneusement examinée. Ces deux modèles agissent comme des ponts reliant le modèle tampon de sortie à l'extrémité de la bosse d'encapsulation de la puce et le modèle de niveau PCB à l'extrémité de la bille de soudage. Le modèle PDN d'un PCB comprend généralement un plan d'alimentation / masse et des condensateurs de grande capacité / découplage sur celui - ci, tandis que le modèle de couplage de signal d'un PCB comprend un réseau de trous croisés étroitement couplés et des traces de signal faiblement couplées sur différentes couches de signal. Les effets interactifs de ces deux modèles de niveau PCB apparaissent dans le PCB par le biais de tableaux. C'est à partir de là que la diaphonie inductive introduit le bruit dans le modèle PDN, tandis que le bruit delta - I réduit à son tour la qualité du signal d'E / S. Cette méthode de modélisation par couches préserve raisonnablement la précision de la simulation tout en améliorant l'efficacité de calcul de tels systèmes complexes.