La tecnica di tagliare singole unità dai wafer e poi confezionarle è stata a lungo la norma per il confezionamento dei circuiti integrati a semiconduttori per decenni. Tuttavia, questo approccio non è attualmente adottato dai principali produttori di semiconduttori a causa degli elevati costi di produzione e della crescente componente RF dei moduli odierni. Pertanto, l'emergere di imballaggi a livello di wafer (WLP) ha portato a un cambiamento di paradigma nello sviluppo di imballaggi a basso costo. WLP è una tecnologia di imballaggio a livello wafer prima del taglio dei dispositivi di imballaggio wafer.

Utilizzando strumenti e processi standard, WLP funge da estensione del processo di produzione dei wafer. Alla fine, il WLP DIE fabbricato avrà un pad metallizzato sulla superficie del chip e un punto di saldatura depositato su ogni pad prima di tagliare il wafer. Questo, a sua volta, rende WLP compatibile con i tradizionali processi di assemblaggio PCB e consente di testare il dispositivo sul wafer stesso. Di conseguenza, si tratta di un processo relativamente economico ed efficiente, soprattutto quando la dimensione del wafer aumenta e il chip DIE si restringe. Le dimensioni dei wafer sono aumentate negli ultimi decenni, da 4, 6 e 8 pollici di diametro a 12 pollici. Ciò si traduce in un aumento del numero di DIE per wafer, che riduce i costi di produzione. In termini di prestazioni elettriche, WLP è superiore ad altre tecnologie di imballaggio, nel senso che una volta integrato un dispositivo WLP in un modulo RF denso, si traduce in una significativa riduzione dell'accoppiamento parassitario EM perché l'interconnessione tra il dispositivo e il PCB è relativamente breve, a differenza dell'interconnessione cablata utilizzata in alcuni tipi di tecnologie CSP.

Tecnologia WLP chip flip-chip

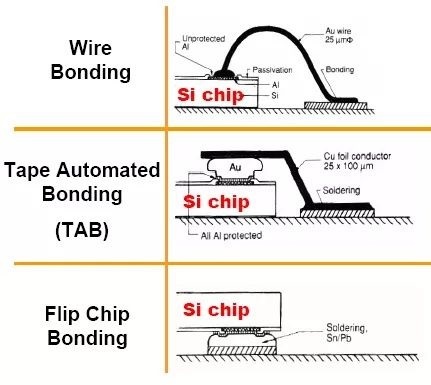

La tecnologia Flip-chip, nota anche come Controlled Collapse Chip Connection (C4), è una delle numerose tecnologie di assemblaggio dei chip sviluppate da IBM negli anni '60. Sebbene la tecnologia di imballaggio basata sull'incollaggio del filo sia più flessibile in termini di capacità induttiva libera per il debug di laboratorio dopo la costruzione dell'hardware e fornisca anche una buona conducibilità termica, l'uso di rigonfiamenti della saldatura nella tecnologia di imballaggio flip-chip rende la connessione elettrica tra il substrato del pacchetto e il chip fornisce la riduzione delle dimensioni relative, la latenza ridotta, e migliore isolamento in termini di input e output pin. La figura 1 illustra la struttura di base del chip DIE sul substrato, con una palla di saldatura nella parte superiore della colonna Cu che cresce sulla superficie del chip. Il giunto di saldatura è solitamente incapsulato con un composto di stampo di riempimento per fornire supporto meccanico per il giunto di saldatura.

Pacchetto di livello del chip WLP

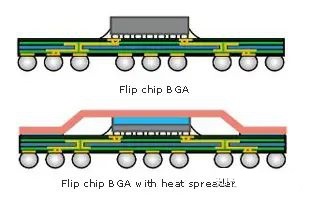

Il chip scale packaging (CSP) è uno dei metodi di imballaggio più comunemente utilizzati nell'industria della microelettronica e dei semiconduttori. Mentre diversi tipi di tecnologie CSP sono già disponibili per i produttori di microchip, nuovi tipi continuano ad emergere per soddisfare la domanda di prodotti che supportano nuove funzionalità e nuovi prodotti specifici per le applicazioni. Questi requisiti di imballaggio possono variare a seconda del livello richiesto di affidabilità, costo, caratteristiche aggiuntive e dimensioni complessive. Come suggerisce il nome, la dimensione del pacchetto del CSP è approssimativamente la stessa della dimensione del chip DIE, che è uno dei suoi principali vantaggi. Adottando il processo di produzione WLP, CSP è costantemente sviluppato per ottenere il più piccolo rapporto formato pacchetto-dado possibile. Come mostrato nella Figura 2, lo stile BGA (Ball Grid Array) di CSP nel pacchetto consente diverse interconnessioni semplificando il cablaggio PCB, aumentando la produttività di assemblaggio PCB e riducendo i costi di produzione.

Altre tecnologie di incapsulamento

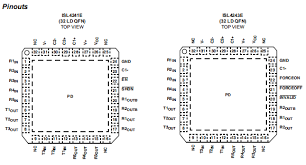

Esistono diverse altre forme di imballaggio integrato IC che consentono l'integrazione senza soluzione di continuità in pacchetti di moduli personalizzati per applicazioni. Quad Flat Package (QFP) è una delle prime tecnologie del pacchetto IC di montaggio superficiale, dove la struttura del pacchetto è composta da quattro lati con cavi di interconnessione estesi, come mostrato nella Figura 3 (a). I cavi sollevati sono collegati al telaio del pacchetto per formare un condensatore di tipo metallo-isolante-metallo (MIM) tra i cavi e il chip DIE metallo, che può essere utilizzato come elemento di corrispondenza. Questa tecnica è adatta per IC di dimensioni millimetriche in cui il numero di pin periferici nella confezione può raggiungere più di 100 pin. Esistono diversi derivati di questo tipo di incapsulamento, a seconda del materiale utilizzato, come ad esempio la confezione piatta in ceramica quad, la confezione piatta sottile quad, la confezione piatta in plastica quad, la confezione piatta in plastica Quad) e la confezione piatta in metallo Quad (MQFP). Il QFN, Quad Flat No Lead, mostrato in Fig. 3(b) è una delle numerose tecnologie di imballaggio a superficie formate da un telaio piatto in piombo di rame e da un pacchetto di plastica utilizzato come pad di trasferimento termico per il radiatore. L'incollaggio del filo può essere utilizzato anche per le interconnessioni e poiché le linee di legame non sono solo conduttori, ma anche induttori, generalmente influenzano le prestazioni dei dispositivi sotto questa tecnica di incapsulamento, a meno che non sia considerato parte della progettazione generale. Sebbene il QFN sia un'interconnessione composta da quattro lati, sono apparsi anche i cavi non collegati biplane (DFN) che formano entrambi i lati dei cavi piani di interconnessione.