Oltre ai processi avanzati, l'imballaggio avanzato è diventato una tecnologia chiave per continuare la Legge di Moore. Tecnologie come 2.5D, 3D e Chiplets sono diventate temi caldi nel settore dei semiconduttori negli ultimi anni. In che modo, esattamente, il packaging avanzato gioca un ruolo chiave nel portare avanti la legge di Moore? Quali sono le caratteristiche delle tecnologie di imballaggio come 2.5D, 3D e Chiplets?

Intelligenza artificiale (AI), Internet of Vehicles, 5G e altre applicazioni sono emerse e tutte hanno bisogno di utilizzare chip funzionali avanzati con calcolo ad alta velocità, trasmissione ad alta velocità, bassa latenza e basso consumo energetico. Tuttavia, poiché la domanda di calcolo cresce più volte, come continuare la legge di Moore è una sfida per l'industria dei semiconduttori.

Man mano che la microscala del chip diventa più difficile, nasce un'integrazione eterogenea.

In altre parole, i processi avanzati a semiconduttore si muovono in 7 nm, 5 nm e poi 3 nm e 2 nm. Le dimensioni dei transistor si stanno quindi avvicinando ai limiti fisici del volume degli atomi. Anche le limitazioni elettroniche e fisiche rendono sempre più difficile per i processi avanzati continuare a ridursi e aggiornare.

Di conseguenza, oltre a continuare a sviluppare processi avanzati, l'industria dei semiconduttori sta anche cercando altri modi per mantenere i chip piccoli ed efficienti. Il layout Design dei chip diventa quindi una nuova soluzione per continuare la Legge di Moore, e il concetto di Heterogeneous Integration Design Architecture System (HIDAS) nasce nel momento storico e diventa lo slancio innovativo di ICchips.

La cosiddetta integrazione eterogenea, in generale, è l'integrazione di due chip diversi, come memoria + chip logico, componenti fotoelettrici + elettronici, ecc., attraverso packaging, stack 3D e altre tecnologie. In altre parole, l'integrazione di due chip con processi diversi e proprietà diverse può essere chiamata integrazione eterogenea.

Poiché il mercato delle applicazioni è più diversificato, i costi, le prestazioni e la popolazione target di ciascun prodotto sono diversi, quindi anche la tecnologia di integrazione eterogenea richiesta è diversa e la tendenza di focalizzazione del mercato emerge gradualmente. Pertanto, l'industria di fonderia IC, produzione e apparecchiature a semiconduttore hanno investito nello sviluppo eterogeneo dell'integrazione, 2.5D, imballaggio 3D, chip e altre tecnologie di imballaggio popolari, si basa sull'idea di integrazione eterogenea, come germoglio di bambù dopo una primavera primaverile.

L'imballaggio 2.5D riduce efficacemente il costo della produzione di chip

In passato, per integrare insieme i chip, la maggior parte dell'utilizzo della tecnologia System in a Package (SiP), come il confezionamento PiP (Package in Package), il confezionamento PoP (Package on Package). Tuttavia, come smartphone, AIoT e altre applicazioni, non solo hanno bisogno di prestazioni superiori, ma anche per mantenere una dimensione ridotta, basso consumo energetico, in tal caso, dobbiamo trovare un modo per impilare più chip per ridurre il volume, quindi, l'attuale tecnologia di imballaggio oltre al SiP originale, ma anche verso lo sviluppo della tecnologia di imballaggio tridimensionale.

In poche parole, imballaggio tridimensionale significa utilizzare l'interposer al silicio (interposer al silicio) realizzato direttamente da wafer al silicio, piuttosto che utilizzare il precedente "supporto metallico" in plastica, e confezionare diversi chip con funzioni diverse direttamente in un chip più efficiente. In altre parole, aggiungendo chip di silicio sopra al silicio, in un modo che aumenta i costi e i vincoli fisici del processo, mantiene viva la Legge di Moore.

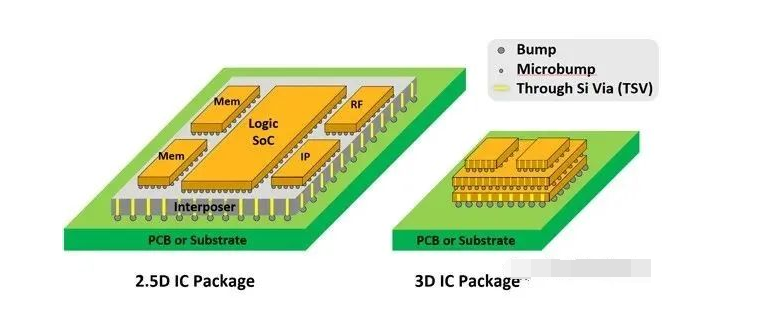

E il pacchetto stereoscopico è più familiare con il pacchetto 2.5D e 3D, qui partiamo dal pacchetto 2.5D. Il cosiddetto pacchetto 2.5D, il concetto principale è quello di disporre processori, memoria o altri chip sul Silicon Interposer (Silicon Interposer), che è collegato da Micro Bump, in modo che i fili metallici all'interno del Silicon Interposer possano collegare i segnali elettronici di chip diversi. Quindi, il TSV viene utilizzato per collegare il Bump metallico inferiore e la piastra portante del filo viene utilizzata per collegare la sfera metallica esterna per ottenere un'interconnessione più stretta tra il chip, il chip e il substrato dell'imballaggio.

2.5D e gli imballaggi 3D sono tecnologia di imballaggio stereo popolare. (Fonte: ANSYS)

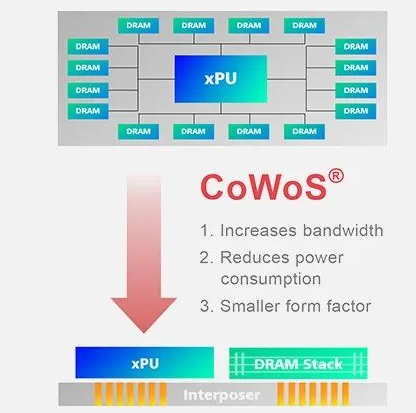

La tecnologia di imballaggio 2.5D che è ben nota al momento non è altro che CoWoS di TSMC. Il concetto della tecnologia CoWoS è quello di mettere insieme chip semiconduttori (come processori, memoria, ecc.) sullo strato intermedio di silicio, e quindi collegarli al substrato inferiore attraverso il processo di confezionamento di Chip on Wafer (CoW). In altre parole, il Chip viene prima collegato al Wafer di silicio attraverso il processo di confezionamento di Chip on Wafer (CoW), quindi il Chip CoW è collegato al substrato e integrato in CoWoS. Utilizzando questa modalità di imballaggio, i chip multipli possono essere imballati insieme e interconnessi attraverso Si Interposer per ottenere l'effetto di piccolo volume di imballaggio, basso consumo energetico e meno pin.

TSMC CoWos concetto di tecnologia di imballaggio. (Fonte: TSMC)

Oltre ai CoWos, l'imballaggio a livello di wafer ventilato può anche essere classificato come metodo di imballaggio 2.5D. Il principio dell'imballaggio a livello di wafer fan-out è quello di estrarre i circuiti richiesti dalle estremità del semiconduttore nudo allo strato di ridistribuzione per formare l'imballaggio. Pertanto, non c'è bisogno di sigillare la piastra di carico, cavo, bump, che può ridurre il costo di produzione del 30%, e anche rendere il chip più sottile. Allo stesso tempo, l'area del chip può essere ridotta molto. Può anche sostituire il costo più elevato della perforazione in silicio, per raggiungere l'obiettivo di integrare diversi componenti attraverso la tecnologia di imballaggio.

Naturalmente, la tecnologia di imballaggio stereo non è solo 2.5D, c'è anche il packaging 3D. Quindi, qual è la differenza tra i due e l'industria SEMICONDUCTOR sta adottando il packaging 3D?

A differenza del pacchetto 2.5D, il pacchetto 3D funziona creando una struttura a transistor (CMOS) sul chip e utilizzando perforazioni di silicio per collegare i segnali elettronici di chip diversi sopra e sotto, in modo che la memoria o altri chip possono essere direttamente impilati verticalmente sul chip.

Il packaging 3D è una pila diretta di chip. (Fonte: Intel)

TSMC e Intel sviluppano attivamente la tecnologia di imballaggio 3D

Intel (INTC) e Taiwan Semiconductor (TSMC) hanno le proprie tecnologie per il packaging 3D. Intel utilizza la tecnologia di imballaggio 3D "Foveros", che utilizza una logica di stack eterogenea per gestire le operazioni e può impilare ogni chip logico insieme. Ciò significa, per la prima volta, estendere il chip stacking dai tradizionali mediatori passivi in silicio e memoria impilata a prodotti logici ad alta efficienza come CPU, processori grafici e AI. In passato, l'stacking era utilizzato solo per la memoria, ma ora l'stacking eterogeneo è utilizzato per consentire l'impilamento di diverse combinazioni di memoria e chip di calcolo.

Inoltre, Intel sta sviluppando tre nuove tecnologie, vale a dire co-EMIB, ODI e MDIO. Co-emib può connettersi con prestazioni e capacità di calcolo superiori e consentire l'interconnessione di due o più componenti Foveros. I progettisti possono anche collegare simulatori, memoria e altri moduli ad altissima larghezza di banda e a bassissimo consumo energetico. La tecnologia ODI offre una maggiore flessibilità per la comunicazione omnidirezionale di interconnessione tra chip di piccole e medie dimensioni. Il chip superiore può comunicare con altri piccoli chip come la tecnologia EMIB e può comunicare verticalmente con il chip nudo inferiore sottostante attraverso un foro di silicio (TSV) come la tecnologia Foveros.

Concetto di tecnologia Intel Foveros. (Fonte: Intel)

La tecnologia utilizza anche grandi fori passanti verticali che forniscono energia direttamente dal substrato dell'imballaggio alla piastra nuda superiore. Questi grandi fori passanti sono molto più grandi dei tradizionali fori passanti in silicio e forniscono una trasmissione di potenza più stabile con una resistenza inferiore. E attraverso lo stack per ottenere maggiore larghezza di banda e minore latenza. Questo approccio riduce il numero di fori di silicio necessari nel chip di base, liberando più area per l'elemento attivo e ottimizzando la dimensione del foglio nudo.

TSMC, invece, propone una soluzione di integrazione "3D multi-chip and system integrated chip" (SoIC). La soluzione on-chip integrata nel sistema combina cristalli nudi noti di diverse dimensioni, tecnologie di processo e materiali direttamente l'uno sopra l'altro.

TSMC osserva che i chip integrati del sistema hanno densità e velocità di urto diverse volte superiori, riducendo significativamente il consumo energetico, rispetto alle tradizionali soluzioni di circuito integrato 3D che utilizzano microbump. Inoltre, i chip integrati nel sistema sono soluzioni integrate pre-processo che collegano due o più cristalli nudi prima del confezionamento; Di conseguenza, il chipset Integration di sistema può sfruttare la tecnologia di imballaggio avanzata InFO o CoWoS dell'azienda per integrare ulteriormente altri chip, creando una robusta soluzione a livello di sistema "3D*3D".

Inoltre, TSMC ha lanciato 3DFabric, che riunisce le soluzioni di integrazione di sistema 3DIC in rapida crescita per offrire maggiore flessibilità e creare sistemi potenti con una robusta interconnessione on-chip. Con diverse opzioni per l'impilamento dei chip anteriori e il confezionamento dei chip posteriori, 3DFabric aiuta i clienti a collegare più chip logici insieme, anche a memoria larga tandem ad alta frequenza (HBM) o a piccoli chip eterogenei come moduli analogici, INPUT/output e rf. 3DFabric combina soluzioni 3D anteriori e posteriori e integra miniature transistor per migliorare continuamente le prestazioni e le funzionalità del sistema, ridurre le dimensioni e l'aspetto e accelerare il time-to-market del prodotto.

Dopo aver introdotto 2.5D e 3D, Chiplets è una delle più recenti tecnologie di imballaggio avanzate per colpire l'industria dei semiconduttori. Infine, una breve descrizione delle caratteristiche e dei benefici dei Chiplets.

Ci sono tre vantaggi nell'usare Chiplets. Poiché il costo del processo avanzato è molto alto, in particolare il circuito analogico e I / O stanno diventando sempre più difficili da restringere con la tecnologia di processo. I chip dividono il circuito in piccoli chip indipendenti, rafforzano le loro funzioni, la tecnologia di processo e le dimensioni, e infine li integrano insieme per superare la sfida della miniaturizzazione del processo. Inoltre, i chip possono anche utilizzare chip maturi esistenti per ridurre i costi di sviluppo e verifica.

Attualmente, molti produttori di semiconduttori hanno introdotto prodotti ad alte prestazioni nel modo dei chip. Ad esempio, Intel Stratix 10 GX 10m FPGA è progettato con chip per ottenere una maggiore densità e capacità dei componenti. Basato sull'architettura Intel Stratix 10 FPGA esistente e sulla tecnologia avanzata di interconnessione multi chip embedded Intel (emib), il prodotto utilizza la tecnologia emib per integrare due chip logici core Intel Stratix 10 GX FPGA ad alta densità e corrispondenti unità I / O. Lo stesso vale per i processori della serie epyc di seconda generazione AMD. Diverso dalla prima generazione di metodo chip che combina memoria e I / O per formare una CPU 14 nm, la seconda generazione è quella di separare I / O e memoria in un chip, e tagliare la CPU 7 nm in 8 chip per combinazione.

In una parola, in passato, l'efficienza del chip è stata migliorata dal miglioramento del processo a semiconduttore, ma man mano che la dimensione del componente si avvicinava al limite fisico, la miniaturizzazione del chip è diventata sempre più difficile. Per mantenere la progettazione del chip di piccole dimensioni e ad alta efficienza, l'industria dei semiconduttori non solo ha continuato a sviluppare processi avanzati, ma ha anche migliorato l'architettura del chip per fare il chip dal singolo strato originale, Turn to multi-layer stacking. Per questo motivo, il packaging avanzato è diventato anche uno dei driver chiave per migliorare la legge di Moore, guidando la tendenza nel settore dei semiconduttori.

Il lavoro principale del futuro laboratorio intelligente comprende: la creazione di un sistema di intelligenza artificiale sistema di valutazione IQ e l'esecuzione della valutazione IQ mondiale dell'intelligenza artificiale; Realizzare il piano di ricerca del cervello cloud di Internet (città), costruire la tecnologia del cervello cloud di Internet (città) e la mappa aziendale e servire a migliorare il livello di intelligenza di imprese, industrie e città.