Il principio e l'applicazione del 3D IC Packaging

Lo strato mediante 2.5D è una configurazione in cui i nuclei del tubo sono installati fianco a fianco su uno strato mediante di silicio, vetro o organico utilizzando un foro passante di silicio (TSV) attraverso lo strato mediante. (Quando vetro o laminati organici sono utilizzati come substrato per lo strato intermedio, sono chiamati attraverso vetro attraverso fori (TGV) e substrato attraverso fori (TSV) rispettivamente.) La comunicazione tra i nuclei avviene attraverso un circuito prodotto sullo strato intermedio.

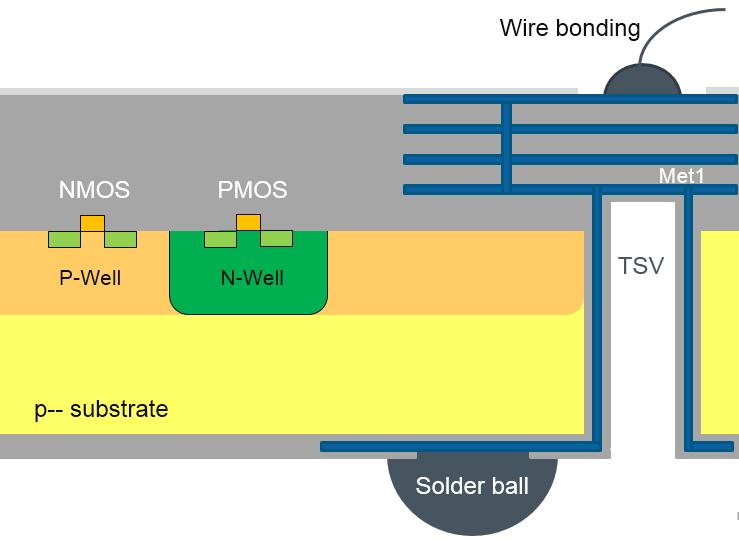

I sensori di immagine CMOS (CIS) hanno TSV come fori posteriori per formare interconnessioni, eliminando le fusioni di chiavi di piombo consentendo dimensioni ridotte e densità aumentata. In tutti i tipi di pacchetti 3D, i chip nella confezione utilizzano segnali off-chip per comunicare come se fossero montati in un pacchetto separato su un normale circuito stampato.

3D IC può essere diviso in 3D stacked IC (3D-sic), il che significa che il chip IC è impilato e interconnesso con TSV; E i veri ics 3D, che utilizzano il processo FAB per impilare più livelli di dispositivi su un singolo chip, possono o meno utilizzare TSVS molto finemente distanziati per formare interconnessioni.

I fori passanti del silicio (TSV) sono fori creati in wafer di silicio utilizzando un processo di incisione. L'interconnessione si forma riempiendo il TSV con un materiale conduttivo come rame, tungsteno o polisilico (Figura 2). Il vantaggio principale delle interconnessioni TSV è che accorciano il percorso attraverso il quale i segnali viaggiano da un chip all'altro o da uno strato di circuito all'altro. Ciò consente una potenza ridotta e la possibilità di aumentare la densità di interconnessione, migliorando così funzionalità e prestazioni. Il TSV stesso non è un IC 3D. Invece, sono la base per abilitare il 3D ics. I fori posteriori sono utilizzati anche in altri dispositivi, come sensori di immagine, sistemi microelettromeccanici (MEMS) e semiconduttori composti.

Qual è il significato di IC 3D monolitico?

Invece di impilare wafer o moduli per creare un IC 3D, un IC 3D monolitico inizia con un wafer base su cui vengono aggiunti strati aggiuntivi come silicio cristallino, strati metallici e circuiti attivi e passivi utilizzando dispositivi FAB tradizionali (Figura 2). Le interconnessioni verticali sono formate tra strati piuttosto che tra chip utilizzando fori passanti nel nanometro piuttosto che nell'intervallo micron; Come la TSV. Diversi approcci diversi sono in fase di sviluppo, principalmente per applicazioni in-memory. Il 3D integrale è talvolta chiamato 3D sequenziale.

Che cos'è la memoria 3D?

Molti metodi sono stati sviluppati per impilare la memoria perpendicolare a due dispositivi di memoria non volatili (NAND flash) e volatili (DRAM). I metodi DRAM includono la memoria ad alta larghezza di banda (HBM), il cubo di memoria mista di Micron e la RAM integrata di Tezzaron (DiRAM). Tutto questo è basato su un IC 3D che utilizza TSV (Figura 3). Samsung, Toshiba e molti altri stanno sviluppando flash NAND 3D basati su approcci 3D olistici.

Quali sono i vantaggi della tecnologia 2.5D inserter?

Originariamente sviluppata come tecnologia di ponte per l'ics 3D, la tecnologia 2.5D è cresciuta in una piattaforma di imballaggio che dovrebbe coesistere con l'ics 3D. A differenza del 3D-IC, solo lo strato intermedio (non il nucleo stesso) richiede il TSV per collegare il nucleo attivo al substrato del pacchetto. Ciò consente l'uso di modelli di stampi esistenti.

Quali sono i principali driver tecnici dell'integrazione 3D?

L'aumento del costo di questa fase litografica e della lavorazione dei wafer in generale al nodo dei chip di prossima generazione sta spingendo l'industria a cercare alternative per migliorare le prestazioni e la funzionalità dei nostri dispositivi elettronici e ridurre i costi. Inoltre, la necessità di integrare varie tecnologie (logica, memoria, RF, sensori, ecc.) a piccole dimensioni sta spingendo il settore ad abbracciare l'integrazione 3D come soluzione.

Quali sono i driver di mercato per l'integrazione 3D?

La spinta del mercato per l'integrazione 3D (integrazione 3D) inizia con l'elaborazione di fascia alta, server e data center, militari e aerospaziali e attrezzature mediche, in quanto sono più richieste e possono permettersi il costo delle attuali tecnologie di integrazione 3D. Tablet, smartphone e dispositivi di gioco sono anche alla guida della tecnologia.

Quali sfide devono affrontare i sistemi 3D?

Mentre molti sostengono che non ci sono ancora sfide tecniche e che i restanti problemi possono essere facilmente affrontati, alcune fasi del processo richiedono ancora soluzioni migliori, come strumenti di progettazione per la pianificazione, l'implementazione e la verifica degli ICS 2.5D e 3D, l'elaborazione dei wafer, la gestione termica e i test. Le sfide principali sono gli attuali costi unitari, le basse quantità e i rischi di implementazione dovuti alla maturazione dell'ecosistema. Si stanno facendo sforzi per ridurre i costi di processo e semplificare la collaborazione in tutto il settore. L'aumento della produzione contribuirà a ridurre i costi. Tuttavia, molti esperti 3D ritengono che l'implementazione di 3D ics ridurrà notevolmente i costi di sistema, e che la sfida restante sia quella di educare gli ingegneri a livello di sistema sui vantaggi della progettazione 3D ics nei loro sistemi.

Il sensore di immagine CMOS (CIS) è uno dei primi dispositivi ad implementare il foro attraverso il foro in grandi quantità. CIS con illuminazione posteriore (BSI) è ora in produzione e poiché il CIS è impilato sopra l'IC, si tratta di un dispositivo IC 3D (Figura 2). Xilinx ha introdotto un design plug-in 2.5D per tutti i FPgas programmabili della sua serie Virtex-7 nel 2011. Negli ultimi anni Tezzaron ha consegnato piccole quantità di DiRAM.

Alla fine del 2014, Micron e Samsung inizieranno la produzione di ibridi storage Cubes (HMCS), che sono stack DRAM 3D in cima ai dispositivi logici. SK Hynix fornirà sia la memoria HMC che l'alta larghezza di banda (HBM). La produzione di massa di questi dispositivi di archiviazione 3D integrati è avvenuta nel 2014/15 e ha continuato a utilizzare stack logici e dispositivi eterogenei per diversi anni dopo.

iPCB condividerà tutte le informazioni con te!