今日, チップを完全に理解することなく高速電子システムを設計することは困難である, パッケージ構造, and PCBボード 電源系統特性. 事実上, より低い電源電圧を満たすために, フリップフロップ, 高いレベルの統合, そして、より多くの挑戦的な需要, 製品設計プロセスの電子設計会社の最前線での多くのウォーキングは、電源と信号の整合性を確保するために, 電力系統の分析, 人的資源と物質資源.

電力供給システム(pds)の解析と設計は,特に,コンピュータ,半導体,通信,ネットワーク,家電業界において,高速回路設計の分野でますます重要になってきている。VLSI技術の必然的なスケーリングダウンに伴い、集積回路の供給電圧は低下し続ける。より多くのメーカーが130 nmから90 nmに変わると、供給電圧が1.2 Vまで低下するか、さらに低くなり、電流が著しく増加することが期待できる。dc‐ir電圧の低減からac動的電圧変動制御への展望から,この開発傾向は,より小さな許容範囲の小さい電源システムの設計に大きな課題をもたらす。

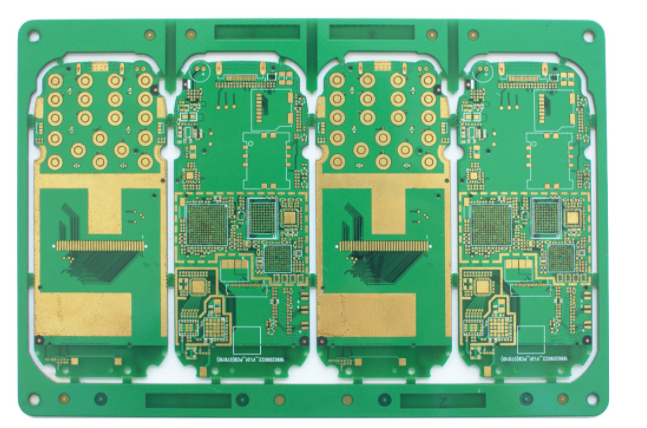

PCB電源システムの設計概要

通常,交流解析において,電源と接地間の入力インピーダンスは,電源システムの特性を測定する重要な観測である。dc解析におけるこの観察の決定はir圧力降下の計算に発展する。DCまたはAC解析において、電源システムの特性に影響を及ぼす要因は、PCB層、パワーボード層面の形状、部品のレイアウト、ホール及びピンの分布などである。

電源と接地の間の入力インピーダンスの概念は、上記の要因のシミュレーションと分析で使用することができます。例えば、電源接地入力インピーダンスの非常に広い用途は、ボード上のデカップリングコンデンサの配置を評価することである。ボード上に配置された特定の数のデカップリングコンデンサを用いることにより、ボード自体の特性共鳴を抑制することができ、したがって、ノイズの発生を低減し、また、ボードのエッジ放射を低減して、電磁両立性問題を軽減することができる。システムの設計信頼性を向上させるために,システム設計技術者は,デカップリングコンデンサのシステムレイアウトを経済的かつ効果的に選択する方法を検討しなければならない。

高速回路システムにおける電源システムは,チップ,集積回路パッケージ構造,pcbの三つの物理サブシステムに分けられる。チップ上のパワーグリッドは金属の交互層からなる。各層は、XまたはY方向の金属のストリップから構成され、電力または接地格子を形成する。穴は、異なる層の金属の細片を接続します。

いくつかの高性能チップについては、コアおよびIO電源は、多くのデカップリングユニットと一体化される。小型PCBのような集積回路パッケージ構造は、複雑に成形された電源またはフロアプレートのいくつかの層を有する。パッケージ構造の上面には、通常、デカップリングコンデンサの設置位置が予約されている。PCBは、通常、連続した大きな電源およびフロアプレート、およびいくつかの大規模および小さな離散デカップリングコンデンサ要素、および電力整流モジュール(VRM)が含まれています。ボンド・ワイヤ、C 4衝突およびハンダ・ボールは、チップ、パッケージおよびPCBを連結する。

全体の電源システムは、集積回路構成要素が正常な範囲の範囲内で安定した電圧を提供することを確実としなければならない。しかし、それらの電源システムにおけるスイッチング電流および寄生周波数効果は常に電圧ノイズを導入する。

実際には、PCB上に配置されたディスクリートデカップリングコンデンサの周波数範囲が数百メガヘルツに達することができるという別の非常に重要な事実も明らかにする。しかし、周波数が高いと、各ディスクリートデカップリングコンデンサの寄生インダクタンスおよび基板のループインダクタンス(コンデンサ−チップ)とスルーホールを介して、デカップリング効果が大幅に低減される。ディスクリートデカップリングコンデンサをPCB上に配置するだけで、電源システムの入力インピーダンスをさらに低減することはできない。数百メガヘルツから高周波数範囲まで、パッケージ構造の電源システムのプレート間容量とパッケージ構造上に配置されたディスクリートデカップリング容量とが遊びに来る。GHz周波数範囲では、チップ内のパワーグリッドとチップ内のデカップリングコンデンサとの間のコンデンサは、デカップリング解である。

図示の一例では、赤色ラインは、いくつかのディスクリートデカップリングコンデンサをそれに配置した後のPCBの入力インピーダンスである。つの共鳴ピークが600 mhzから700 mhzに現れる。パッケージ構造を考慮した後、追加のパッケージ構造のインダクタンスは、青色線に示すように、共振ピークを約450 MHzに移動させる。チップ電源システムの包含の後、チップのデカップリングコンデンサはそれらの高周波共振ピークを除去すると同時に、緑の線に示すように、30 MHzの非常に弱い共振ピークを導入する。この30 MHz共鳴は、高周波の反転信号の中周波数エンベロープの電圧トラフとして時間領域で表される。