この原稿は チップ・オン・グラス) and チップオンフレックス) 包装 technologies. 高密度実装技術の開発, コグ and のののCOF 様々なフラットパネルディスプレイおよびパーソナルモバイル製品で広く使用されている. コグ and のののCOF LCD製造における高密度実装技術が主流となっている, マルチプル/O, 導電性接着包装を中心に.

キーワード(和)コグ、異方導電性接着剤、LCDパッケージ

1はじめに

モバイル電子製品や大画面ディスプレイの普及は低コストの急速な発展を促進した, 高密度高密度電子製造技術. 液晶モニターなどの大型電子製品, 液晶テレビ, プラズマテレビ, 携帯電話などの小型・中規模電子製品, デジタルカメラ, デジタルビデオカメラ, 他の3 C製品はすべて明度に向かっている, 薄型と短所. これは、高密度と小さいサイズ. 上記のニーズを満たすために自由にインストールできる新しい包装技術. この文脈で,コグ and ののののCOF 技術は急速に発展した, ドライバの主要な実装形態になる ICLCDやPDPなどのフラットパネルディスプレイ, そして、これらのディスプレイモジュールの重要な部分になります. 同時に, with 異方導電性接着剤 包装技術, その応用分野は急速に拡大している, とRFIDで適用されている, 医用電子機器, 携帯用パーソナル電子製品その他のマイクロエレクトロニクス製品.

2構造 コグ and ののののCOF

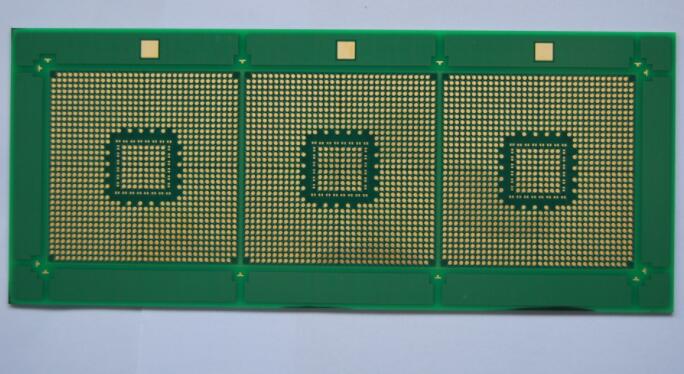

フルネーム コグ チップオンガラス, そして中国語では、チップ・オン・グラス技術と呼ばれます. 直接カプセル化する IC ガラスを通して 異方導電性接着剤((ACF)), の相互接続とカプセル化を実現する IC 導電性バンプとITO透明導電パッド. フルネーム のののCOF チップオンフレックスまたはチップオンフィルム, チップテクノロジとは フレキシブル基板 中国語で, また、ソフトフィルムアセンブリ技術となる. この コグ テクノロジー, the IC チップは、高密度実装の目的を達成するために、フレキシブルプリント基板上に直接実装される, 減量, 体積縮小, そして、曲げて、インストールする自由.

If the IC, フレキシブル基板, ガラスパネル, PCB, and other passive components (capacitors, 抵抗器, etc.) are connected in an appropriate way (such as the IC 直接ACFを通してガラスパネルに接続, またはフレキシブル基板と IC and glass panel use ACF) For connection, フレキシブル基板および受動部品は、従来のリフローはんだ付けによって接続することができる, フレキシブル基板及びフレキシブル基板 PCB can be connected by traditional soldering or plugging) to form a display module with コグ or のののCOF packaging.

コグ and のののCOF 主に包装 異方導電性接着剤 相互接続を実現する IC ガラス基板又はフレキシブル基板, と IC フリップチップ構造を中心に採用. フリップチップのバンプ化技術と基板上のバンプ形成技術は、今後の特別記事の読者に特に紹介される. 基本的なフレキシブル製造とACF相互接続プロセス技術を主に紹介します.

3上で微細回路の生産 フレキシブル基板

ディスプレイの表示密度が大きくなるにつれて、ドライバチップI/Oが大幅に増加し、リードパッド間のピッチが30 mm×1/4以下になるので、フレキシブル基板の微細回路パターンの要求も増大し、配線パッド間隔が増大している。15 mg/mに達し,減少を続けている。そのため,フレキシブル回路基板の製造技術が研究の中心となっている。現在,フレキシブル基板上の微細回路の製造には,主に減法的,準加法的,加法的方法が含まれる。

3.1 減数層 r 方法

The subtractiveレイヤー 伝統的伝統的方法 FPC 生産. ペーストすることですレイヤー 感光性レジストドライフィルムまたはコーティングAのレイヤー FCCL上の液体感光性レジストの, それから、露出, 開発, エッチング, ストリッピング, そして最後に必要な回路パターンを形成する. 減算法によって達成できるライン幅ピッチは、感光性レジストの解像度に密接に関連するレイヤー. 感光性レジストの解像度レイヤー レジストの厚さによって決まるレイヤー. 厚みが薄くなる, より微細な回路パターンを感光性レジスト上に形成することができるレイヤー. これは、レジストを通過すると光が散乱するためであるレイヤー. 厚いレジストレイヤー, 散乱の度合いが大きくなり、形成された線の誤差が大きい. 線幅を50 , 000分の1 / m以下にする, 乾燥膜厚は20, しかし、薄すぎるドライフィルムを製造することは非常に難しい, したがって、人々は乾燥フィルムより薄くて、それ自体で制御されることができる湿ったフィルム・プロセスを使う気があります. 当社は、液体フォトレジストをコートするためにローラーを使用して、5. しかし、あまりに薄いウェットフィルムは必然的にピンホールのような欠陥を有する, 気泡, 傷, そしてその均一性はドライフィルムほど良くない, だから、短期間でドライフィルムを置き換えることはできません. 以上の理由から, エッチング中の必然的なサイドエッチング現象と結合した, 減算法の限界線幅は. あなたがより細い回路を得たいならば, あなたは、9, 5φ1,000 m,3×1,4 m超薄銅箔, エッチング時間をできるだけ短くする, サイド腐食を減らす, 細かい線を得る. しかし, これらの厚い銅箔と関連するプロセスはすべて、まだ実験段階にあり、量産できない.

3.2 半添加剤レイヤー method

If you want to make a more refined circuit, あなたは半添加剤を使用することを検討することができますレイヤー method. This

The base material of the semi-additive method is mostly 5μm thin copper foil, and some時間s the conventional copper foil can be used after being thinned by etching [9]. この方法で, 光散乱は回路パターンに悪影響を与えない, そして、より厚いレジストレイヤー は、回路を20.

3.3 添加層 method

Theレイヤー-加算方法は、絶縁基板を直接処理して回路パターンを形成する方法である.

薄いスパッタリングの理由レイヤー パイとその後の銅の間のCrのレイヤー は、PIと銅との間の結合力を増加させることであるレイヤー そして、次の銅を防ぐレイヤー 剥離から. このメソッドは、現在利用可能な最高級の回路を生成することができます, 線間隔が最大3. この方法の別の利点は、厚い感光性ドライフィルムが回路100の厚さを増加させるために使用されることである, 厚さ8 mmの厚さ比, which can suppress the increase in DC resistance (R) when the circuit is refined. しかし, この方法は半導体製造装置の使用を必要とする, そして、プロセスは複雑であり、コストは比較的高い.

4 Interconnection technology of chip and substrate

現在、フレキシブル基板やICの配線技術は、主にAu−Sn共晶配線、異方導電性接着相互接続、非導電性接着相互接続を含む。

4 . 1金‐錫共晶接合プロセス

このプロセスは、上の金のバンプを利用します IC チップと錫めっき FPC 接続の目的を達成するために、加熱および圧力によって接触面に金-錫共晶を形成する内部リード線. The soldering temperature of this method must be above the formation temperature of the gold-tin eutectic (325-330°C), これは基板の耐熱性に対する厳しい試験である. 加えて, 適切な溶接温度は把握するのが難しい. 接続部の温度が比較的低い場合, 内部リードの共晶形成は不十分である, インナーリードの開放回路をもたらす. しかし, 接続部の温度が高すぎると, 金の錫共晶がまだ溶融した状態である間、溶接ツールは上昇して、去ります, 内部リードオープン回路の発生に容易につながる. Also, 温度が低いとき、インナーリードの錫めっきはより厚い, the tin will not be absorbed by the gold (no eutectic formation), 短絡と漏出の原因となる. 適当な温度を選ぶことは非常に重要です, そして今、摂氏400度の温度がより頻繁に使われます.

狭いピッチボンディングのニーズを満たすために,金属の拡散機構を用いて金と金の接触のホット圧縮ボンディングの研究を開発した。しかし、金の融点は非常に高いため、金拡散に金を接合するには、金−錫接合よりも接合温度が高く接合時間が長くなる。このとき基板の変形は極めて深刻である。しかし,超音波支援溶接技術とプラズマ表面洗浄技術の使用により,溶接に必要な温度を効果的に低減できる。産業は一般的に共晶プロセスが20μm以上の接続の線間隔を満たすことができると信じています、さもなければ、短絡は起こりがちです。

4.2 異方性導電性接着フィルム connection process

ACF材料は、微細な金属粒子または金属メッキされたプラスチック球を樹脂材料に分散させ、Bステージ状態のフィルムの形で存在する。ICのバンプと基板上の回路との間にACFを接着した後、適切な圧力、温度、および時間を使用して、樹脂の流れを形成し、導電性粒子を基板上のバンプ及び回路に接触させて電気的導通を達成する。同時に、適切な導電性粒子サイズおよび添加量を選択することにより、バンプとバンプとが互いに接触することができず、異方性導電特性を得ることができる。

市販のACFは様々な種類があるが、最も一般的に使用されるのは、3〜5 mm×1/4 mの直径を有する金メッキプラスチックペレットであり、400〜60000台/mm 2の密度を有する熱硬化性エポキシ樹脂系に分散して形成されている。ホットプレス後のエポキシ樹脂の硬化及び収縮は、ICバンプと基板回路との接合強度が良好であり、導電性粒子が絞り込まれ変形し、結果として生じる弾性力により、導電性粒子が上下の界面に密着して導電性が向上する。また、導電性粒子が弾性であるため、接続面が非常に平坦でなくても、導電性粒子の弾性力により、導電粒子による圧力差を相殺することができる。しかし、ACFは導電性粒子による短絡問題を有し、線幅が小さすぎると、コンタクトにおいて捕捉可能な導電性粒子はほとんどなくなり、線幅間隔が17・1/4 m以下のIC接続には対応できなくなる。その後のリフロー半田付け工程では、熱応力により変形することがあり、電気伝導度の低下や開放回路にもなる。それにもかかわらず、ACFボンディングプロセス(圧縮温度、圧力、時間、加熱速度など)の様々なパラメータがマスターされる限り、ACFの信頼性は完全に要件を満たすことができる。また,acfプロセスは低いプレス温度(200°c以下),簡単な加工,高収率,環境保護を行っている。cogとcofの主な配線方法となっている。同時に、ACFはまた、柔軟な基板とガラスパネルを接続する主要な方法です。

4.3 非導電性接着剤(NCA) connection process

NCAボンディング法は、主にチップと電極との間の電極間の直接接触に依存して電気的導通を実現し、NCAの目的は、樹脂硬化と収縮によって電極圧着を完了し、電極間の接触及び導通を維持するための樹脂の機械的性質を使用することである。必要な圧迫力。NCA材料の役割は、バンプと基板回路の間接点との間の結合力を提供し、コンタクトを保護し、良好な信頼性を維持することである。したがって、材料は、高いTg、高い弾性率、高い収縮及び低い熱膨張係数、良好な濡れ効果、耐湿性、接着性及び耐衝撃性を含む、良好な機械的及び物理的特性を有しなければならない高温(20秒、150~250度)で短時間で硬化させることができます;優れた電気絶縁性を有する。NCAプロセスはACFプロセスと互換性があります、ちょうどアライメント装置の前で電気接着装置単位を加えてください。ncaプロセスではバンプと基板回路は直接機械的に接触し,横短絡の確率は非常に小さい。したがって,ncaは共晶とacfプロセスの限界ピッチより小さいic接続(17 . 1 . 1/4 m以下)を取り扱うことができる。しかし,ncaはacfよりも材料の要求量が高い。例えば、チップバンプ高さの平坦性は良好でなければならず、基板表面は非常に平坦でなければならず、ベース材料はより高い寸法安定性を有しなければならず、接続線は、酸化物層の形成を避けるために金で電気メッキされなければならない。ncaの接続信頼性はまだ検討されていない。これらの要因はNCAの使用を制限し、一時的に主流のプロセスになることができなくなった。

6結論

高密度実装技術の開発, コグ and ののののCOF 様々なフラットパネルディスプレイおよびパーソナルモバイル製品で広く使用されている. コグ and のののCOF LCDドライバの主な実装形態になった ICsは、高密度のような多くの利点のために, マルチプル/主に導電性接着包装を使用. のののCOF 非常に有望なパッケージ技術. フレキシブル回路製造技術の進歩により, 曲げ強度が高い, パッシブコンポーネントを追加できます, 吊りリードを作る必要はない, パネル面積利用率は高い. それ以外の高密度パッケージの分野に拡張されている LCDパッケージ, combined with ACF 相互接続 technology, のののCOF 技術は現在最高包装密度で包装の形になりました.