高性能、高信頼性集積回路パッケージパッケージパッケージチップの相互接続技術

電子部品の市場動向(プリント基板アセンブリ用PCBA)

集積度と速度の高いLSIの成熟した技術には、適宜、低K材料を用いたアイソレーション技術を開発する必要がある。しかし、これらのセルの高性能を満たすためには、多孔質および多層構造のために、スペーサ層はますます薄くなっている。その結果、LSIは脆弱になる。一方、高速要件を満たすためにLSIの電流は増加している。チップサイズが大きいものから小さいものまで、熱密度と消費電力も増加しています。そのため、将来の半導体パッケージ基板(IC基板パッケージ)にとって、これらの問題、すなわち層間媒体の脆性、高熱、高速、低コストを解決する必要がある。半導体プロセスの将来のプリセットは20 nm以下であり、これははるかに弱い。

20 nm世代に必要なパッケージ技術

次世代20 nmに必要な仕様は、

脆性低K層の低応力

高性能LSIに適した高放熱5 W

高速10 GHz、高機能を実現

半導体パッケージの発展方向

モバイル機器を含む電気機器の機能的成長とコスト削減に対応するために、ウェハプリセット規則はより大きく、より細かいプリセット規則に向かって発展している。そのため、コスト削減のために、半導体パッケージ技術は最も標準的な金線接合技術から銅線接合に急速に転換しており、これにより金の使用量が減少している。また、フリップチップボンディング技術の使用はLSIのより高い集積度と性能を大きく満たしている。2010年、フリップチップボンディングは世界の半導体パッケージ技術の15%、ワイヤボンディングは85%を占めた。2015年までに、フリップチップボンディングのシェアは25%、ワイヤボンディングの割合は75%に達する見込みだ。特に、高熱放射線と高信号速度を必要とする高集積度と高性能LSIについては、フリップチップボンディング技術が適していると積極的に考えられている。

常識的なフリップチップ技術

低K向け

一般的なフリップチップ技術:

・隣接側面を溶接し、主要構造はC 4(制御可能沈降チップ協同設計)

・AuバンプとACFタイプの圧着用

AU−AU型署名の超音波接着

圧力結合と超音波結合はLSIに高圧と機械的振動を与えるため、これらの方法は低K LSIには使用できない。したがって、上記方法では、C 4を適切に使用することができ、3つの方法の比較により、C 4によるチップへのダメージが最小であることと一致する。

C 4技術は40年代初めに誕生し、汎用コンピュータに使用され、使用されてきた。低Kウエハ数が増加するにつれて、C 4はUBM構造、材料、改良を置換することによって低Kに使用される。

最近開発されたCuピラーバンプ(C 4の進歩とほぼ同様)は、低Kウエハではなく、直列または重畳パッドに適している。Cu(130 GPa)の高弾性率のために、Cuカラム構造パッケージが低k層を損傷する可能性が報告されている。熱膨張係数(CTE)の不整合は加速因子である。

また、C 4技術は最初にフラックスを用いた後の溶融金属接合とフラックスの高弾性率(50 GPa)が適切であると考えられているため、マザーボードの結合と取り付けの間、加熱膨張の違いによりLSIに応力の量が添加される。そのため、C 4技術は将来のLSIには使えず、後者はずっと弱い。

ねつほうしゃ

これまで、有機基板はフリップチップパッケージに使用されてきた。有機基板の熱伝導率は0.5 W/MKと小さく、高消費電力のLSIへの応用は困難である。冷却または冷却システムを追加して熱放射を改善すると、パッケージのコスト、平面、または表面の寸法と高さが増加します。

実際、LSIの一点は熱放射が低いためその潜在力を制限し、大量の熱を発生させない。また、熱放射が悪いため、接合温度が上昇し、漏れ電流が増加し、これにより消費電力がさらに増加し、消費電力の増加により温度が上昇した。これは危険な悪循環だ。したがって、熱放射線を改善することは密接に関連する問題である。

信号の高速度

有機基板の中心層の誘電体損傷損失は高く(0.02)、中心層のスルーホールのインピーダンス(T/H)は高い。その結果、高周波範囲での挿入損傷損失が高い。しかし、従来の有機基板と同じ材料を用いたコアレス基板は根本的な解決策ではない。また、複合層材料は多種多様であることができるため、ユーザが最適な材料を選択するのはより難しく、プリセット要件全体で高速性能の問題を考慮しなければならない。

基板が薄いため、一連の施設を交換する必要があります。これは生産の足かせになっている。この問題のため、コアレス基板への移行はリスクが高く、ローカライズ製品にのみ適用されます。

従来の技術では、将来の20 nm世代のニーズを満たすことは難しい。そのため、新たなコア技術を備えた新しい半導体パッケージの開発が必要である。

Monsterpacタイプとプロセスのポイント

Monsterpac typecは、従来のパッケージ技術では適応できなかった20 nmプロセスを満たすために開発された。これは伝統的な包装技術や構造とは全く異なる。

パッケージ構造

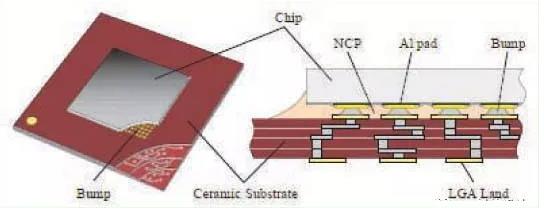

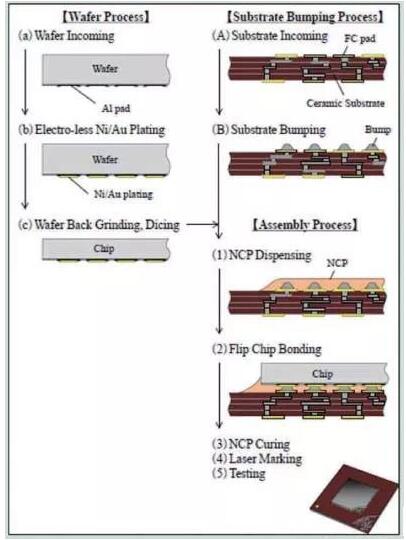

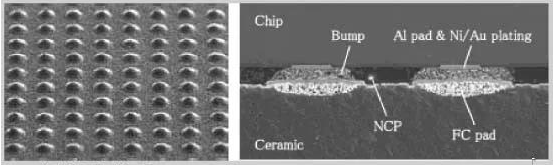

我々のパッケージ構造、基板はセラミックス、半導体チップはバンプフリップ、チップと基板はNCP(非導電性ペースト)を補充する。エポキシガスや天然樹脂で成形されていません。だからチップの裏面は露出しています。リフロー溶接の高温反りは小さく、30 ~ 50μm未満であるため、BGA(メッシュアレイパッケージ)ではなく、ハンダボールを持たないLGA(コンタクトアレイパッケージ)にパッケージ化されている。銀含有導電ペーストはバンプに使用され、バンプは基板上に印刷されるので、パッド上にモジュールを製造することはありません。チップのAlパッドのみにニッケルと金をめっきせず、ウエハバンプなしのプロセス(図1-3)。

FIC-1包装構造

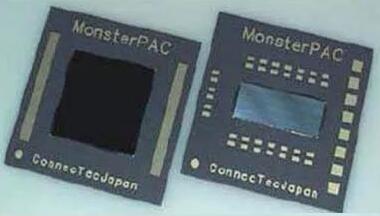

FIC-2パッケージ画像

FIC-3プロセス

上記とほぼ同様に、パッケージは4つの材料(チップ、バンプ、セラミックス、NCP)のみで構成されています。この簡単な構造により、パッケージの体積が小さく、薄く、軽い。

HTCC(高温共焼セラミックス)とLTCC(低温共焼セラミックス)の2つの主要なタイプのセラミックス基材を選択できます。セラミックスの特殊な性能(電気的性質、熱伝導性、CTE、反りなど)とフリップチップ接合により、私たちのパッケージは電気製品から半導体チップまでの様々な要求を満たすことができる最適なソリューションを提供します。

Monsterpacタイプは構造が独特である

これらのユニークな点は次のように記述されています。

・破損のない接着

・高熱放射

・挿入損失が低い

・高信頼性

これらの主な利点を組み合わせて、MonsterPac TypeCは20 nm世代LSIにできるだけ良い性能を提供することに成功した。

無損傷接着

我々のパッケージの核心技術は無損傷フリップチップボンディング技術であり、この技術は先端精密加工を用いて製造された半導体チップへの無損傷と高度に信頼性の高いボンディングを実現することに成功した。

破損していない半導体チップとは、

ていあつせっちゃく

通常のC 4の2.4 g/bump圧力の1/20である0.12 g/bumpの結合圧力を実現することができます。接合荷重をこの限界まで小さくすることにより、接合による層間媒体の損傷を回避することができる。

凸面硬化中の低収縮応力

バンプ凝固中の収縮応力は10 MPA/バンプより小さく、非常に小さい。脆性媒体中間層(例えば、低K及びAlパッド及び線路など)に印加される温度、負荷及び収縮応力を上限に下げることにより、線路の破断及び割れを回避するための高収量及び信頼性のあるフリップ溶接を実現することに成功した。

これらの利点から、弱い低K層損傷を回避する構造を有する唯一のパッケージであることが分かる。

こうねつほうしゃ

半導体チップの熱がパッケージ基板から放射されることを意識して、通常の有機基板(熱伝導率は0.5 W/mk)ではなく、セラミック基板を選択した。その熱伝導率は有機基板の熱伝導率より14 W/mk高いからである。パッケージサイズが21*21 mmであり、セラミック基板を使用する場合、消費電力は6 Wに達し、3.6 W消費電力の有機基板より1.7倍高い。

低挿入はあなたを傷つける

電子機器には、高周波範囲で高いレベルの性能が要求されている。セラミック基板の挿入損失は0.42 dB(@20 GHz,L=5 mm)であり、有機基板の挿入損失は0.62 dBであった。セラミック基板の許容周波数は10 GHzより大きく、有機基板の周波数は3 GHzである。

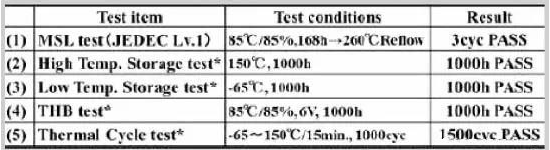

高い信頼性と高い防湿性

通常の還流抵抗(MSL:濡れレベル)は3段階(@30 DEG/60 100%RH 192 Hr)である。Monsterpac typecにはそれぞれ破損していない半導体チップがあり、バンプは非溶融材料で作られている。高温還流時にはバンプは溶融しないので、再溶融と再硬化を繰り返すことはなく、セラミックス基板も水分を吸収しない。そのため、MonsterPac Type CのMSLレベルは1レベル(@85 DEG/85 100%RH 192 Hr)であり、あらかじめベイク処理することなく湿気と防湿包装を除去することができ、MonsterPac Type Cの植物寿命は無限である。

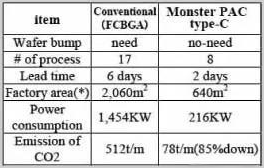

植物の生育率が高い

生産を容易にするために、溶接バンプではなくエポキシガスバンプ構造を開発した。そのため、大量のウェハバンプ処理施設が必要であり、リフローに隣接する大量のcan+溶接のコストも必要である。したがって、同じサイズの従来のC 4プロセス装置に比べて、装置の平面または表面サイズを69%削減することができ、装置のエネルギー消費を85%削減することができる。省エネと低背景負荷発電所の実現に成功することができる。

ようりょう

Monsterpac typec工芸のユニークな点

セラミック技術バンプ

Monsterpac typecはバンプ材料として銀含有導電ペーストを使用することが適切であると考えている。通常の溶接印刷SMD部品印刷技術を用いてセラミックス基板にバンプを形成する(場合によっては)。高点処理前にセラミックス基板表面を前処理してクリーニングする必要はなく、高点形成後に表面を電気めっきする必要もない。従来の有機FCBGAは、半田、Au、Cuバンプなどの半導体ウエハのAlパッド上の長いバンプを必要としていた。しかし、セラミックベースのバンプは、このようなウェハ長のバンププロセスを必要としない。逆に、彼らは半導体チップ上に無電解めっきのNiとAuを生産している。セラミック技術に基づくバンプは、処理が簡単で低コストなプロセスを実現することに成功した。

また、フラックス、Au、Cuバンプなどの常識的な技術で用いられるハードバンプ(硬度10 Hv)と異なり、ソフトバンプ(1 Hv)は低硬度でパターンを保持するために開発されている。

銀を含む軟凸導電性スラリーについて、低応力、低会札抵抗、詳細アスファルト印刷において経験豊富な関連固定点を開発した。これまで、私たちが形成してきたバンプの労働力は、面アレイパッド:間隔150Å、ペリフェラルパッド:間隔75島。しかし、実際のプリセット規則はこのパッドピッチを考慮しているので、60°mの表面アレイピッチは開口バンプにのみ適用されます。

無損傷接着

軟質フリップチップ接合技術を用いて、NCPはセラミックバンプ技術で形成された軟質バンプを分布させ、その後半導体チップとフリップチップを接合するために用いられる。接合中、バンプの導電性ペーストとNCPは同時に硬化する。その結果、共同署名と信頼性を実現することに成功した。

FCB施設の温度は200℃未満であり、通常の接着技術より40℃以上低い。接着圧力は0.12 g/dot未満であり、通常の接着技術の1/20である。これらの低温低圧熱圧着により、半導体チップは結合と結合後の硬化過程で応力と外力の影響を受けない。新開発の導電性スラリーとNCPを用いて、1.0秒未満の高速結合に成功した。NCPは、一般にチップパッドとバンプの両側で発見される補充剤を含む。しかし、低電圧でチップキーを反転することは一般的である。この補足物はバンプに埋め込まれているので、チップパッドとバンプの間の署名には影響しません。これは柔らかい揺れの利点の1つです。フリップチップ溶接前のNCP分布後、NCPはバンプと狭ギャップの間で補充しやすく、チップと基板の間のアライメントが発生しない低負荷キーを使用しています。そのため、この接合技術は狭パッドピッチに適している。

一般的な接合技術の問題点は、半田付けバンプを有するフリップチップ接合の場合、半田が溶融して硬化するまでの間、半導体チップのバンプとAlパッドに非常に大きな収縮応力(約200〜500 mPa/バンプ)を印加することである。しかし、非溶融バンプ材料の低弾性率には非常に小さな反発応力(10 MPa/バンプ未満)が必要であるため、低応力接合技術は成功している。

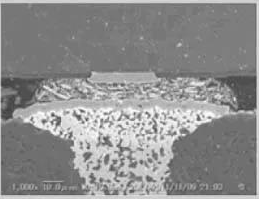

上述のような基礎技術の発展過程によるフリップ溶接の成功は損なわれていない。図4はフリップチップのキーとサインの断面図である。

図-4外観及び断面写真

ほうそうしんらいせい

TCは後バンプの輪郭を試験したが、破断結合によって引き起こされる可能性のある亀裂やスケールは試験も測定もしなかった。

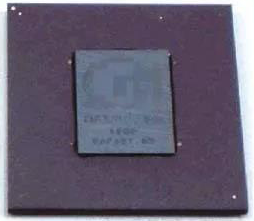

MAPIC(アプリケーションIC)

今日のAPIC加工は、高い温度公差と高速度を必要とする低K材料を用いた精密加工の方向に向かっている。Monsterpac TypeCは、これらの要件を満たすことができる次の利点があります。

・破損のない接着

・高熱放射

高速時

一部のAPIC顧客はMonsterPAC TypeCの規模生産を評価している

PACタイプC

同じ条件下(同じスカート、同じチップ、同じパッドピッチ)での有機FCBGAとmonsterpac Type C間の実際の評価の結果、monsterpac Type C温度Tjは有機パッケージの温度より10℃低い。Tjを非常に正確に比較すると、差は約20℃になります。

無線周波数板(無線周波数板):

現在、高速通信LSIについては、ボードパッケージの改良が進んでいる。これらのセクションには、次の特殊な特性が必要です。

・高速および高周波に適している

小さいサイズ

高速および高周波用途では、上述したように、適切であれば、セラミック基板を使用することで挿入損失を高めることができ、10 GHzに使用することができる。

さらに、マルチチップおよび大量のSMDコンポーネントは、小さな、詳細なピッチのフリップチップボンディングを使用できるので、小型パッケージに使用することができます。

顧客と協力して周波数板のサンプルを開発し、その性能はすでに顧客の認可を得て、規模化生産の準備をしている

無線周波数モジュール

これらのプレートハウジングに対して、基板の湿度は非常に密である。monsterpac TypeCのMSLは1級であるため、濡れ度窒息は存在しない。

monsterPAC TypeCは平板パッケージに最適であり、従来の有機パッケージSMDとフリップチップは複数回のリフロー溶接が必要であることがわかる。

判事

次世代の20 nmプロセスでは、より高い熱放射線とより高い速度に対応するためにカプセル化が必要です。しかし、常識的な包装技術ではこれらの要求を満たすことは難しい。そのため、20 nmプロセスに適した新しいパッケージ技術を開発する必要がある。

当社のMonsterpac TypeCは、来るべき20 nmプロセスに適しており、LSIの性能を最大限に向上させています。その高性能は驚くべき奇妙な製品のようだ。我々が開発したMonsterPACはC 4を時代遅れにし、将来の次世代半導体の主要技術となる。

次世代技術の開発

新規セラミックス基板の研究開発

セラミック基板技術の発展はずっと光明である。これまで、高密度の正確かつ詳細な描画は有機IC基板にはるかに遅れていた。

この問題を解決し、進展させるために、コストに影響を与えずに高密度の精密セラミック基板の開発に着手した。適切な精度を実現し、より柔軟な詳細図面を使用するためには、20°mの線間隔を目標としています。既定では、50°mを目標とする貫通孔間隔もより正確で詳細にする必要があります。

これまで、セラミック基板は、プレスとマスク印刷(場合によっては)を用いて製造されてきた。これらの従来技術は、正確で詳細な図面に限定されています。レーザーや直接印刷プロセスで置換することを考えています。この技術を実施することにより、有機基板よりも優れた性能を提供することができる。これまでセラミック基板はハイエンド製品に使用されてきたが、この新型基板は消費財に対応する。マトリックスには確かに高性能な消費財が必要です。

この基板とMonsterPAC技術の組み合わせは、世界に最適な性能と高信頼性のプリント基板(PCB)を提供するだろう。