の一般原則 PCB設計 デジタルアナログハイブリッド回路

ハイブリッド回路干渉の発生メカニズムについて話した。設計する前に、電磁両立性(EMC)の2つの基本原則を理解しなければならない。第1の原理は、電流ループの面積をできるだけ小さくすることである。信号が最小の可能なループを通して戻ることができない場合、大きいループは形成されることができる。アンテナアンテナ.第2の原理は、システムが1つの基準面だけを使用するということである。逆に、システムが2つの基準面を有する場合、ダイポールアンテナを形成することができる。これらの2つの状況をできるだけ避けてください。

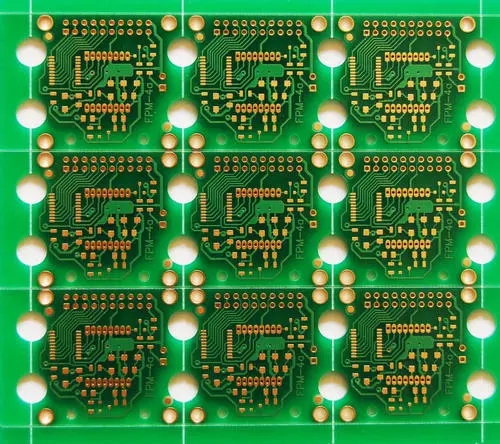

1)レイアウトとルーティングの原理。部品レイアウトのために考慮する第1の要因の1つは、デジタル回路部分からアナログ回路部分を分離することである。アナログ信号は、回路基板の全ての層のアナログ領域においてルーティングされ、デジタル信号はデジタル回路領域においてルーティングされる。この場合、デジタル信号戻り電流はアナログ信号グランドには流れない。特別な要件を持ついくつかの高周波のラインについては、手動でそれらをルーティングし、必要に応じて差動線またはシールド線を使用することが最適です。入出力コネクタの位置によっては、デジタル回路とアナログ回路の配線を混ぜ合わせなければならず、アナログ部分と回路のデジタル部分の相互影響を引き起こすことがある。これは、アナログ電力層の近くのデジタルクロックラインおよび高周波アナログ信号線を走らせるのを避けるために必要である。そうでなければ、電力信号のノイズは、敏感なアナログ信号に結合される。低インピーダンス電力およびグランドネットワークを達成しようとするために、デジタル回路ワイヤのインダクタンスを最小化し、アナログ回路の容量結合を最小限にする必要がある。ディジタル回路の周波数は高く,アナログ回路の感度が強い。信号線については、高周波デジタル信号線は、感度の高いアナログ回路装置からできるだけ遠くであるべきである。

2)電源及び研削処理。複雑なハイブリッド回路基板の設計において,接地線のレイアウトと取扱いは回路性能を改善する重要な因子である。デジタルグラウンドとアナロググランドの分離を達成するために,混合信号回路基板上のディジタルグラウンドとアナロググラウンドを分離することを提案した。しかし、この方法は分離ギャップ配線を横切る傾向があり、電磁放射及び信号クロストークの急激な増加を招く。

電流への電流リターンの経路と方法を知ることは、混合信号回路基板設計を最適化するための鍵である。グランド層が分割されなければならず、配線が分割間のギャップを通してルーティングされなければならない場合、分割されたグラウンドの間に単一点接続を行い、2つのグラウンドの間に接続ブリッジを形成し、接続ブリッジを通して配線することができる。

このように, 各信号線の下に直流リターンパスを設けることができる, または光アイソレーションデバイス, 変圧器, etc. また、セグメンテーションギャップ全体の信号を達成するために使用することができます. しかし, 実際には, PCB設計 統一地を採用する傾向がある. ディジタル・アナログ回路の分割と適切な信号配線, いくつかの困難なレイアウトと配線の問題は、通常解決することができます, そして、それは地方の分割のために若干の潜在的トラブルを引き起こしません. . 回路基板のテスト結果を比較することによって, また、統合された地盤の解は、機能とEMC性能に関して、分割された地面よりも優れていることがわかる.

通常、混合信号には独立したデジタルおよびアナログ電源がある PCBボード. スプリットパワープレーン, 好ましくは、グランドプレーンの次および下にある. パワープレーンは、無線周波数電流をスペースに取り付けることができる回路に結合することができる. この結合効果を低減するために, the power plane is required to be physically smaller than its adjacent ground plane by 20H (H refers to the distance between the power supply and the ground plane).

3)ハイブリッドデバイスの処理。一般的なハイブリッドデバイスは、水晶発振器、高速ADデバイス等を含む。一般に、AGndおよびDGNDピンは、同じ低インピーダンスアナログ接地面に外部に接続されるべきであり、リード線はできるだけ短いはずである。DGNDのどんな付加的なインピーダンスも、寄生容量を通してデバイスの内部アナログ回路により多くのデジタルノイズを連結する。もちろん、これは、コンバータの内側のデジタル電流がアナロググランドプレーンに流れる原因になるが、これは、コンバータのDGNDピンをノイズの多いデジタル接地面に接続するよりもはるかに少ない干渉を引き起こす。接地のように、アナログおよびデジタルパワーピンもアナログ電源プレーンに接続され、適切なバイパスコンデンサは、各パワーピンに可能な限り近く接続されるべきである。必要に応じて、アナログ電源ピンおよびデジタル電源ピンをジャンパーインダクタによって分離する必要がある。

(4) Add decoupling capacitors. デカップリングコンデンサは高周波干渉を排除できる. コンデンサの容量性リアクタンスは周波数に反比例するので, キャパシタと信号との間を並列に接続することは高周波ノイズのバイパスとなる. 原則的に, 各々の集積されたチップは、0.01 MF ~ 0.1 MFセラミックチップコンデンサ, チップがエネルギーを蓄えるのを可能にするだけではない, しかし、ドアが開閉されるときに、チップの回路の瞬間的な充電および放電エネルギーを提供して、吸収する, また、バイパスしてフィルタリングすることもできます. 装置の高周波ノイズ成分. Add a 10mF~100MF electrolytic capacitor (preferably a tantalum capacitor) to the power input terminal to suppress the noise interference of the power supply. もちろん, コンデンサのリード線は長すぎてはならない, コンデンサのリード長が非常に重要なパラメータであるので. インダクタンスが長い, インダクタンスが大きくなり、コンデンサの共振周波数が低くなる. 高周波ノイズに対する周波数のフィルタリング効果は弱くなります. したがって, in the design of 高速PCBボード, コンデンサのリードをできるだけ短くするために特別な注意を払うべきである. それで, コンデンサをできるだけ近いチップにする.

(5)銅箔の大面積をアナロググランドに接続する。銅箔の広い領域でアナログ回路を覆い、ブランク領域に密な穴をあけて、アナロググランドに接続する。これにより、遮蔽及び分離効果を奏することができ、それによってアナログ信号間の相互干渉を低減することができ、また、放熱においても役割を果たすことができる。

(6)電源配線と接地線は、できるだけ短く、厚くする必要がある。特に、デジタルパワーとアナログパワーを接続する磁気ビーズ上の配線は、電圧降下を小さくすることに加えてカップリングノイズを低減することが重要である。