プリント基板では、回路設計段階で電磁互換性(EMC)設計を考慮することが重要である。12層板を例に、階層化方法、配線規則、接地と電源線レイアウト、電磁互換性を紹介した。電磁互換性は新興の総合性学科であり、主に電磁干渉と耐干渉問題を研究している。電磁互換性とは、規定された電磁環境レベルにおいて、電子機器またはシステムの性能指標が電磁干渉によって低下することはなく、それ自体に発生する電磁放射は限定された限界レベルを超えず、他のシステムの正常な動作に影響を与えないことを意味する。そして、設備と設備、システムとシステムが互いに干渉せず、共に信頼できる仕事をする目的を達成する。電磁干渉(EMI)は電磁干渉源が結合経路を通じてエネルギーを敏感なシステムに伝達することによって引き起こされる。これには、ワイヤと共通接地伝導、空間放射、または近接場結合の3つの基本的な形式が含まれています。回路原理図の設計が正しく、プリント基板の設計が不適切であっても、電子機器の信頼性に悪影響を与えることが実証されている。したがって、プリント基板の電磁互換性を確保することがシステム設計全体の鍵となる。本文は主に電磁互換性について討論する。多層プリント基板の設計における技術及びその応用。

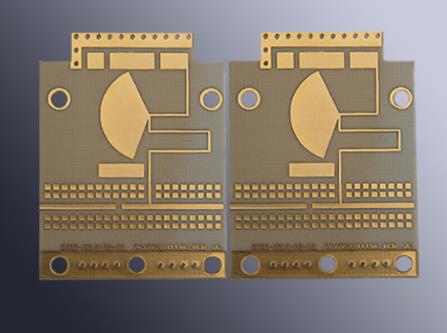

PCBボードは、電子製品における回路素子とデバイスの支持である。回路コンポーネントとデバイス間の電気的接続を提供し、さまざまな電子デバイスの基本コンポーネントです。現在、大規模で非常に大規模な集積回路は電子機器に広く応用されており、プリント基板への素子の実装密度が高くなり、信号の伝送速度が速くなっている。EMCの問題もますます浮き彫りになっています。PCBボードは、単板(単層板)、二層板(二層板)、多層板に分かれている。片面と2枚のパネルは一般的に中低密度配線回路と低集積度回路に使用され、多層板は高密度配線と高集積度回路を使用している。電磁互換性の観点から見ると、片面と両面の回路は高速回路に適さず、片面と両面の配線は高性能回路の要求を満たすことができなくなり、多層配線回路の発展は上述の問題を解決するために可能性を提供した。応用はますます広がっている。多層配線の特徴PCB板は有機と無機電誘電体材料からなり、多層構造を持っている。層間の接続はビアを介して実現され、層間の電気信号伝導は金属材料でめっきしたり、ビアを充填したりすることによって実現することができる。多層配線が広く使用されているのは、(1)多層基板内部に特殊な電源層とアース層があること。電源層はノイズループとして使用して干渉を低減することができ、同時に、電源層は、共通インピーダンス結合干渉を除去するために、システムのすべての信号にループを提供します。電源ケーブルのインピーダンスを低減し、共通インピーダンス干渉を低減します。(2)多層板は特殊な接地層を採用し、すべての信号線に専用の接地線がある。信号線の特徴:インピーダンスが安定し、整合しやすく、反射による波形歪みを減少し、また、特殊な接地線を使用しています。線路層は信号線と地線の間の分布容量を増加させ、クロストークを減少させた。プリント基板の積層設計2.1 PCB基板の配線規則多層基板の電磁互換性解析は、電磁誘導のキールホーフ法則とファラデー法則に基づくことができる。キールホフの法則によれば、ソースから負荷までの時間領域信号伝送にはインピーダンス経路が必要である。多層PCBボードは、通常、直流(DC)電源または接地基準平面に多層が使用される高速で高性能なシステムに使用されます。これらの平面は通常、電源または接地平面として十分な層があるため、同じ層に異なる直流電圧を印加する必要はありません。レイヤは、隣接する伝送路上の信号の電流リターン経路として使用されます。低インピーダンス電流リターンパスを作成することは、これらの平面層の重要なEMC目標の1つです。信号層は、対称帯状線であっても非対称帯状線であってもよい物理基準平面層の間に分布している。多層板の構造とレイアウトを12層板を例に説明する。その階層構造はT-P-S-P-N-S-N-P-Bで、「T」は最上階、「P」は基準平面層、「S」は信号層、「B」は下地である。最上階から最上階までは第1階、第2階、第12階です。上部と下部は素子のパッドとして使用され、信号は上部と下部にあまり長く伝播して、トレースからの直接放射を減らすべきではありません。互換性のない信号線は、相互結合干渉を回避するために相互に分離されなければならない。高周波と低周波、大電流と小電流、デジタルとアナログ信号線は互換性がありません。コンポーネントレイアウトでは、互換性のないコンポーネントはプリント基板上の異なる位置に配置され、信号線のレイアウトは依然として必要です。彼らを隔離してください。設計時には、(1)どの基準平面層が異なる直流電圧を含む複数の電力領域を含むかを決定する3つの問題に注意してください。層11に複数の直流電圧があると仮定すると、設計者は、リターン電流が層10の上の基準平面を流れることができず、キャパシタをステッチする必要があるため、高速信号の信号層である第3、5、7、9がそれぞれ高速信号の信号層であるため、高速信号をできるだけ層10と底層から遠ざけなければならないことを意味する。重要な信号のトレースは、レイヤ上のトレースチャネルの可能な数を最適化するために、できるだけ多くの方向にルーティングされなければならない。異なる層に分布する信号トレースは互いに垂直であるべきであり、これは線間の電場と磁場の結合干渉を減らすことができる。レイヤ3とレイヤ7は「東西」トレースとして設定でき、レイヤ5とレイヤ9は「東西」トレースとして設定できます。「南北」路線を運行する。どのレイヤーにルーティングするかは、目的地に到着する方向によって異なります。(2)高速信号をルーティングすると、レイヤが変化し、どのレイヤが独立したルーティングに使用されるかによって、リターン電流が基準平面から必要な新しい基準平面に流れることを保証する。これは、信号ループ面積を低減し、差動モード電流raを低減するためである