システムクロック周波数と立ち上がり時間が増加するにつれて, シグナル完全性 デザイン ますます重要になる. 残念ながら, ほとんどのデジタル サーキットデザイナー 信号完全性問題の重要性を理解しないでください, または、最後の段階まで、それを実現しないでください デザイン.

高速ディジタルハードウェア回路の設計における信号完全性の影響を紹介した。これは、特性インピーダンス制御、端子整合、電力および接地面、信号ルーティング、およびクロストークのような問題を含む。この知識をマスターすることによって、デジタル回路設計者は、回路設計の初期段階で潜在的な信号完全性の問題を通知することができ、また、設計の性能に対する信号の完全性の影響を回避するよう設計することもできる。

信号の整合性は常に必要なものの一つであったが デザイン ハードウェアエンジニアの経験, それは長い間デジタルで無視されました 回路設計. 低速論理の時代に 回路設計, シグナル完全性関連の問題はめったに起こらないので, 信号完全性の考慮は効率の無駄と考えられる. しかし, 近年、クロックレートと立ち上がり時間が増加している, 必要性と デザイン 信号完全性解析の増加も. 残念ながら, 大部分 デザインERは気づかない, そして、まだシグナルの完全性の問題を考える デザイン.

最新のディジタル回路は、GHzまでの周波数に到達し、50 ps以内に立ち上がり時間を有する. この率で, 過失 PCB設計 痕跡も1フィート, 結果電圧, 遅延とインターフェイスの問題は、この行に限定されません, しかし、ボード全体と隣接するボードにも影響します.

この問題は、特にハイブリッド回路において深刻である。例えば、アナログ信号をデジタル的に受信するシステムに高性能ADCがあることを考える。ADCデバイスのデジタル出力ポートに広がるエネルギーは、アナログ入力ポートよりも130 dB(10、000、000、000、000倍)に達することができる。ADCデジタルポート上の任意のノイズ。設計における信号の完全性は不可解なプロセスではない。設計の初期段階での潜在的な問題を実現し,それによって生じた問題を効果的に回避することは重要である。本稿では,いくつかの重要な信号完全性課題とそれらに対処する方法について論じた。

シグナルの整合性を確保する

アイソレーション

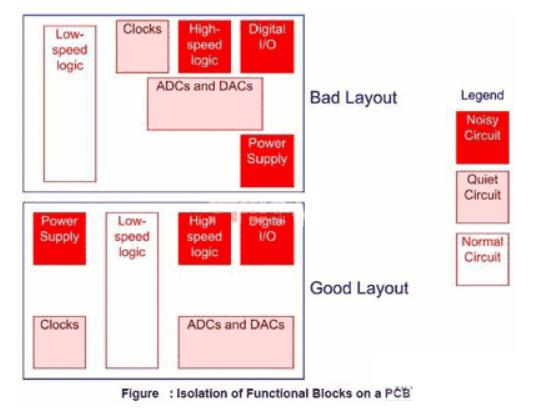

コンポーネント PCBボード 様々なエッジレートと様々なノイズの違い. SIを改善する最も直接的な方法は、 PCB デバイスの境界値と感度に基づいて. 下の図は例です. 例では, 電源, デジタルI/ポート, と高速論理, クロック・データ変換回路のハイリスク回路, 特別に考慮される. 最初のレイアウトで, ノイズの多いデバイスに隣接してクロックおよびデータコンバータを配置する. ノイズは敏感な回路に結合し、性能を低下させる. 第2のレイアウトの効果的な回路分離は、系のシグナル完全性のためになる デザイン.

インピーダンス、反射及び端子整合

インピーダンス制御と端子整合は高速回路設計の基本的課題である。通常、無線周波数回路はあらゆる回路設計において最も重要な部分であると考えられるが、無線周波数より高い周波数を有するいくつかのデジタル回路設計はインピーダンスおよび端子整合を無視する。

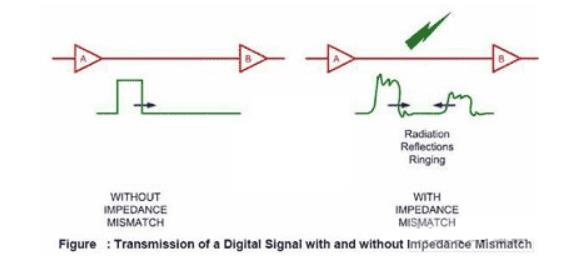

インピーダンス不整合によるデジタル回路に致命的な影響がいくつかあります。

a .デジタル信号は、受信装置の入力と送信装置の出力との間の反射を引き起こす。反射された信号は反発され、端部で完全に吸収されるまで、ラインの両端に沿って伝搬する。

b .反射信号は伝送線路を通過する信号のリンギング効果を引き起こし、リンギングは電圧及び信号遅延及び信号の完全な劣化に影響を及ぼす。

C .不整合の信号経路は、環境に信号放射を引き起こすことがある。

インピーダンス不整合に起因する問題は、抵抗を終端することによって最小化することができる。終端抵抗器は、通常、受信端に近接する信号線上に配置された1つまたは2つの別個の構成要素である。簡単な方法は、直列に小さな抵抗器を接続することです。

終端抵抗は信号立ち上がり時間を制限し,反射エネルギーの一部を吸収する。インピーダンス整合の使用が破壊的要因を完全に排除することができないことは注目に値する。しかし、適切なデバイスを慎重に選択することによって、端子インピーダンスは、信号の完全性を効果的に制御することができる。

すべての信号ラインは、コンパクトPCI仕様の特性インピーダンス及び端子インピーダンス特性などのインピーダンス制御を必要としない。

インピーダンス制御仕様を必要としない他の規格および設計者にとっては、それらは特に関与しない。最終的な標準は、1つのアプリケーションからもう一つまで変わるかもしれません。したがって、信号線(相関と遅延TD)と信号立ち上がり時間(Tr)の長さを考慮する必要がある。インピーダンス制御の一般的なルールはtd(delay)がtrの1/6より大きいことである。

内部電気層と内部電気層分割

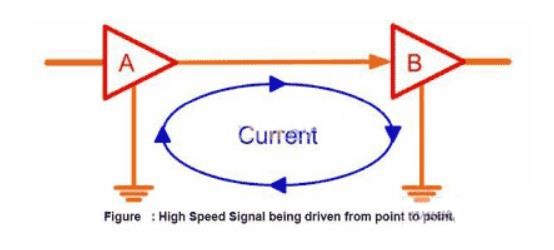

現在のループ設計においてデジタル回路設計者によって無視される要因は、2つのゲート回路(図の下に示す)間のシングルエンド信号の伝送の考慮を含む。電流Aは、ゲートAからゲートBへ、そして、それからグランドプレーンからゲートAに戻る。

上の写真には2つの潜在的な問題があります。

A点AとB点との間の接地面は、低インピーダンス経路を介して接続される必要がある。グランドインピーダンスがグランドプレーンの間で接続される場合、グランドプレーンピン間の電圧逆流が生じる。これは必然的に全てのデバイスの信号振幅の歪みと入力ノイズの重畳につながる。

b .現在のリターンループの面積は、できるだけ小さくなければならない。ループはアンテナのようです。一般的に言えば、ループ面積が大きくなればループ放射と伝導の機会が増大する。すべての回路設計者は、リターン電流が信号線に沿って直接的になることを望み、最小ループ面積を得る。

大面積接地を用いることで,上記2つの問題を同時に解決できる。大面積接地は、全ての接地点間に小さなインピーダンスを与えることができ、一方、リターン電流は信号線に沿って可能な限り直接戻ることができる。

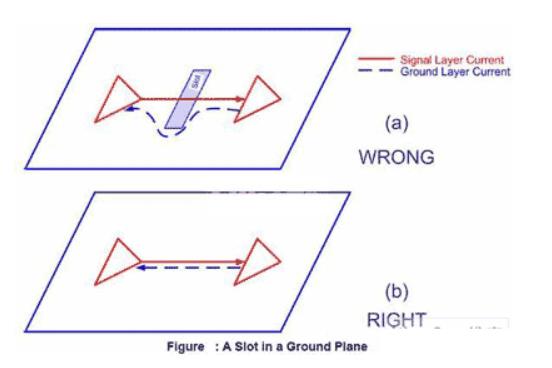

間の共通ミス PCB デザインERSは地面にバイアとスロットを作ることです. 信号線がスロット化された地球電気層の上にあるとき、以下の図は流れの方向を示します. ループ電流はスロットを迂回させる, これは必然的に大きな循環ループを作り出す.

一般的に言えば、接地パワープレーンにスロットをかけることはできない。しかし、スロットが不可避である若干の状況において、PCB設計者は、シグナルループがスロット領域を通過しないことを最初に確認しなければならない。同じ規則は混合信号回路に当てはまる。

複数のグランドプレーンが使用されない限り PCBボード. 特に高性能ADC回路で, アナログ信号を分離する接地層, デジタル信号及びクロック回路を用いて信号間の干渉を効果的に低減することができる. それが再び強調される必要があるいくつかの機会では、スロットが不可避です, the PCB設計ERは最初に信号ループがスロット領域を通過しないことを確認しなければならない.

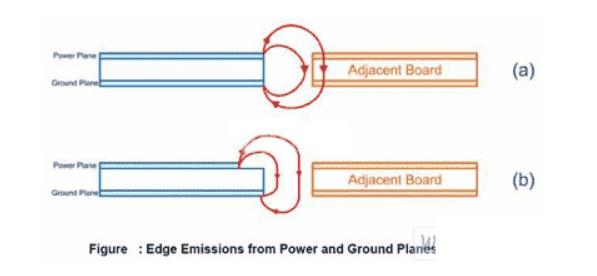

ミラー差を有するパワー層においても、層間領域の面積(以下、図に示す)に注意を払う必要がある。基板の端には、パワープレーン層の接地面層への放射線効果がある。エッジから漏れている電磁エネルギーは隣接するボードを損傷する。下記図を参照。適切に、接地面層がある領域に重なるように、パワープレーン層の面積を減少させる(図b参照)。これは隣接するボードへの電磁漏れの影響を低減する。

信号配線

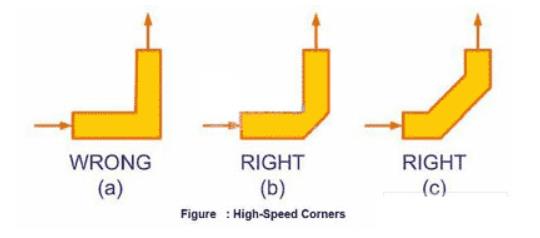

信号の完全性を保証する最も重要なことは信号線の物理的配線である.PCB デザイン労働圧力はしばしば, 完了するだけでなく デザイン 最短時間で, しかし、信号の整合性を確保するために. 可能な問題と信号のギャップをバランスさせる方法を知っているシステムのプロセスを促進する デザイン. 高速電流は信号線の不連続性に効果的に対処できない. 信号不連続性の問題は、以下の図において最も起こり易い. 低速回路で, 通常、信号不連続性を考慮する必要はない, しかし、高速回路で, この問題は考慮しなければならない. したがって, に 回路設計 とBに示すメソッドを使用する/図中のC, 信号の連続性を効果的に保証することができる.

高速回路設計では、信号配線に共通の問題がある。特別な理由がない場合は、すべての短い配線をできるだけ排除する必要があります。高周波回路設計において、短絡配線は、信号線のインピーダンス整合に起因する放射線のようなものである。

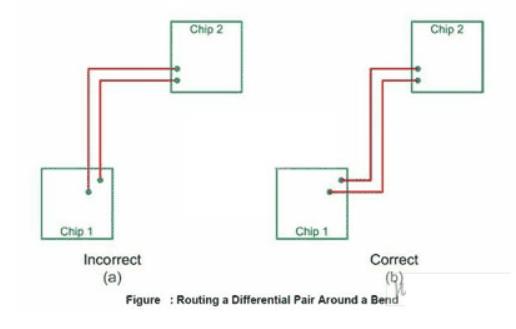

高速回路設計のルーティングにおける差動対のルーティングに特別な注意を払うべきである。差動対は、2つの完全相補信号線によって駆動される。差動対は雑音干渉を回避し,s/n率を改善できる。しかしながら、差動対信号線は特に配線の必要条件を有している。

つのワイヤは、配線に可能な限り近くなければならない

2 . 2行の長さは全く同じでなければなりません。

一緒に配置されていない2つのデバイス間の差動対信号線を適切にルート化する方法は重要な問題である。

上記画像Aでは、2つの信号線の長さの不一致により、何らかの不確実なリスクが生じる。正しい配線は、上記の図Bに示す方法をとるべきです。差動対配線の一般的な規則は、2つの信号線を等間隔にして互いに近接させ続けることである。

クロストーク

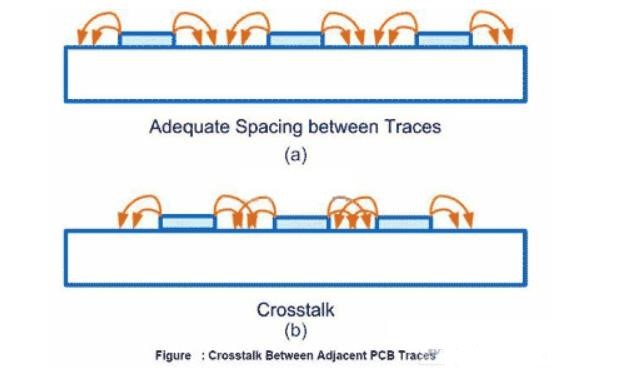

PCB設計において、クロストークは注目に値する別の問題である。次の図は、PCBの並列信号線の3つの隣接する対の間のクロストーク領域および関連する電磁領域を示す。信号線間の間隔が小さすぎると、信号線間の電磁領域が互いに影響し、信号の劣化が起こりクロストークとなる。

クロストークは信号線間隔を増加させることによって解決できる. しかし,PCB デザインERは、通常、ますますきつく配線スペースと狭い信号線間隔によって制約される選択肢がないからです デザイン, その中でいくつかのクロストーク問題を導入することは避けられない デザイン. 明らかに, PCB設計は、クロストーク問題を管理することができる必要があります. 信頼性の高いスペーシングの多くの関連ルールは、年間. 業界で一般的に認められているルールは, それで, 隣接する信号線間の距離は、信号線12の幅の少なくとも3倍でなければならない. しかし, 実際に許容できる信号線間隔は、実際のアプリケーションのような要因に依存する, 作業環境, and デザイン 冗長性. 信号線間隔は、ある状況から別の状況へと変化し、毎回計算される. したがって, クロストーク問題が避けられないとき, クロストークの定量化. これはコンピュータシミュレーション技術で表現できる. シミュレータの使用, the デザインer can determine the signal integrity effect and *estimate the crosstalk effect of the system.

電源デカップリング

パワーデカップリングはデジタル回路設計における標準的な実践である。ここで言及することは、電力線の雑音問題を減らすのを助けます。高性能回路の設計にはクリーン電源が不可欠である。電源に重畳された高周波ノイズは、各隣接するデジタルデバイスに問題を生じる。典型的なノイズは、グラウンドバウンス、信号放射、またはデジタルデバイス自体から来ている。電源ノイズを解決する最も簡単な方法は、地上で高周波ノイズを分離するためにコンデンサを使用することである。理想的な減結合コンデンサは高周波ノイズのための接地に低インピーダンス経路を提供し、それによって電源ノイズを除去する。実際のアプリケーションに基づいてデカップリングコンデンサを選択します。ほとんどの設計者は、電源ピンに可能な限り近接して表面実装コンデンサを選択し、予測可能な電源ノイズのために接地への低抵抗経路を提供するのに十分な容量値を必要とする。デカップリングコンデンサを使用するときに通常問題となるのは、デカップリングコンデンサを単にキャパシタとして考えることはできないということである。いくつかの状況があります。

コンデンサパッケージは寄生インダクタンスを引き起こす

b .コンデンサは、いくつかの等価抵抗をもたらす

c .電源ピンとデカップリングコンデンサとの間のワイヤは、いくつかの等価インダクタンスをもたらす

d .接地ピンとグランドプレーンとの間のワイヤは、いくつかの等価インダクタンスをもたらすこれによる効果

A .キャパシタは特定の周波数に共振効果を生じ、結果として生じるネットワークインピーダンスは隣接する周波数帯域における信号に大きな影響を与える

b .等価抵抗(ESR)は、高速ノイズのデカップリングによって形成される低抵抗経路にも影響する

これがデジタルデザイナにある効果をまとめます。

デバイス上のVCC及びGNDピンから引き出されたリード線は、小さなインダクタとして扱う必要がある。したがって、設計上、VCCとGNDをできるだけ短くかつ厚くすることが推奨される。

b .低ESR効果を有するコンデンサを選択し、電源の分離を改善する

小さいパッケージコンデンサを選ぶことは、パッケージインダクタンスを減らすでしょう。小さなパッケージでデバイスを変更すると、温度特性の変化になります。したがって、小さいパッケージ・コンデンサを選んだ後に、設計のデバイスのレイアウトを調整する必要がある。

設計では、Y 7 VキャパシタをY 7 Vキャパシタに置き換えることにより、パッケージの小型化および等価インダクタンスの確保が可能になるが、同時に高温特性を確保するためには、デバイスコストがさらに高くなる。

設計においては,大容量キャパシタによる低周波雑音のデカップリングも考慮すべきである。分離した電解コンデンサおよびタンタルコンデンサを使用することにより、装置のコスト効率を向上させることができる。

7章:

信号の完全性は高速ディジタル回路の設計を通して最も重要な課題の一つであるデジタル回路設計における信号完全性を保証するためのいくつかの提案があります:

ノイズ成分から物理的に高感度成分を分離する

インピーダンス制御、反射及び信号端子整合

c .連続パワーとグラウンドプレーン層を使用します

d .配線に直角を使用しないようにしてください

E .差動対の配線長は等しい

f .クロストークは高速回路の設計で考慮すべきである

電源のデカップリング問題;

ディジタルにおける問題の良い把握 circuit デザイン 上記のデジタルヘルプ サーキットデザイナー 多くの潜在的な問題を見つける 回路設計 できるだけ早く 回路設計.