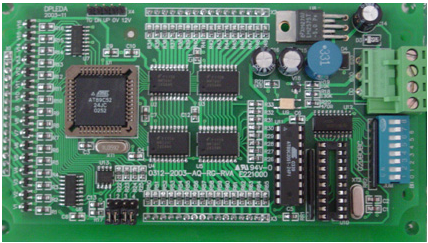

高周波回路基板配線

1. ピンの間のリードが短い 高周波回路基板 デバイス, より良い

信号の放射強度は、信号線のトレース長に比例する。高周波信号が長ければ長いほど、それに近い成分に容易に結合することができる。したがって、クロック、水晶発振器、DDRデータ、LVDS線、USB線、HDMI線および他の高周波信号線のような信号のために、できるだけ短い必要がある。

(2)高周波回路装置のピン間でリード層を異ならせた方が良い

いわゆる「リード線の層間交替がより少なく、より良い」とは、部品接続プロセスで使用されるより少ないビア(ビア)がよりよいことを意味する。側によれば、1つのビアは約0.5 pFの分布キャパシタンスをもたらすことができ、ビアの数を減らすことは速度を著しく増加させ、データエラーの可能性を減らすことができる。

3 .近接線と平行に信号線で導入される「クロストーク」に注目する

高周波回路配線は信号線の近接並列ルーティングによって導入された「クロストーク」に注目すべきである。クロストークは直接接続されていない信号線間の結合現象を指す。高周波信号は伝送線路に沿って電磁波の形で伝送されるので、信号線はアンテナとして作用し、電磁界のエネルギーは伝送線の周囲に放出される。望ましくないノイズ信号は、信号間の電磁界の相互結合のために生成される。クロストークと呼ばれる。PCB層のパラメータ、信号線の間隔、駆動端および受信端の電気的特性、および信号線終端方法は、すべて、クロストークに一定の影響を及ぼす。従って、高周波信号のクロストークを低減するためには、配線時にできるだけ以下のことを行う必要がある。

配線スペースが許容される場合、より深刻なクロストークを有する2本のワイヤの間に接地線又はグランドプレーンを挿入することは、分離の役割を果たし、クロストークを低減することができる。

信号線を囲む空間に時分変動する電磁場がある場合、平行分布を回避できない場合には、並列信号線の反対側に「グランド」の大面積を配置して干渉を大幅に低減することができる。

配線スペースが許容されるという前提において、隣接する信号線間の間隔を増大させ、信号線の平行長を短くし、並列の代わりにキー信号線に垂直にクロックラインを作るようにしている。

同じ層内の平行配線がほとんど避けられない場合、2つの隣接する層では、配線の方向は互いに垂直でなければならない。

ディジタル回路では、通常のクロック信号は、高いエッジクロストークを有する高速エッジ変化を有する信号である。したがって、設計においては、クロックラインを接地線で囲み、より多くの接地線孔を打ち抜き、容量を減少させてクロストークを低減する。

高周波信号クロックについては、低電圧差動クロック信号を使用し、接地モードをラップし、パッケージグランドパンチの完全性に注意を払う。

未使用の入力端子は、停止されるべきではなく、電源に接地されるか、または電源に接続されている(電源はまた、高周波信号ループにおいて接地されている)。吊り下げラインは送信アンテナと等価であり、接地は発光を抑制することができるからである。この方法を用いてクロストークを除去することにより、即時の結果をもたらすことがある。

(4)集積回路ブロックの電源ピンに高周波デカップリングコンデンサを加える

各集積回路ブロックの電源ピンには高周波デカップリングコンデンサが付加されている。電源ピンの高周波デカップリングコンデンサを増やすことにより、電源ピン上の高周波高調波の干渉を効果的に抑制することができる。

PCB設計・製造パッケージ

1. スピードアップと改善 PCB配線

従来のPCB配線は、固定線座標とどんな角度ででもワイヤーの不足によって制限されます。これらの制限を除去することにより、配線の品質を大幅に改善することができる。本論文では,任意角度配線の利点,フレキシブル配線の利点,実用例によるスタイナー木構築のための新しいアルゴリズムを紹介する。

2 . PCBダイアグラム描画時の溶接の観点から

手動溶接を置き換えることができるより洗練された配置マシンがありますが、溶接の品質に影響を与えるあまりにも多くの要因があります。パッチはんだ付けの観点からpcb設計時に留意すべき点を紹介した。経験によると、これらの要件が続かない場合は、PCB修復中に半田付け品質、偽はんだ付け、およびはんだ付けに対してさえ損傷が生じる可能性が高い。ディスクまたは回路基板。

PCB描画時の配線技術と要点

配線は、最高級で最も制限的な技術です PCB設計 プロセス. 若干の良い配線技術と要点は、ここにあります.

DDR 3メモリのPCBシミュレーションと設計

信号完全性に影響する主因子をddr 3タイミングに対して解析し,解析結果を用いて設計を改善し最適化した。