Công nghệ cắt các đơn vị riêng lẻ từ wafer và sau đó đóng gói chúng đã là đặc điểm kỹ thuật để đóng gói các mạch tích hợp bán dẫn trong nhiều thập kỷ. Tuy nhiên, do chi phí sản xuất cao và các thành phần RF ngày càng tăng của các mô-đun ngày nay, phương pháp này không được các nhà sản xuất bán dẫn lớn áp dụng. Do đó, sự ra đời của gói cấp wafer (WLP) đã dẫn đến một sự thay đổi mô hình trong việc phát triển gói chi phí thấp. WLP là công nghệ đóng gói cấp wafer trước khi cắt các thiết bị đóng gói wafer.

Sử dụng các công cụ và quy trình tiêu chuẩn, WLP hoạt động như một phần mở rộng của quy trình sản xuất wafer. Cuối cùng, WLP DIE được sản xuất sẽ có các miếng kim loại trên bề mặt chip và các mối hàn được lắng đọng trên mỗi miếng trước khi cắt chip. Điều này làm cho WLP tương thích với quy trình lắp ráp PCB truyền thống và cho phép kiểm tra thiết bị trên chính wafer. Do đó, đây là một quy trình tương đối rẻ và hiệu quả, đặc biệt là khi kích thước chip tăng và chip DIE co lại. Kích thước của wafer đã tăng lên trong vài thập kỷ qua, từ 4 inch, 6 inch và 8 inch đường kính lên 12 inch. Điều này dẫn đến sự gia tăng số lượng DIE trên mỗi chip, do đó giảm chi phí sản xuất. Về hiệu suất điện, WLP vượt trội so với các công nghệ đóng gói khác vì một khi thiết bị WLP được tích hợp vào các mô-đun RF dày đặc, nó làm giảm đáng kể khớp nối ký sinh EM vì kết nối giữa thiết bị và PCB tương đối ngắn, không giống như kết nối liên kết chì được sử dụng trong một số loại công nghệ CSP.

Công nghệ chip WLP

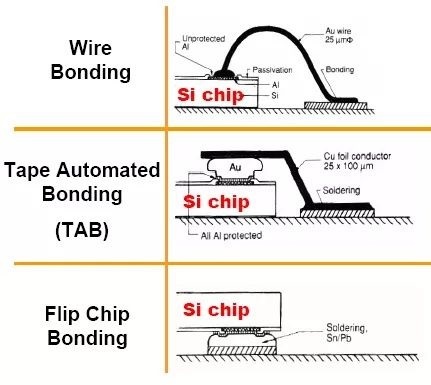

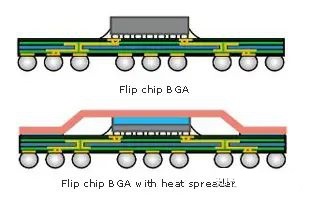

Công nghệ chip đảo ngược, còn được gọi là kết nối chip gấp có thể điều khiển (C4), là một trong một số công nghệ lắp ráp chip được IBM phát triển vào những năm 1960. Mặc dù công nghệ đóng gói dựa trên liên kết chì linh hoạt hơn về khả năng cảm ứng tự do để gỡ lỗi trong phòng thí nghiệm sau khi xây dựng phần cứng và cũng cung cấp độ dẫn nhiệt tốt, việc sử dụng hàn trong công nghệ đóng gói chip đảo ngược làm cho kết nối điện giữa lớp lót đóng gói và chip cung cấp giảm kích thước tương đối, giảm độ trễ, Và cách ly tốt hơn về pin đầu vào và đầu ra của nó. Hình 1 cho thấy cấu trúc cơ bản của chip DIE trên chất nền với một quả bóng hàn trên đỉnh của cột Cu phát triển trên bề mặt chip. Các mối hàn thường được đóng gói với các hợp chất khuôn đầy để cung cấp hỗ trợ cơ học cho các mối hàn.

Gói cấp chip WLP

Đóng gói cấp chip (CSP) là một trong những phương pháp đóng gói được sử dụng phổ biến nhất trong ngành công nghiệp vi điện tử và bán dẫn. Trong khi một số loại công nghệ CSP đã có sẵn cho các nhà sản xuất chip, các loại CSP mới vẫn tiếp tục xuất hiện để đáp ứng nhu cầu về các sản phẩm hỗ trợ các tính năng mới và ứng dụng mới cho các sản phẩm cụ thể. Các yêu cầu đóng gói này có thể khác nhau tùy thuộc vào độ tin cậy cần thiết, chi phí, các tính năng bổ sung và kích thước tổng thể. Như tên cho thấy, kích thước gói của CSP gần giống với kích thước chip DIE, đây là một trong những lợi thế chính của nó. Bằng cách áp dụng quy trình sản xuất WLP, CSP đang phát triển để đạt được tỷ lệ kích thước lõi đóng gói nhỏ nhất có thể. Như thể hiện trong hình 2, loại CSP Ball Grille Array (BGA) trong gói cho phép nhiều kết nối trong khi đơn giản hóa việc định tuyến PCB, cải thiện thông lượng lắp ráp PCB và giảm chi phí sản xuất.

Công nghệ đóng gói khác

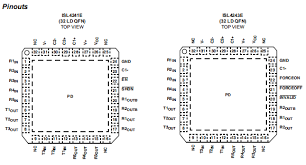

Có một số hình thức khác của gói IC tích hợp cho phép tích hợp liền mạch vào gói mô-đun tùy chỉnh ứng dụng. Bao bì bốn mặt phẳng (QFP) là một trong những công nghệ bao bì IC gắn trên bề mặt sớm nhất, trong đó cấu trúc của bao bì bao gồm bốn mặt với các dây dẫn kết nối mở rộng như trong Hình 3 (a). Các dây dẫn được nâng lên được kết nối với khung gói để tạo thành một tụ điện loại kim loại-cách điện-kim loại (MIM) giữa dây dẫn và kim loại chip DIE, có thể được sử dụng như một phần tử phù hợp. Công nghệ này phù hợp với IC có kích thước milimet, trong đó số lượng chân ngoại vi trong gói có thể lên tới hơn 100. Tùy thuộc vào vật liệu được sử dụng, có một số dẫn xuất của loại bao bì này, chẳng hạn như bao bì phẳng gốm, bao bì phẳng mỏng, bao bì phẳng nhựa (bao bì phẳng nhựa) và bao bì phẳng kim loại (MQFP). QFN, Quad Flat No Lead, thể hiện trong hình. 3 (b) là một trong một số công nghệ đóng gói bề mặt được hình thành từ khung dẫn bằng đồng phẳng và bao bì nhựa được sử dụng làm miếng đệm truyền nhiệt cho bộ tản nhiệt. Mối nối dây dẫn cũng có thể được sử dụng để kết nối, và vì dây nối không chỉ là dây dẫn mà còn là cuộn cảm, chúng thường ảnh hưởng đến hiệu suất của thiết bị theo công nghệ đóng gói này trừ khi chúng được coi là một phần của thiết kế tổng thể. Mặc dù QFN được kết nối với nhau bằng bốn mặt, dây dẫn không dây hai mặt phẳng (DFN) cũng đã xuất hiện và tạo thành hai mặt của dây dẫn mặt phẳng được kết nối với nhau.