Nguyên tắc đóng gói mạch tích hợp 3D và ứng dụng

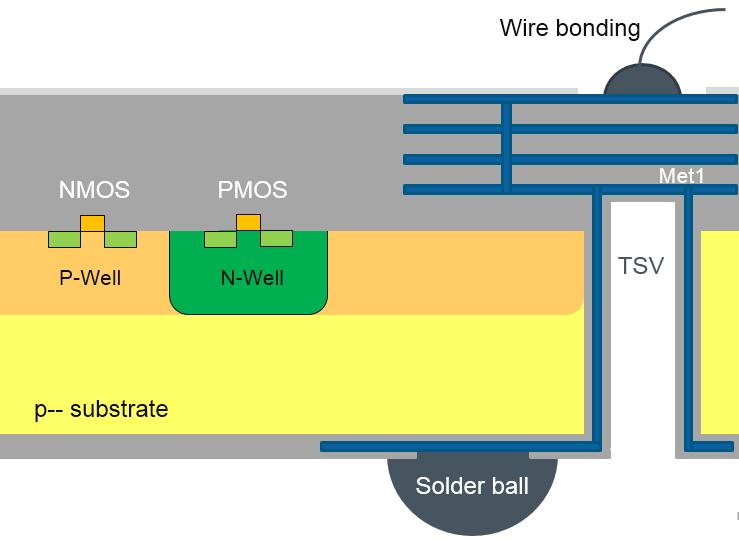

Lớp điện môi 2.5D là cấu hình trong đó các lõi được gắn cạnh nhau trên lớp điện môi silicon, thủy tinh hoặc hữu cơ bằng cách sử dụng một lỗ thông qua silicon (TSV) đi qua lớp điện môi. (Khi thủy tinh hoặc tấm laminate hữu cơ được sử dụng làm cơ sở cho lớp giữa, chúng được gọi là xuyên qua kính (TGV) và xuyên qua cơ sở (TSV), tương ứng.) Giao tiếp giữa các lõi được thực hiện thông qua các mạch được sản xuất trên các lớp trung gian.

Cảm biến hình ảnh CMOS (CIS) có TSV làm lỗ phía sau để tạo kết nối, loại bỏ sự kết hợp phím chì, do đó giảm kích thước và tăng mật độ. Trong tất cả các loại gói 3D, các chip trong gói sử dụng tín hiệu ngoài chip để giao tiếp như thể chúng được gắn trong một gói riêng biệt trên một bảng mạch thông thường.

IC 3D có thể được chia thành IC xếp chồng 3D (3D-sic), có nghĩa là chip IC được xếp chồng lên nhau và kết nối với TSV; Các IC 3D thực sự sử dụng quy trình FAB để xếp nhiều lớp thiết bị trên một chip duy nhất và có thể hoặc không sử dụng TSVS cách nhau rất tốt để tạo thành kết nối.

Silicon Through the Hole (TSV) là một lỗ được hình thành trên một tấm silicon bằng cách sử dụng quá trình khắc. Kết nối được hình thành bằng cách lấp đầy TSV với các vật liệu dẫn điện như đồng, vonfram hoặc silicon đa tinh thể (Hình 2). Ưu điểm chính của kết nối TSV là chúng rút ngắn đường đi của tín hiệu từ chip này sang chip tiếp theo hoặc từ lớp mạch này sang lớp mạch khác. Điều này cho phép khả năng giảm công suất và tăng mật độ kết nối, do đó cải thiện chức năng và hiệu suất. Bản thân TSV không phải là IC 3D. Thay vào đó, chúng là cơ sở để kích hoạt các mạch tích hợp ba chiều. Mặt sau cũng được sử dụng trong các thiết bị khác như cảm biến hình ảnh, hệ thống vi cơ điện (MEMS) và chất bán dẫn hợp chất.

Monolithic 3D IC là gì?

Thay vì xếp chồng chip hoặc mô-đun để tạo ra một IC 3D, IC 3D nguyên khối bắt đầu với một chip cơ bản, trên đó các thiết bị FAB truyền thống được thêm vào các lớp bổ sung như silicon tinh thể, các lớp kim loại và các mạch hoạt động và thụ động (Hình 2). Sử dụng các lỗ thông qua nanomet thay vì micron để tạo ra một kết nối dọc giữa các lớp thay vì chip; Tương tự với TSV. Một số phương pháp khác nhau hiện đang được phát triển, chủ yếu cho các ứng dụng bộ nhớ. Integral 3D đôi khi được gọi là Sequential 3D.

Bộ nhớ 3D là gì?

Nhiều phương pháp đã được phát triển để xếp chồng lên nhau vuông góc với hai bộ nhớ không bay hơi (NAND Flash) và bộ nhớ không bay hơi (DRAM). Các phương pháp DRAM bao gồm bộ nhớ băng thông cao (HBM), Hybrid Memory Cube của Micron và RAM tích hợp (DiRAM) của Tezzaron. Tất cả đều dựa trên IC 3D sử dụng TSV (Hình 3). Samsung, Toshiba và nhiều công ty khác đang phát triển bộ nhớ flash NAND 3D dựa trên cách tiếp cận 3D tổng thể.

Lợi thế của công nghệ chèn 2.5D là gì?

Công nghệ 2.5D, ban đầu được phát triển như một công nghệ cầu nối cho các mạch tích hợp 3D, đã phát triển thành một nền tảng đóng gói hứa hẹn sẽ cùng tồn tại với các mạch tích hợp 3D. Không giống như 3D-IC, chỉ có lớp trung gian (không phải chính lõi) yêu cầu TSV để kết nối lõi hoạt động với lớp lót đóng gói. Điều này cho phép sử dụng các thiết kế khuôn mẫu hiện có.

Các trình điều khiển công nghệ chính cho tích hợp 3D là gì?

Trên các nút của chip thế hệ tiếp theo, chi phí gia tăng cho các bước in thạch bản và xử lý chip đã thúc đẩy ngành công nghiệp tìm kiếm các giải pháp thay thế để cải thiện hiệu suất và chức năng của các thiết bị điện tử của chúng tôi và giảm chi phí. Ngoài ra, nhu cầu tích hợp nhỏ các công nghệ khác nhau (logic, bộ nhớ, RF, cảm biến, v.v.) đang thúc đẩy ngành công nghiệp tích hợp 3D như một giải pháp.

Các trình điều khiển thị trường cho tích hợp 3D là gì?

Động lực thị trường cho tích hợp 3D (tích hợp 3D) bắt đầu với máy tính cao cấp, máy chủ và trung tâm dữ liệu, quân sự và hàng không vũ trụ và thiết bị y tế vì chúng có nhu cầu lớn nhất và có thể chịu được chi phí của công nghệ tích hợp 3D hiện tại. Máy tính bảng, điện thoại thông minh và thiết bị chơi game cũng đang thúc đẩy công nghệ này.

Những thách thức nào đối với IC 3D?

Mặc dù nhiều người tuyên bố rằng không còn thách thức kỹ thuật nào còn lại và các vấn đề còn lại có thể dễ dàng được giải quyết, một số bước quy trình vẫn yêu cầu các giải pháp tốt hơn, chẳng hạn như công cụ thiết kế để lập kế hoạch, thực hiện và xác minh mạch tích hợp 2.5D và 3D, xử lý chip, quản lý nhiệt và thử nghiệm. Thách thức chính là chi phí đơn vị hiện tại, số lượng thấp và rủi ro thực hiện do sự trưởng thành của hệ sinh thái. Các nỗ lực đang được thực hiện để giảm chi phí quy trình và hợp lý hóa sự hợp tác trong toàn ngành. Tăng sản lượng sẽ giúp giảm chi phí. Tuy nhiên, nhiều chuyên gia 3D tin rằng việc triển khai mạch tích hợp 3D sẽ giảm đáng kể chi phí hệ thống, trong khi thách thức còn lại là giáo dục các kỹ sư cấp hệ thống về lợi ích của việc thiết kế mạch tích hợp 3D trong hệ thống của họ.

Cảm biến hình ảnh CMOS (CIS) là một trong những thiết bị đầu tiên đạt được số lượng lớn các lỗ thông qua. CIS (BSI) với ánh sáng mặt sau hiện đang được sản xuất và vì CIS được xếp chồng lên nhau trên IC, nó là một thiết bị IC 3D (Hình 2). Xilinx đã giới thiệu thiết kế plugin 2.5D vào năm 2011 cho tất cả các FPgas có thể lập trình của dòng Virtex-7. Trong vài năm qua, Tezzaron đã cung cấp một lượng nhỏ DiRAM.

Vào cuối năm 2014, Micron và Samsung sẽ bắt đầu sản xuất Hybrid Storage Cube (HMCS), một ngăn xếp DRAM 3D nằm trên các thiết bị logic. SK Hynix sẽ cung cấp cả HMC và bộ nhớ băng thông cao (HBM). Các thiết bị lưu trữ tích hợp 3D này được sản xuất hàng loạt vào năm 2014/15 và tiếp tục sử dụng các thiết bị ngăn xếp logic và không đồng nhất trong những năm sau đó.

iPCB sẽ chia sẻ tất cả với bạn!