Ngoài các quy trình tiên tiến, bao bì tiên tiến đã trở thành một công nghệ quan trọng để tiếp tục Định luật Moore. Trong những năm gần đây, các công nghệ như 2.5D, 3D và chip đã trở thành chủ đề nóng trong ngành công nghiệp bán dẫn. Làm thế nào chính xác đóng gói tiên tiến đóng một vai trò quan trọng trong việc duy trì Định luật Moore? Các tính năng của công nghệ đóng gói như 2.5D, 3D và Chiplets là gì?

Các ứng dụng như trí tuệ nhân tạo, mạng xe hơi, 5G đã xuất hiện và tất cả đều yêu cầu chip chức năng tiên tiến sử dụng tính toán tốc độ cao, truyền tốc độ cao, độ trễ thấp và tiêu thụ năng lượng thấp. Tuy nhiên, làm thế nào để duy trì Định luật Moore là một thách thức đối với ngành công nghiệp bán dẫn khi nhu cầu tính toán tăng theo cấp số nhân.

Theo độ khó thu nhỏ chip càng lúc càng lớn, tích hợp dị cấu đúng thời cơ mà sinh ra.

Nói cách khác, quá trình bán dẫn tiên tiến đang tiến tới 7nm, 5nm và sau đó là 3nm và 2nm. Do đó, kích thước của transistor đang tiến gần đến giới hạn thể tích vật lý của nguyên tử. Các hạn chế về điện tử và vật lý cũng khiến các quy trình tiên tiến ngày càng khó tiếp tục thu nhỏ và nâng cấp.

Do đó, ngoài việc tiếp tục phát triển các quy trình tiên tiến, ngành công nghiệp bán dẫn cũng đang tìm kiếm những cách khác để giữ cho chip nhỏ và hiệu quả. Thiết kế bố cục của chip đã trở thành một giải pháp mới để tiếp tục Định luật Moore và khái niệm Hệ thống Kiến trúc Thiết kế Tích hợp Không đồng nhất (HIDAS) đã ra đời như một động lực đổi mới cho chip mạch tích hợp.

Cái gọi là tích hợp không đồng nhất, theo nghĩa rộng, là thông qua đóng gói, xếp chồng 3D và các công nghệ khác, bộ nhớ+chip logic, quang điện+linh kiện điện tử và hai loại chip khác nhau được tích hợp với nhau. Nói cách khác, việc tích hợp hai chip với quy trình khác nhau và hiệu suất khác nhau có thể được gọi là tích hợp không đồng nhất.

Do thị trường ứng dụng đa dạng hơn, chi phí, hiệu suất và dân số mục tiêu của mỗi sản phẩm là khác nhau, do đó các công nghệ tích hợp không đồng nhất cần thiết cũng khác nhau và xu hướng tập trung thị trường dần xuất hiện. Do đó, ngành công nghiệp thiết bị IC, sản xuất và bán dẫn đã đầu tư vào phát triển tích hợp không đồng nhất, và các công nghệ đóng gói phổ biến như 2.5D, gói 3D, Chiplets, tất cả đều dựa trên ý tưởng tích hợp không đồng nhất, chẳng hạn như chồi mùa xuân tràn đầy ý nghĩa.

Gói 2.5D có hiệu quả giảm chi phí sản xuất chip

Trước đây, để tích hợp chip với nhau, hầu hết các công nghệ hệ thống trong gói (SiP) được sử dụng như gói PiP (gói trong gói) và gói PoP (gói trên gói). Tuy nhiên, là một ứng dụng như điện thoại thông minh, AIoT và các ứng dụng khác, không chỉ đòi hỏi hiệu suất cao hơn mà còn duy trì khối lượng nhỏ, tiêu thụ điện năng thấp, trong trường hợp này, chúng ta phải tìm cách xếp nhiều chip hơn để giảm khối lượng, do đó, công nghệ đóng gói hiện tại, ngoài SiP ban đầu, đang hướng tới công nghệ đóng gói ba chiều.

Tóm lại, đóng gói ba chiều có nghĩa là sử dụng một lớp trung gian silicon (lớp trung gian silicon) được làm trực tiếp từ các tấm silicon, thay vì sử dụng "chất mang dây" nhựa trước đây và đóng gói một số chip với các chức năng khác nhau trực tiếp vào một chip hiệu quả hơn. Nói cách khác, các tấm silicon được thêm vào silicon để tăng chi phí và hạn chế vật lý của quá trình để giữ cho Định luật Moore hoạt động.

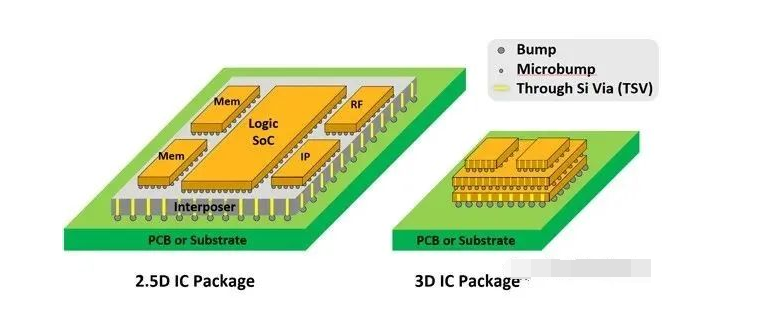

Gói stereo quen thuộc hơn là gói 2.5D và 3D, ở đây chúng tôi bắt đầu với gói 2.5D. Cái gọi là gói 2.5D, khái niệm chính là bố trí bộ vi xử lý, bộ nhớ hoặc các chip khác trên bộ chèn silicon, được kết nối thông qua các vi lồi, cho phép các dây kim loại bên trong bộ chèn silicon kết nối tín hiệu điện tử từ các chip khác nhau. TSV sau đó được sử dụng để kết nối các vết lồi kim loại thấp hơn và các tấm mang dây được sử dụng để kết nối các quả bóng kim loại bên ngoài để đạt được kết nối chặt chẽ hơn giữa chip, chip và chất nền gói.

Bao bì 2.5D và 3D là công nghệ đóng gói stereo phổ biến hiện nay. (Nguồn: ANSYS)

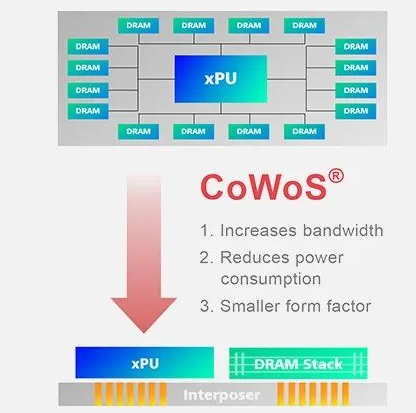

Công nghệ đóng gói 2.5D nổi tiếng hiện nay không gì khác ngoài CoWoS của TSMC. Khái niệm về công nghệ CoWoS là đặt các chip bán dẫn (như bộ xử lý, bộ nhớ, v.v.) trên lớp trung gian silicon và sau đó kết nối chúng với chất nền dưới cùng thông qua quá trình đóng gói chip trên wafer (CoW). Nói cách khác, đầu tiên, chip được kết nối với chip silicon thông qua quá trình đóng gói của chip trên chip (CoW), sau đó chip CoW được kết nối với chất nền và tích hợp vào CoWoS. Sử dụng chế độ đóng gói này, nhiều chip có thể được đóng gói lại với nhau và được kết nối với nhau bằng bộ chèn silicon, do đó đạt được hiệu quả của khối lượng đóng gói nhỏ, tiêu thụ điện năng thấp và pin ít hơn.

Ý tưởng kỹ thuật đóng gói của Đài Tích Điện. (Nguồn: TSMC)

Ngoài CoWos, gói cấp wafer quạt ra cũng có thể được phân loại là một phương pháp cho gói 2.5D. Nguyên tắc của gói cấp wafer quạt là kéo mạch mong muốn từ đầu của chất bán dẫn trần đến lớp phân phối lại để tạo thành gói. Do đó, không cần phải niêm phong tấm tải, dây dẫn, lồi, có thể giảm chi phí sản xuất xuống 30% và cũng có thể làm cho chip mỏng hơn. Đồng thời, diện tích chip có thể được giảm đáng kể. Nó cũng có thể thay thế các lỗ thủng silicon xuyên chi phí cao hơn, cho phép tích hợp các thành phần khác nhau thông qua công nghệ đóng gói.

Tất nhiên, công nghệ đóng gói stereo không chỉ là 2.5D, mà còn là đóng gói 3D. Vì vậy, sự khác biệt giữa hai, ngành công nghiệp bán dẫn đang áp dụng bao bì 3D?

So với gói 2.5D, gói 3D hoạt động bằng cách tạo ra cấu trúc bóng bán dẫn (CMOS) trên chip và sử dụng các lỗ silicon để kết nối tín hiệu điện tử của các chip khác nhau lên và xuống, do đó bộ nhớ hoặc các chip khác có thể được xếp chồng lên nhau theo chiều dọc trực tiếp

Gói 3D là một ngăn xếp trực tiếp của chip. (Nguồn: Intel)

TSMC và Intel tích cực phát triển công nghệ đóng gói 3D

Intel (INTC) và Taiwan Semiconductor (TSMC) có công nghệ đóng gói 3D tương ứng. Intel đang sử dụng công nghệ đóng gói 3D "Foveros", sử dụng logic ngăn xếp không đồng nhất để xử lý các hoạt động và có thể xếp từng chip logic lại với nhau. Điều này có nghĩa là lần đầu tiên, việc xếp chồng chip đã được mở rộng từ phương tiện truyền thông silicon thụ động truyền thống và bộ nhớ xếp chồng lên các sản phẩm logic hiệu quả cao như CPU, đồ họa và bộ xử lý AI. Trước đây, ngăn xếp chỉ được sử dụng cho bộ nhớ, nhưng bây giờ ngăn xếp không đồng nhất được sử dụng để cho phép ngăn xếp các kết hợp khác nhau của bộ nhớ và chip tính toán.

Ngoài ra, Intel đang phát triển ba công nghệ mới là co-EMIB, ODI và MDIO. Co-emib có thể kết nối hiệu suất và khả năng tính toán cao hơn và cho phép hai hoặc nhiều thành phần Foveros được kết nối với nhau. Các nhà thiết kế cũng có thể kết nối các trình mô phỏng, bộ nhớ và các mô-đun khác với băng thông rất cao và mức tiêu thụ điện năng rất thấp. Công nghệ ODI cung cấp tính linh hoạt cao hơn cho truyền thông kết nối toàn diện giữa các chip vừa và nhỏ. Chip trên có thể giao tiếp với các chip nhỏ khác như công nghệ EMIB hoặc theo chiều dọc với chip trần phía dưới thông qua lỗ silicon (TSV) như công nghệ Foveros.

Khái niệm công nghệ Foveros của Intel (Nguồn: Intel)

Công nghệ này cũng sử dụng các lỗ thông qua thẳng đứng lớn, cung cấp năng lượng trực tiếp từ chất nền đóng gói cho các tấm trần trên cùng. Những lỗ thông lớn này lớn hơn nhiều so với các lỗ thông qua silicon thông thường và cung cấp truyền tải điện ổn định hơn với điện trở thấp hơn. Và đạt được băng thông cao hơn và độ trễ thấp hơn thông qua ngăn xếp. Phương pháp này làm giảm số lượng lỗ silicon cần thiết trong chip cơ sở, giải phóng diện tích lớn hơn cho các yếu tố hoạt động và tối ưu hóa kích thước của tấm trần.

Mặt khác, TSMC đang đề xuất giải pháp tích hợp "chip tích hợp đa chip và hệ thống 3D" (SoIC). Các giải pháp tích hợp hệ thống trên chip chồng lên nhau trực tiếp các tinh thể trần tốt được biết đến với các kích cỡ khác nhau, công nghệ xử lý và vật liệu.

TSMC lưu ý rằng các chip tích hợp của hệ thống có mật độ và tốc độ lồi cao gấp nhiều lần so với các giải pháp mạch tích hợp 3D truyền thống sử dụng microbucks, đồng thời giảm đáng kể mức tiêu thụ điện năng. Ngoài ra, một chip tích hợp hệ thống là một giải pháp tích hợp tiền xử lý để kết nối hai hoặc nhiều tinh thể trần trước khi đóng gói; Do đó, chipset tích hợp hệ thống có thể sử dụng công nghệ đóng gói tiên tiến InFO hoặc CoWoS back-end của công ty để tích hợp thêm các chip khác, tạo ra các giải pháp cấp hệ thống 3D * 3D mạnh mẽ.

Ngoài ra, TSMC đã giới thiệu 3DFabric, tập hợp các giải pháp tích hợp hệ thống 3DIC đang phát triển nhanh chóng để cung cấp tính linh hoạt cao hơn và tạo ra các hệ thống mạnh mẽ được kết nối trên các mảng lớn mạnh mẽ. Với các tùy chọn đóng gói chip phía trước và phía sau khác nhau, 3DFabric giúp khách hàng kết nối nhiều chip logic với nhau, ngay cả các chip nhỏ không đồng nhất như bộ nhớ rộng tần số cao (HBM) hoặc mô-đun analog, đầu vào/đầu ra và RF. 3DFabric kết hợp các giải pháp 3D ở mặt sau và mặt trước và bổ sung các mô hình thu nhỏ transistor để liên tục cải thiện hiệu suất và chức năng của hệ thống, giảm kích thước và ngoại hình và đẩy nhanh thời gian đưa sản phẩm ra thị trường.

Sau sự ra mắt của 2.5D và 3D, Chiplets là một trong những công nghệ đóng gói tiên tiến nhất đang tác động đến ngành công nghiệp bán dẫn. Cuối cùng, tóm tắt ngắn gọn về các tính năng và lợi ích của Chiplets.

Có ba lợi ích khi sử dụng Chiplets. Bởi vì chi phí của các quy trình tiên tiến là rất cao, đặc biệt là mạch analog và I/O ngày càng khó thu hẹp khi công nghệ quy trình phát triển. Các chip chia mạch thành các chip nhỏ độc lập, tăng cường chức năng, công nghệ xử lý và kích thước của chúng và cuối cùng tích hợp chúng lại với nhau để vượt qua những thách thức của việc thu nhỏ quy trình. Ngoài ra, Chiplets có thể sử dụng các chip trưởng thành hiện có để giảm chi phí phát triển và xác minh.

Hiện nay, nhiều nhà sản xuất chất bán dẫn đã giới thiệu các sản phẩm hiệu suất cao theo cách chip. Ví dụ, Intel Stratix 10 GX 10M FPGA của Intel có thiết kế chip cho phép mật độ và dung lượng linh kiện cao hơn. Sản phẩm này dựa trên kiến trúc Intel Stratix 10 FPGA hiện có và công nghệ cầu nối đa chip nhúng (emib) tiên tiến của Intel, tích hợp hai chip logic lõi Intel Stratix 10 GX FPGA mật độ cao và các đơn vị I/O tương ứng bằng công nghệ emib. Điều này cũng đúng với bộ vi xử lý dòng epyc thế hệ thứ hai của AMD. Không giống như cách tiếp cận chip thế hệ đầu tiên kết hợp bộ nhớ và I/O để tạo thành CPU 14 nm, thế hệ thứ hai là tách I/O và bộ nhớ thành một chip và cắt CPU 7 nm thành 8 chip để kết hợp.

Tóm lại, trong quá khứ, hiệu suất chip đã được cải thiện thông qua những cải tiến trong quy trình bán dẫn, nhưng việc thu nhỏ chip ngày càng trở nên khó khăn hơn khi kích thước của các thành phần tiếp cận giới hạn vật lý. Để duy trì kích thước nhỏ và thiết kế chip hiệu quả cao, ngành công nghiệp bán dẫn không chỉ tiếp tục phát triển các quy trình tiên tiến mà còn cải thiện kiến trúc chip, cho phép chip chuyển từ lớp đơn ban đầu sang ngăn xếp nhiều lớp. Do đó, bao bì tiên tiến cũng trở thành một trong những động lực chính để cải thiện Định luật Moore, dẫn đầu xu hướng trong ngành công nghiệp bán dẫn.

Công việc chính của Phòng thí nghiệm Trí tuệ nhân tạo trong tương lai bao gồm: Xây dựng hệ thống đánh giá IQ của hệ thống Trí tuệ nhân tạo, triển khai đánh giá IQ của Trí tuệ nhân tạo thế giới; Triển khai chương trình nghiên cứu não bộ đám mây Internet (thành phố), xây dựng công nghệ não bộ đám mây Internet (thành phố) và bản đồ doanh nghiệp, dịch vụ nâng cao trình độ thông minh hóa của doanh nghiệp, ngành nghề và thành phố.