Der Lötstellenabstand von WLP- und WLCSP-Komponenten ist recht klein. Unterschiedliche Lötpads begrenzen auch die Spurbreite zwischen Lötstellen. Es gibt mehr Einschränkungen beim Design der Leiterplatte.

Mit der Chipgrößenverpackung auf Wafer-Ebene von WLP und WLCSP, Die Effektivität von miniaturisierten Chips ist immer wichtiger geworden, und die Verwendung elektronischer Produkte hat auch weiterhin zugenommen. Allerdings, Obwohl WLP und WLCSP nach dem Verpacken die Größe des Chips erreichen können Genauso wie die hervorragenden Vorteile der gleichen Größe und Größe der Matrize, Die Funktionen der verpackten Produkte werden immer komplexer, Die Anzahl der Stifte und die Designanforderungen werden immer strenger, und die PCB-Design ist zu einer neuen Anwendungsherausforderung geworden...

WLP (Wafer Level Packaging) und WLCSP (Wafer Level Chip Scale Package) sind eigentlich eine Verpackungsmethode von integrierten Schaltungen, die sich direkt auf dem Wafer bezieht, nachdem die Wafer (Wafer) Produktion abgeschlossen ist. Verpackungs- und Prüfverfahren, wenn die Verpackung abgeschlossen ist, dann in eine einzige integrierte Schaltung Verpackungsherstellung geschnitten.

Die Gehäusekonstruktionskomponenten aus konventionellem IC und WLP unterscheiden sich in der Größe sehr, und WLP benötigt nur die Matrizengröße, um die gleichen elektrischen Eigenschaften zu haben.

WLP führt die Komponentenverpackung in der Waferstufe durch, so dass es keinen Platzbedarf für herkömmliche IC-Pins, Packungskörperfüllung usw. gibt, und die Komponentengröße kann die Matrizengröße erreichen, so dass die PCB-Design-Herausforderungen größer sind.

Nemotek verwendet WLP zur Herstellung von Bildsensormodulen mit einem optischen Linsendesign, das den Platzbedarf des Bildsensormoduls erheblich reduzieren kann. Die Produktion kann schnell mit automatischer Zuführung erfolgen, was Produktionskosten spart.

Samsung verwendet den Bildsensor, der in Form von WLP produziert wird, direkt unter Verwendung von Wafer-Level-Verpackungen, um die Größe der Komponente erheblich zu reduzieren, die Komponente kann extrem dünn und die kleinste Stellfläche sein.

WLP und WLCSP unterscheiden sich von dem Herstellungsverfahren für integrierte Schaltungen, bei dem der Wafer in Matrizen geschnitten wird und dann zusätzliche Pins im Gehäuse verdrahtet werden. Aufgrund des kleineren Platzbedarfs des Pakets können WLP und WLCSP die gleichen IC-Anwendungsfunktionen erreichen, aber solange der Footprint nach dem Schneiden mit der Größe der Matrize übereinstimmt und während der Herstellung eines einzelnen IC aus WLP und WLCSP besteht keine Notwendigkeit, Klebstoff wie gewöhnliche ICs zu verdrahten und zu füllen. Bei der Entwicklung miniaturisierter oder ultrakleiner miniaturisierter Designlösungen können IC-Anwendungen mit WLP- und WLCSP-Verpackungsdesignmethoden hervorragende Produktminiaturisierungsvorteile erzielen. Darüber hinaus besitzen WLP- und WLCSP-Komponenten selbst hervorragende elektrische Eigenschaften (aufgrund fehlender Verdrahtung und Pins), die für Komponenten für Hochgeschwindigkeits-Übertragungsanwendungen verwendet werden. Die Effizienz ist höher, da die Komponenten auf dem Wafer verarbeitet werden können, wird auch der umständliche Herstellungsprozess von IC reduziert.

Aber hier kommt das Problem. Obwohl WLP und WLCSP relativ klein sind, sind mit der steigenden Anzahl von Pins herkömmlicher ICs die Anforderungen an die Kugelbahn für WLP- und WLCSP-Verpackungen strenger geworden, aber die elektrischen Eigenschaften, die für den Schaltungsdesign erforderlich sind Grundsätzlich unterscheidet es sich nicht von der elektrischen Unterstützung, die von allgemeinen ICs benötigt wird, aber die Größe von WLP und WLCSP wurde auf die Matrizengröße reduziert. Zudem sind die Kontakte und Schaltungen, die mit WLP und WLCSP an die Leiterplatte angeschlossen werden können, extrem klein. Bei der Gestaltung von Leiterplatten Die Lösung ist nicht so einfach wie die allgemeine IC-Anwendungslösung.

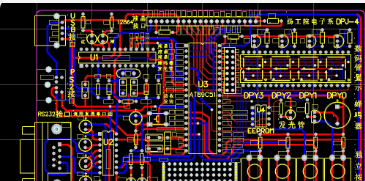

Was die Verwendung von Verpackungen auf Waferebene angeht, Ziel ist es, die Kosten und Gesamtgröße der Lösung zu reduzieren, aber wenn die Wafer-Level-Verpackung eingeführt wird, Die Kosten für die Leiterplatte sind zwangsläufig auf die Verwendung von Wafer-Level-Verpackungen zurückzuführen, und entsprechende Verkabelung muss durchgeführt werden. Mit der Verbesserung des Stanzprozesses, die PCB-Eigenschaften ohne Verbindungsprobleme vollständig mit WLP- und WLCSP-Komponenten abgestimmt werden. Vor allem nachdem WLP und WLCSP im Design-Schema verwendet werden, PCB wird komplizierter und seine Rolle wird wichtiger werden. Während des Designs ist eine sorgfältige Planung erforderlich, um die Stabilität des Endprodukts durch die Qualität der Leiterplatte zu vermeiden.

Komponentenverpackung in der Waferphase spart den Platzbedarf der Trägerplatte erheblich

Da WLP- und WLCSP-Verpackungen direkt auf dem "Silizium"-Substratverpackungsprozess aufgebaut sind, muss IC grundsätzlich keine Bonddrähte verwenden, für Hochfrequenzkomponenten kann es direkt bessere hochfrequente elektrische Eigenschaften erhalten und den Vorteil der Verkürzung der Zykluszeit erzielen. Und weil die Verpackung in der Fabrik fertiggestellt werden kann und die Verpackungskosten gleichzeitig eingespart werden können, aber für den Ingenieur muss der Konstruktionsplan auch in Richtung Kostensenkung betrachtet werden. Um WLP- und WLCSP-Komponenten aufeinander abzustimmen, müssen auch die Leiterplattenkosten in gewissem Umfang begrenzt werden. Achten Sie auf das Kompromissdesign oder nehmen Sie das entsprechende Schaltungslayout an.

Im Allgemeinen müssen Ingenieure, um WLP- und WLCSP-Komponenten zu importieren, bevor sie PCB-Layoutplanung ausführen, zuerst den Footprint von WLP und WLCSP (dh Paketgröße) erhalten und gleichzeitig den Größe-/Kontaktfehler und Kontakt von WLP- und WLCSP-Komponenten bestätigen. Für kritische Komponenteninformationen wie Pitch, Startschaltungslayout und Prozesskomponentenplazierung, Sie können die erhaltenen Komponentenparameter zur Konstruktion und Planung verwenden. Da die Größe und Kontakte von WLP und WLCSP kleiner werden, müssen Sie auch das Löten der entsprechenden IC-Pins berücksichtigen. Mattendesign.

PCB muss für SMD- und NSMD-Formen fein abgestimmt werden

Es kann mit WLP- und WLCSP-Pad-Typen abgestimmt werden, und Lötmasken-Defined (SMD) und Nonsolder Mask Defined (NSMD) können verwendet werden. Die Lötmaskendefinitionsart SMD Lötpad ist so konzipiert, dass die Lötmaske verwendet wird, um die Lötballe und den Bereich des Lötpads zu definieren, das gelötet werden soll. Diese Konstruktionslösung kann die Möglichkeit verringern, dass der Lötpad während des Löt- oder Entlötprozesses hochgezogen wird. Der Nachteil der SMD-Form ist jedoch, dass SMD die Oberfläche der mit der Lötkugel verbundenen Kupferoberfläche reduziert und gleichzeitig den Raum zwischen den benachbarten Pads reduziert, wodurch die Breite der Spur zwischen den Pads begrenzt wird und die Leiterplatte auch eingeschaltet wird.Das Loch verwendet Elastizität. In den meisten Entwurfsschemata ist das am häufigsten verwendete immer noch das SMD-Entwurfsschema, da die Lötpads des SMD bessere Lötverbindungseigenschaften haben können und das Lot und die Lötpads während des Herstellungsprozesses zusammen integriert werden können.

Was das nicht-lötende Masken-definierte Lötpad (NSMD) betrifft, so besteht die Konstruktionsmethode darin, Kupfer für das Lötbufflöten zu verwenden, um den Lötpad-Bereich zu definieren. Diese Entwurfslösung kann eine größere Oberfläche bieten, um die Leiterplatte und die Lötkugel zu verbinden. Gleichzeitig bietet NSMD im Vergleich zur SMD-Designform auch einen größeren Isolationsabstand zwischen den Lötpads und den Lötpads, was einen größeren Verdrahtungsabstand zwischen den Lötpads ermöglicht und eine höhere Flexibilität für die Verwendung von Durchgangslöchern der Leiterplatte hat. Wenn der NSMD jedoch lötet, können Entlöten und andere Operationen leicht dazu führen, dass der Lötpad hochgezogen wird.

Besondere Beachtung ist bei Abständen erforderlich

Die Berücksichtigung der Pitchgröße ist auch sehr wichtig, besonders wenn die Leiterplatte in Form von SMD oder NSMD ist, wird die reservierte Pitchgröße von verschiedenen Lösungen auch geringfügig unterschiedlich sein, und die Pitchgröße bezieht sich auf den Abstand zwischen den Lötkugeln, der zwei ist. Je größer der Verdrahtungsraum zwischen dem Lötpad und dem Lötpad, der für die Verdrahtung verwendet werden kann.

In Bezug auf Leiterplattenverdrahtung, aufgrund der Eigenschaften von WLP und WLCSP Komponenten, die verfügbare Lötballhöhe ist recht klein. Grundsätzlich, Es ist unmöglich, mechanische Öffnungsgeräte zu verwenden, um Leiterplattenlöcher zu öffnen. Weil der Lochdurchmesser der mechanischen Öffnung zu groß ist, Der Öffnungsvorgang kann auch die Leiterplatte verursachen Die obere dünnere Linie wird durch Fehler im Öffnungsvorgang beschädigt. Allerdings, in Leiterplatten, die WLP- und WLCSP-Komponenten verwenden, weil die Schaltungen viel enger sind, Laserbohrungen, die teurer sind, wird stattdessen verwendet.

Schlussbemerkungen

Die Chipgrößenverpackung auf Wafer-Ebene von WLP- und WLCSP-Komponenten hat einen hervorragenden Verbesserungsvorteil zur Reduzierung der Größe des Endprodukts, muss aber im Austausch für den PCB-Designplan gleichzeitig mit hochdichten Mehrschichtplatinen und präzisen Laseröffnungen aufgerüstet werden. Während der Entwicklung werden der Speicherplatz und die Komponentenkosten, die ursprünglich durch IC-Komponenten eingespart wurden, teilweise auf das PCB-Design und die anschließende Massenproduktion übertragen. Stattdessen werden kleinere Komponenten verwendet, um Teile und Komponenten auf der Produktionslinie auf der Rückseite des Produkts herzustellen. Die Verarbeitung oder Wartung wird auch einige operative Probleme verursachen, die schwieriger zu implementieren sind, die vor dem jeweiligen Design einzeln berücksichtigt werden müssen.