Ein häufiges Problem mit Schaltnetzteilen ist "instabile" Schaltwellenformen. Manchmal, Der Wellenformjitter befindet sich im Klangband, und die magnetischen Komponenten erzeugen Audiorauschen. Wenn das Problem im Layout der Leiterplatte liegt, Es kann schwierig sein, die Ursache zu finden. Daher, die richtige Leiterplattenlayout in der Anfangsphase des Schaltnetzwerks Design ist sehr kritisch. Der Stromversorgungsentwickler muss ein gutes Verständnis für die technischen Details und die funktionalen Anforderungen des Endprodukts haben.

Ein gutes Layout-Design kann die Energieeffizienz optimieren und thermische Belastungen reduzieren; Noch wichtiger ist, dass es Geräusche und die Interaktion zwischen Leiterbahnen und Komponenten minimiert. Um diese Ziele zu erreichen, muss der Konstrukteur den aktuellen Leitungsweg und den Signalfluss innerhalb des Schaltnetzteils verstehen. Um die korrekte Auslegung von nicht isolierten Schaltnetzteilen zu realisieren, müssen folgende Gestaltungselemente beachtet werden.

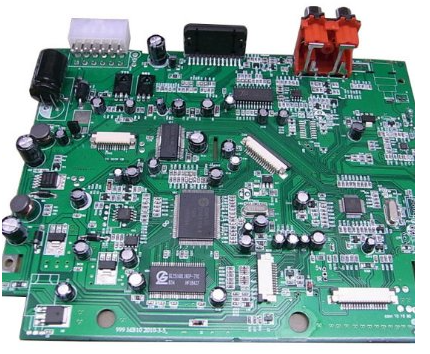

Was sind die Tipps für PCB Layout Design von nicht isolierten Schaltnetzteilen

Layoutplanung?

Entscheidend ist die Planung der Lage der Stromversorgung und des Platzbedarfs an Leiterplatten bereits in den frühen Planungs- und Planungsphasen der Anlage. Manchmal ignorieren Designer diesen Rat und konzentrieren sich auf die "wichtigeren" oder "spannenderen" Schaltungen auf der großen Systemplatine. Das Energiemanagement wird als nachträglicher Gedanke betrachtet, und die Energie wird auf dem zusätzlichen Platz auf der Leiterplatte platziert. Dieser Ansatz ist sehr nachteilig für eine hocheffiziente und zuverlässige Stromversorgung.

Bei Mehrschichtplatinen besteht eine gute Methode darin, eine Gleichstrom-Masseschicht oder Gleichstrom-Eingangs-/Ausgangsspannungsschicht zwischen der Hochstromkomponentenschicht und der empfindlichen kleinen Signalspurenschicht zu platzieren. Die Erdungsschicht oder Gleichspannungsschicht bietet eine AC-Erdungsschicht, die kleine Signalbahnen abschirmt, um Störungen durch rauscharme Stromleitungen und Leistungskomponenten zu verhindern. In der Regel sollten weder die Masseebene noch die Gleichspannungsebene einer mehrschichtigen Leiterplatte getrennt werden. Wenn diese Trennung unvermeidbar ist, versuchen Sie, die Anzahl und Länge der Leiterbahnen auf diesen Ebenen zu reduzieren, und das Layout der Leiterbahnen sollte in der gleichen Richtung wie der hohe Strom gehalten werden, um den Einfluss zu minimieren.

Was sind die Tipps für PCB Layout Design von nicht isolierten Schaltnetzteilen

illustrieren:

Diese Strukturen sandigen die kleine Signalschicht zwischen der Hochstromleistungsschicht und der Masseschicht und erhöhen so das kapazitive Rauschen, das zwischen der Hochstrom-/Spannungsleistungsschicht und der analogen kleinen Signalschicht gekoppelt ist.

(b) and (d) are good structures for six-layer and Vierschichtige Leiterplatte Design bzw. Design, die dazu beitragen, das Kopplungsgeräusch zwischen Schichten zu minimieren, und die Bodenschicht wird verwendet, um die kleine Signalschicht abzuschirmen.

Stellen Sie sicher, dass Sie eine Masseschicht neben die äußere Leistungsschicht legen und dicke Kupferfolie für die externe Hochstrom-Leistungsschicht verwenden, um Leiterplattenleitungsverlust und Wärmewiderstand zu minimieren.

Das Layout der Leistungsstufe?

Der Schaltnetzteil-Schaltkreis kann in zwei Teile unterteilt werden, den Leistungsstufenschalt und den kleinen Signalsteuerkreis. Die Leistungsstufenschaltung enthält Komponenten zur Übertragung großer Ströme. Im Allgemeinen sollten diese Komponenten zuerst platziert werden, und dann sollten Kleinsignal-Steuerkreise an bestimmten Punkten im Layout platziert werden. Hochstrom-Leiterbahnen sollten kurz und breit sein, um die Induktivität, den Widerstand und den Spannungsabfall der Leiterplatte zu minimieren. Für Leiterbahnen mit hohen Di/dt-Pulsströmen ist dieser Aspekt besonders wichtig.

1. Synchroner Buck Konverter Strompfad

Was sind die Tipps für PCB Layout Design von nicht isolierten Schaltnetzteilen

Der kontinuierliche Strompfad und der Impulsstrompfad in einem synchronen Buck-Wandler. Die durchgehende Linie stellt den kontinuierlichen Strompfad und die gestrichelte Linie den Impulsstrompfad (Schalter) dar. Der Impulsstrompfad umfasst Leiterbahnen, die mit folgenden Komponenten verbunden sind: Eingangsentkopplungskeramikkondensator CHF, obere Steuerung FET QT und untere synchrone FET QB sowie optionale parallele Schottky Dioden.

2. Parasitische Induktivität

Was sind die Tipps für PCB Layout Design von nicht isolierten Schaltnetzteilen

Due to the parasitic inductance, Der Pulsstrompfad strahlt nicht nur Magnetfelder aus, sondern erzeugt auch große Spannungsläute und Spitzen auf Leiterplatten-Leiterbahnen und MOSFETs. Um die Leiterplatteninduktivität, the pulse current loop (the so-called thermal loop) should have the smallest circumference when laying out, und seine Spur sollte kurz und breit sein. Der Hochfrequenz-Entkopplungskondensator CHF sollte 0 sein.1μF~10μF, X5R oder X7R dielektrischer Keramikkondensator, it has very low ESL (effective series inductance) and ESR (equivalent series resistance). Larger capacitor dielectrics (such as Y5V) may cause the capacitance value to drop significantly at different voltages and temperatures, also ist es nicht das beste Material für CHF.