1., die Einleitung

Mit der allmählichen Zunahme der Leiterplatte Komplexität des Designs, Analyse der Signalintegrität zusätzlich zur Reflexion, Übersprechen, und EWI, Stabile und zuverlässige Stromversorgung ist eine der wichtigsten Forschungsrichtungen von Designern geworden. Besonders wenn die Anzahl der Schaltgeräte steigt und die Kernspannung abnimmt, Die Schwankung der Stromversorgung wird oft fatale Auswirkungen auf das System haben, Also schlagen die Leute einen neuen Begriff vor: Macht Integrität, PI (power integrity). Auf dem heutigen internationalen Markt, IC-Design ist weiterentwickelt, Aber das Power Integrity Design ist immer noch ein schwaches Glied. Daher, Dieses Papier stellt das Problem der Stromversorgungsintegrität in Leiterplatte, analysiert die Faktoren, die die Integrität der Stromversorgung beeinflussen, und stellt die Optimierungsmethode und den Erfahrungsentwurf vor, um das Problem der Netzversorgungsintegrität in Leiterplatte, die starke theoretische Analyse und praktische technische Anwendungswert hat.

2, die Ursache und Analyse von Stromversorgungsgeräuschen

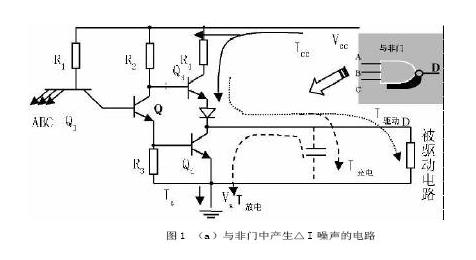

Die Quelle des Stromrauschens wird durch ein NAND Gate Schaltplan analysiert. Der Schaltplan zeigt die Struktur eines Drei-Eingang Nand Gate. Da das NAND Gate ein digitales Gerät ist, Es funktioniert durch Umschalten zwischen "1" und "0" Ebenen. Mit der kontinuierlichen Verbesserung der IC-Technologie, Die Schaltgeschwindigkeit digitaler Geräte ist immer schneller, die mehr Hochfrequenz Komponenten, und die Induktivität in der Schleife ist einfach, die Fluktuation der Stromversorgung bei hoher Frequenz zu verursachen. Wie in Abbildung 1 gezeigt, Wenn der Eingang des NAND-Gates vollständig auf Hochspannung ist, die Triode in der Schaltung schaltet sich ein, die Circuit Shorts sofort, und das Netzteil lädt den Kondensator auf und fließt gleichzeitig in den Erdungskabel. Zur Zeit, wegen der parasitären Induktivität an Stromleitung und Erdungskabel, wir kennen aus der Formel V=LdI/dt, dass dadurch Spannungsschwankungen an der Stromleitung und dem Erdungskabel entstehen, und das δ I-Rauschen, das durch die Pegelsteige hervorgerufen wird, wie in Abbildung 2 gezeigt. Wenn der Eingang des Nand-Gates auf einem niedrigen Strompegel ist, Der Kondensator entlädt sich zu diesem Zeitpunkt, und große δ I Geräusche werden auf dem Erdungskabel erzeugt. Zur Zeit, Das Netzteil hat nur die Strommutation, die durch den augenblicklichen Kurzschluss des Schaltkreises verursacht wird, weil der Kondensator nicht geladen wird, Die aktuelle Mutation ist kleiner als die steigende Kante. Aus der Analyse der Schaltung von NAND Gate, Wir wissen, dass die Quelle der Spannungsversorgungsinstabilität hauptsächlich in zwei Aspekten liegt: Einer ist der Hochgeschwindigkeitsschaltzustand des Geräts, der transiente Wechselstrom ist zu groß.

Die zweite ist die Induktivität, die in der Stromschleife vorhanden ist. Das so genannte Erdstromintegritätsproblem bezieht sich auf Hochgeschwindigkeits-PCB wenn eine große Anzahl von Chips gleichzeitig ein- oder ausgeschaltet ist, großer transienter Strom wird in der Schaltung erzeugt, und die Spannungsschwankung wird sowohl auf der Stromleitung als auch auf der Erdleitung aufgrund des Vorhandenseins von Induktivitätswiderständen erzeugt. Verständnis der Art des Problems der Netzintegrität, Wir wissen, dass, um das Problem der Stromversorgung Integrität zu lösen, vor allem, für Hochgeschwindigkeitsgeräte, Wir fügen einen Entkopplungskondensator hinzu, um seine Hochfrequenz Geräuschkomponente, Verringerung der Übergangszeit des Signals; Für die in der Schleife vorhandene Induktivität, Wir müssen das mehrschichtige Design der Stromversorgung berücksichtigen.

3, die Anwendung des Entkopplungskondensators

Entkopplungskondensatoren spielen eine wichtige Rolle beim Hochgeschwindigkeits-PCB-Design, und ihre Platzierung ist auch sehr wichtig. Dies liegt daran, dass, wenn das Netzteil die Last für kurze Zeit mit Strom versorgt, die Speicherladung im Kondensator den Spannungsabfall verhindern kann, wie eine falsche Kondensatorposition die Leitungsimedanz zu groß machen kann, was die Stromversorgung beeinträchtigt. Gleichzeitig kann der Kondensator das hochfrequente Rauschen während des Hochgeschwindigkeitsschaltes des Geräts filtern. Im Hochgeschwindigkeits-PCB-Design fügen wir im Allgemeinen einen Entkopplungskondensator am Ausgangsende der Stromversorgung bzw. am Eingangsende der Stromversorgung des Chips hinzu. Der Kapazitätswert in der Nähe der Stromversorgung ist im Allgemeinen größer (z.B. 10μF). Dies liegt daran, dass die DC-Stromversorgung im Allgemeinen in PCB verwendet wird, und die Resonanzfrequenz des Kondensators kann relativ niedrig sein, um das Rauschen der Stromversorgung zu filtern. Gleichzeitig kann große Kapazität die Stabilität des Netzteilausgangs gewährleisten. Für den Chip, der an die Stromversorgung der Pin-Position des Entkopplungskondensators angeschlossen ist, ist sein Kapazitätswert im Allgemeinen klein (wie z. B. 0.1μF), weil in Hochgeschwindigkeits-Chips die Rauschfrequenz im Allgemeinen relativ hoch ist, was erfordert, dass die zusätzliche Entkopplungskondensator-Resonanzfrequenz hoch ist, das heißt, die Kapazität des Entkopplungskondensators klein ist.

Was die Platzierung des Entkopplungskondensators betrifft, wissen wir, dass eine falsche Position die Leitungsimedanz erhöht, seine Resonanzfrequenz verringert und die Stromversorgung beeinflusst. Für den Entkopplungskondensator und die Induktivität im Chip oder Netzteil können wir anhand der Formel berechnen. L: die Leitungslänge zwischen Kondensator und Chip; R: Linienradius; D: Abstand zwischen Stromleitung und Erde. Daher wissen wir, dass zur Verringerung der Induktivität L, L und D reduziert werden müssen, das heißt, der Schleifenbereich, der durch Entkopplung von Kondensator und Chip gebildet wird, reduziert werden sollte, das heißt, Kapazität und Chip sollten so nah wie möglich an der Chipvorrichtung sein.

4., das Design der Stromschleife

Um die Integrität der Stromversorgung zu gewährleisten, Wir wissen, dass ein gutes Stromverteilungsnetz unerlässlich ist. Zunächst einmal, for the Design of the power line and ground wire, we should ensure that the line width is thick (such as 40mil, while the ordinary signal line is 10mil), seinen Impedanzwert so weit wie möglich zu reduzieren. Da Chips immer schneller werden, nach 5/5-Regel, werden wir zunehmend einsetzen Mehrschichtige Platine, die von einer dedizierten Power-Schicht betrieben und von einer dedizierten Schicht umschlossen werden, dadurch die Induktivität der Leitung reduziert.