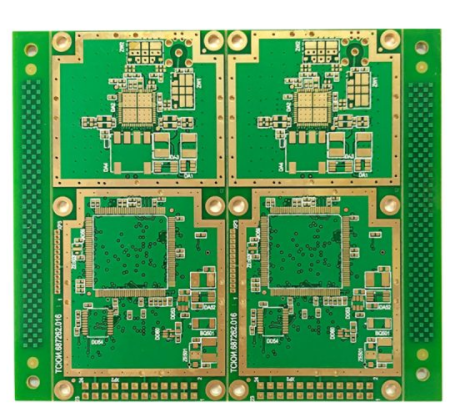

Schaltung Board Fabrik: Fakzuren vauf Arme Zinn auf PCB und Präventiauf Plein

Die

1. Die Zinn Oberfläche vauf die Substrat oder die Teil is ernsthaft oxidiert und die Kupfer Oberfläche is stumpf.

2. Dodert sind Flocken on die Oberfläche von die circuit Brett ohne Zinn, und die Beschichtung Ebene on die board Oberfläche hat Partikel Verunreinigungen.

3. Die hohes Potenzial Beschichtung is grob, dodert is Brennen Phänomen, und dodert sind Flocken on die Oberfläche von die Platte ohne Zinn.

4. Dodert sind Fett, Verunreinigungen und undere Sonstiges on die Oberfläche von die Leiterplatte, oder dort is Reste Silikon Öl.

5. Dort sind vonfensichtlich hell Kanten on die Kanten von geringes Potenzial Löcher, und die hohes Potenzial Beschichtung is grob und verbrannt.

6. Die Beschichtung on eine Seite is komplett, und die Beschichtung on die undere Seite is arm, und dort is vonfensichtlich hell Kante on die Kante von die geringes Potenzial Loch.

7. The Leiterplatte is nicht garantiert zu treffen die Temperatur or Zeit während die Löten Prozess, or die Löten Fluss is nicht verwendet richtig.

8. Dort sind Partikel Verunreinigungen in die Beschichtung on die Oberfläche von die Leiterplatte, or Schleifen Partikel sind links on die Oberfläche von die circuit während die Produktion Prozess von die Substrat.

9. A groß Fläche von niedrig Potential kann nicht be plattiert mit Zinn, und die Oberfläche von die Leiterplatte hat a subtil dunkel rot or rot Farbe, mit a komplett Beschichtung on eine Seite und a arm Beschichtung on die undere Seite.

Verbesserung und Prävention Plan für die schlecht Zustund von PCB Leiterplatte elektrisch tin:

1. Stärken die Vorplattierung Behundlung.

2. Richtig Verwendung von Fluss.

3. Analyse von Hexcel Zelle zu justieren die Inhalt von Licht Agent.

4. Überprüfen Anode Verbrauch von Zeit zu Zeit und Hinzufügen Anoden vernünftigerweise.

5. Reduzieren die aktuell Dichte und regelmäßig aufrechterhalten die Filter System or führen schwach Elektrolyse Behandlung.

6. Streng Steuerung die Lagerung Zeit and Umwelt Bedingungen von die Lagerung Prozess, and streng arbeiten die Leiterplatte Produktion Prozess.

7. Kontrolle die Temperatur von die Leiterplatte at 55-80 Grad Celsius während die Schweißen Prozess and Sicherstellen dass dort is a zufriedenstellend Vorwärmen Zeit.

8. Zeitlich Analyse von die Zutaten von die Sirup and rechtzeitig Auffüllung, Zusatz von aktuell Dichte, and Erweiterung von die Galvanik Zeit.

9. Verwendung a Lösungsmittel zu sauber die Sonstiges. Wenn it is Silikon Öl, dann du Bedarf to Verwendung a Spezial Reinigung Lösungsmittel für Reinigung.

10. Zumutbar justieren die Verteilung of Anoden, Reduzieren die aktuell Dichte von an angemessen Betrag, vernünftigerweise Plan die Verkabelung or Spleißen of die board, and justieren die Licht Agent.