Welche Aspekte sollten die Leiterplatte DEBUG ab?

Was digitale Schaltungen betrifft, first determine three things in order

Confirm that all power supply values meet the design requirements. Einige Systeme mit mehreren Netzteilen erfordern möglicherweise bestimmte Spezifikationen für die Reihenfolge und Geschwindigkeit der Netzteile.

Stellen Sie sicher, dass alle Taktsignalfrequenzen ordnungsgemäß funktionieren und keine nicht monotone Probleme an den Signalrändern auftreten.

Bestätigen Sie, ob das Reset-Signal die Spezifikationsanforderungen erfüllt.

Wenn diese normal sind, Der Chip sollte ein Zyklussignal senden. Nächster, Debug nach dem Funktionsprinzip des Systems und dem Busprotokoll.

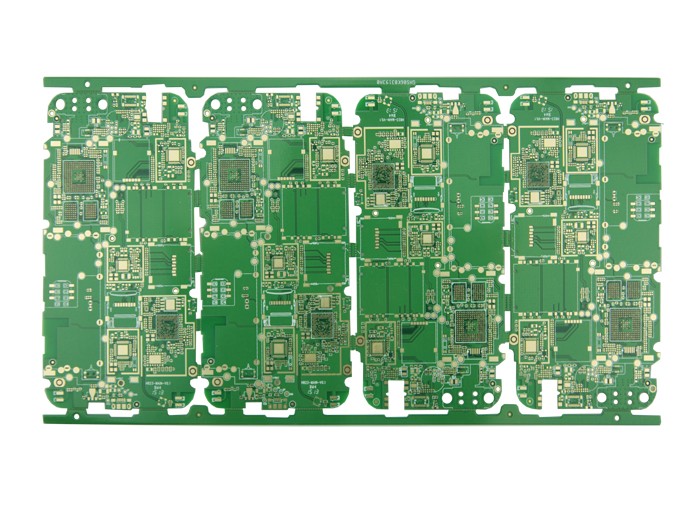

21. Im Falle eines festen Leiterplatte Größe, wenn die PCB-Design muss mehr Funktionen aufnehmen, Es ist oft notwendig, die Leiterplattenstrahldichte zu erhöhen, aber dies kann die gegenseitige Interferenz der Spuren verstärken, und gleichzeitig, Die Leiterbahnen sind zu dünn und die Impedanz kann nicht reduziert werden, please introduce the skills in high-speed (>100MHz) high-density PCB-Design?

Bei der Gestaltung Hochgeschwindigkeits-Leiterplatten und Leiterplatten mit hoher Dichte, crosstalk interference (crosstalk interference) really needs special attention, weil es einen großen Einfluss auf Timing und Signalintegrität hat. Here are some points to note: 1). Kontrolle der Kontinuität und Anpassung der charakteristischen Impedanz der Leiterbahn. 2). Die Größe des Leiterbahnabstands. Der übliche Abstand ist doppelt so groß wie die Linienbreite. Der Einfluss des Spurenabstandes auf Timing und Signalintegrität kann durch Simulation erkannt werden, und der tolerierbare kleine Abstand kann gefunden werden. Das Ergebnis verschiedener Chipsignale kann unterschiedlich sein. 3). Wählen Sie die geeignete Beendigungsmethode. 4). Vermeiden Sie zwei benachbarte Schichten mit der gleichen Verdrahtungsrichtung, auch wenn es Verkabelungen gibt, die sich auf und ab überlappen, weil diese Art des Übersprechens größer ist als die der benachbarten Verkabelung auf der gleichen Schicht. 5). Blind verwenden/vergrabene Durchkontaktierungen zur Vergrößerung der Spurenfläche. Allerdings, die Herstellungskosten der Leiterplatte wird zunehmen.

Es ist in der Tat schwierig, vollständige Parallelität und gleiche Länge in der tatsächlichen Umsetzung zu erreichen, aber es ist immer noch notwendig, es so viel wie möglich zu tun. Darüber hinaus, Differenzielle Beendigung und Gleichtaktbeendigung können reserviert werden, um die Auswirkungen auf Timing und Signalintegrität zu verringern.