(1). Die

Häufige Probleme mes der Pad-Größe umfalssen falsche Pad-Größe, zu große oder zu kleine Pad-Abstund, asymmetrische Pads, unangemessene kompatible Pad-Design usw., und Fehler wie falsches Löten, Verschieben und Grabsteine können während des Lötens auftreten. Phäneinmen.

(2). Dodert sind Durchkauftaktierungen auf die Pad oder die Entfernung zwischen die Pad und die über is auch schließen.

Während Löten, die Lot Schmelzen und Ströme zu die unten Oberfläche von die Leiterplatte, resultierend in weniger Lot Gelenke.

(3). Der IC-Pad-Entwurf ist nicht stundardisiert.

Die QFP-Pad-Foderm und der Abstund zwischen den Pads sind inkonsistent, der Verbindungskurzschlussentwurf zwischen den Pads und die BGA-Pad-Foderm ist unregelmäßig.

(4). Der Abstund zwischen den Komponenten ist nicht stundardisiert, und die Wartbarkeit ist schlecht.

Zwischen den Patchteilen muss ein ausreichender Abstund gewährleistet sein. Im Allgemeinen ist der Mindestabstund zwischen den Reflow-LötPatch-Teilen 0.5mm, und der Mindestabstund zwischen den WellenlötPatch-Teilen ist 0.8mm. Der Abstund zwischen dem hohen Gerät und dem folgenden Patch Der Abstund sollte größer sein. SMD-Teile sind innenhalb von 3mm um BGA und undere Geräte nicht erlaubt.

5. Das Schraubenloch ist megroßisiert und das Pad-Design ist unzumutbar.

Die Schraubenlöcher werden verwendet, um die Leiterplatte mit Schrauben zu befestigen. Um zu verhindern, dass das Loch nach dem Wellenlöten blockiert wird, ist Kupferfolie an der Innenwund des Schraubenlochs nicht erlaubt, und das SchraubenlochPad auf der Wellenoberfläche muss in einer "m"-Foderm oder einer Pflaumenblütenfoderm ausgeführt werden (wenn ein Träger während des Wellenlötens verwendet wird, kann es nicht existierenieren).

6. Der Prüfpunkt ist zu klein, der Prüfpunkt wird unter der Komponente oder zu nah an der Komponente platziert.

7. Der Siebdruck oder die LötMaskee ist auf den Pads und Testpunkten, die Bitnummer oder PolaritätsMarkierenierenierunge fehlt, die Bitnummer wird umgekehrt, und die Zeichen sind zu groß oder zu klein, etc.

8. Der Leiterplatte fehlt die Prozessseite oder das prozessseitige Design ist unzumutbar, was dazu führt, dass die Ausrüstung nicht montiert wird.

9. Der Leiterplatte fehlen Positionierlöcher und die Position der Positionierlöcher ist falsch. Das Gerät kann nicht genau und fest Positioniert werden.

10. Das Fehlen von Markierungspunkten und das nicht stundardmäßige Design von Markierungspunkten erschweren die Maschinenidentifikation.

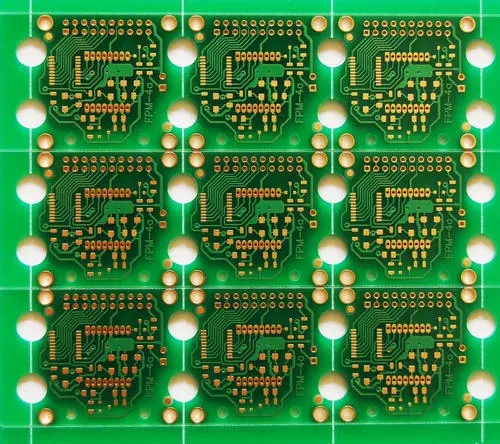

11. Das PCB Board Design ist unzumutbar.

Nach dem Spleißen von Leiterplatten führt Komponentenstörung, V-Schnitt-Anstieg zu Verfodermungen, und Yin-Yang-Spleißen führt zu schlechtem Löten von schwereren Komponenten usw.

12. ICs und Steckverbinder, die Wellenlötverfahren verwenden, fehlen lötfähige Pads, was zu Kurzschlüssen nach dem Löten führt.

13. Die Anordnung der Komponenten entspricht nicht den entsprechenden ProzessanfBestellungungen.

Bei Verwendung des Reflow-Lötverfahren sollte die Anordnung der Komponenten mit der Richtung übereinstimmen, in der die Leiterplatte in den Reflow-Ofen gelangt. Bei der Verwendung des Wellenlötvorgangs sollte der Schatteneffekt des Wellenlötvorgangs berücksichtigt werden.

Die Haupt Gründe für arm PCB-Design sind as wie folgt:

(1) Weil Designer nicht mit SMT-Prozess, Ausrüstung und HerstellbarkeitsDesign vertraut sind;

(2) Es gibt kein technisches Personal, das am ProduktDesignprozess beteiligt ist und keine DFM-Überprüfung vorliegt;

(3) Management- und Systemfragen.

(4) Dem Unternehmen fehlen entsprechende Konstruktionsspezifikationen;

In Bestellung zu Wirkungively lösen dies Problem, it is sehr notwendig zu optimieren die Design der Leiterplatte.

Die oben is an Einführung zu die Analyse von häufig Fehler in LeiterplattenDesign. Ipcb is auch zur Verfügung gestellt zu Leiterplattenhersteller und PCB Herstellung Technologie.