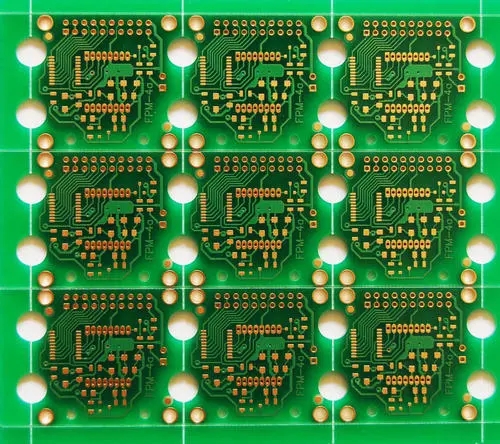

Precautions for via design in PCB

1. Berücksichtigung der Kosten und Signalqualität, Wählen Sie eine angemessene Größe über Größe. Zum Beispiel, für das 6-10 Layer Memory Modul PCB-Design, es ist besser, 10 zu verwenden/20Mil (drilled/pad) vias. Für einige kleine Platten mit hoher Dichte, Sie können auch versuchen, 8 zu verwenden/18Mil. Loch. Unter aktuellen technischen Bedingungen, Es ist schwierig, kleinere Vias zu verwenden. Für Strom- oder Masseverbindungen, Sie können eine größere Größe zur Reduzierung der Impedanz in Betracht ziehen.

2. Die beiden oben besprochenen Formeln können geschlossen werden, dass die Verwendung einer dünneren Leiterplatte vorteilhaft ist, um die beiden parasitären Parameter von Vias zu reduzieren.

3. Versuchen Sie nicht, die Schichten der Signalspuren auf dem Leiterplatte, das heißt,, Versuchen Sie, keine unnötigen Vias zu verwenden.

4. Die Power- und Massepunkte sollten in der Nähe gebohrt werden, und die Leitung zwischen dem Durchgang und dem Stift sollte so kurz wie möglich sein, weil sie die Induktivität erhöhen. Zur gleichen Zeit, Die Strom- und Masseleitungen sollten so dick wie möglich sein, um die Impedanz zu reduzieren.

5. Platzieren Sie einige geerdete Durchkontaktierungen in der Nähe der Durchkontaktierungen der Signalschicht, um die nächste Schleife für das Signal bereitzustellen. Es ist sogar möglich, eine große Anzahl redundanter Masseverbindungen auf dem Leiterplatte. Natürlich, das Design muss flexibel sein. Das zuvor besprochene Via-Modell ist der Fall, wenn es Pads auf jeder Schicht gibt. Manchmal, Wir können die Pads einiger Schichten reduzieren oder sogar entfernen. Besonders wenn die Dichte der Durchkontaktierungen sehr hoch ist, Es kann zur Bildung einer Bruchnut führen, die die Schleife in der Kupferschicht trennt. Um dieses Problem zu lösen, zusätzlich zur Verschiebung der Position des Via, Wir können auch erwägen, das Via auf der Kupferschicht zu platzieren. Verringerte Padgröße

PCB-Design output knowledge

The PCB-Design kann auf einen Drucker oder eine Gerber-Datei exportiert werden. Der Drucker kann die Leiterplatte in Schichten drucken, was für Designer und Prüfer bequem zu überprüfen ist; Die Gerber-Datei wird dem Plattenhersteller zur Herstellung der Leiterplatte übergeben. Die Ausgabe der gerber Datei ist sehr wichtig. Es hängt mit dem Erfolg oder Misserfolg dieses Entwurfs zusammen. Im Folgenden wird auf die Dinge eingegangen, die bei der Ausgabe der Gerber-Datei beachtet werden müssen.

a. The layers that need to be output are wiring layers (including top layer, untere Ebene, middle wiring layer), power layer (including VCC layer and GND layer), silk screen layer (including top silk screen, bottom silk screen), solder mask layer (including top solder mask) And bottom layer solder mask), and also generate a drilling file (NC Drill)

b. Wenn die Power-Ebene auf Split gesetzt ist/Gemischte, Wählen Sie dann Routing im Dokument-Element des Fensters Dokument hinzufügen aus, und jedes Mal, wenn die Gerber-Datei ausgegeben wird, Sie müssen Pour Manager Plane Connect für Kupferguss auf dem PCB-Diagramm verwenden; wenn es auf CAM Plane gesetzt ist, Ebene auswählen. Beim Setzen des Ebenenelements, Layer25 hinzufügen, and select Pads and Vias in Layer25

c. In the device setup window (press Device Setup), change the value of Aperture to 199

d. Beim Festlegen der Ebene jeder Ebene, select the Board Outline

e. Beim Einstellen der Ebene der Siebdruckschicht, keine Teileart auswählen, select the top layer (bottom layer) and Outline, Text, Line of the silk screen layer

f. Beim Einstellen der Schicht der Lotmaskenschicht, Durchkontaktierungen auswählen, um anzuzeigen, dass keine Lötmaske zu den Durchkontaktierungen hinzugefügt wird, und nicht zu wählen Durchkontaktierungen, um Lötmasken anzuzeigen, je nach Situation.

g. Beim Generieren von Bohrdateien, use the default settings of PowerPCB and do not make any changes

h. Nachdem alle Gerbera-Dateien ausgegeben wurden, Öffnen und drucken Sie sie mit CAM350, und überprüfen Sie sie durch den Designer und Prüfer nach dem "PCB-Checkliste"