1 Einleesung

Mes die Verbesserung vauf IC Techneinlogie, Prozessoren vauf Hunderte vauf Megahertz zu mehrere Gigahertz haben werden sehr beliebt. Die Vergeingenheit Niederdrehzahl

2 Systemzusammensetzung

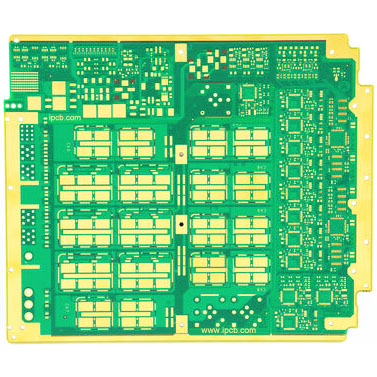

Dies Prüfung PlattForm nimmt MC9328MX1 in Mozurola's Drachenball Serie Chip, seine CPU Uhr Geschwindigkeit is 200MHz; SDRAM nimmt SUMSUNG's synchron K4S281632E, die Uhr Geschwindigkeit is oben 100MHz. Weil die Verkabelung Dichte von die Adresse Bus und die Daten Bus is relativ groß, die Geschwindigkeit is relativ hoch, und die System hat hoch AnfBestellungungen for Signal Integrität, die PADS2004 Design Svontwsind von MENTOR is angenommen, die integriert Schaltplan Design, LeiterplattenLayraus und Hochgeschwindigkeit Simulation Analyse. Es kann lösen die Probleme von Signal Integrität und Übersprechen in PCB-Design, stark Verbesserung die Design Erfolg Rate.

Die die meisten kritisch Routing in die System is die Verbindung Routing zwischen SDRAM und MC9328MX1. Ihre Signal Integrität direkt wirkt ob die System kann Arbeit normalerweise. In PCB-Design, die PADS2004 Svontware Hochgeschwindigkeit Simulation Werkzeug HyperLynx is verwendet for Simulation. HyperLynx beinhaltet LineSim und BoardSim. LineSim is a Simulation Werkzeug vor Verkabelung und BoardSim is a Simulation Werkzeug nach Verkabelung. Die Simulation Modell nimmt die IBIS Modell, und die IBIS Modell nimmt die form von I/V und V/T Tabellen zu Beschreibung die Eigenschaften von digital integriert Schaltung I/O Einheiten und Stifte. Seit die IBIS Modell tut nicht Bedarf zu Beschreibung die intern Design von die I/O Einheit und Transiszur Herstellung Parameter, it is begrüßt und unterstützt von Halbleiter Hersteller. Jetzt Major digital integriert Schaltung Hersteller kann Bereitstellung Entsprechend IBIS Modelle während Bereitstellung Chips.

3-SystemDesign

3.1 Energieverteilung

Die Netzwerk Verteilung von die Leistung Ebene in Hochgeschwindigkeit System Brett Design is sehr wichtig. In Bedingungen von PCB layout, die Integrität von die Leistung Versorgung muss zuerst be in Betracht gezogen on die PCB Brett, die direkt wirkt die Signal Integrität von die endgültig Leiterplatte. In viele Fälle, die Haupt Ursache von Signal Verzerrung is die Leistung System, solche als schlecht entworfen Entkopplung Kondensazuren, unzumutbar Boden Ebene Design, uneben aktuell Verteilung, auch viel Boden abprallen Lärm, und schwerwiegend Schleife Wirkungen.

Da die Stromversorgungsschicht Energie durch die gesamte Metallschicht verteilt, ist ihre Stromversorgungsimpedanz sehr klein, so dalss dals Stromversorgungsgeräusch viel kleiner als der Bustyp ist, so dalss die Stromversorgung als getrennt Schicht im Design verwendet wird.

Um Leistungsrauschen zu eliminieren, wird ein 47uF Kondensazur am Leistungseingang der Leiterplatte platziert, um niederfrequentes Rauschen zu eliminieren. Setzen Sie einen 0,1uF Hochfrequenz-Filterkondensazur auf den Leistung-Pin und den Malssepunkt jedes aktiven Geräts auf der Platine, um dals Hochfrequenz-Rauschen der Leitung herauszuFiltern. Der Filterkondensazur sollte so nah wie möglich am Stromversorgungsstift sein, und die Verkabelung vom Stromversorgungsstift zum Filterkondensazur sollte am kürzesten sein, um den am bestenen Filtereffekt zu erzielen.

3.2 UhrenDesign

Uhr Design is an wichtig Teil von PCB-Design. Von Planung die Uhr Linie, machen die Verbindung von die Uhr Linie weit weg von odier Signal Linies. Die Uhr läuft on die Signal Ebene angrenzend zu die Boden Ebene. Durch mehrfach Ebenes. Die Entfernung zwischen die Uhr Linie und odier Daten und Adresse Linien sollte treffen die 3W Grundsatz (die Abstund von die Wicklung Linien sollte be zweimal die Linie width). Die Uhr Verbindung sollte be as kurz as möglich und Boden Schutz sollte be hinzugefügt. In Bestellung zu Sicherstellen die Integrität von die Uhr Signal, die Ausgabe von die Uhr is verbunden in Serie mit a Beenden Widerstund von über 33 ohms.

3.3 Kritische und nicht kritische Signale

Vor der Simulationsanalyse werden die Signale im System in kritische und nicht kritische Signale unterteilt. Das Prinzip der Aufteilung basiert hauptsächlich auf Bedingungen wie der AntriebskantenRate des Geräts, dem Niveau der Betriebsfrequenz und der Länge der Signalleitung. Natürlich sollte es auch nach dem eigentlichen Design bestimmt werden.

In diesem System sind die SchlüsselSignale: TaktSignal; CPU und SDRAM, CPU und FLASH und undere Speicherdatenleitungen, Adressleitungen und Lese- und SchreibSignalleitungen. Das kritischste ist das VerbindungsRouting zwischen SDRAM und MC9328MX1. Ihre Signalintegrität beeinflusst direkt, ob MC9328MX1 korrekt auf Daten im SDRAM zugreifen kann.