Das Design des LVDS Signals auf der Leiterplatte ist nicht nur ein Differenzsignal, aber auch ein digitales Hochgeschwindigkeitssignal. Daher, unabhängig davon, ob das LVDS-Übertragungsmedium Leiterplatte Drähte oder Kabel, Maßnahmen müssen getroffen werden, um eine Reflexion des Signals am Medienterminal zu verhindern, und elektromagnetische Störungen sollten reduziert werden, um die Signalintegrität zu gewährleisten. Solange wir diese Elemente bei der Verdrahtung berücksichtigen, Das Design von High-Speed Differential-Leiterplatten ist nicht sehr schwierig. Im Folgenden werden kurz die Designpunkte des LVDS-Signals auf der Leiterplatte: 2.1 Layout in eine mehrschichtige Platine Leiterplatten mit LVDS-Signalen werden im Allgemeinen als mehrschichtige Platine ausgelegt. Da das LVDS-Signal ein Hochgeschwindigkeitssignal ist, Die benachbarte Schicht sollte eine Masseschicht sein, um das LVDS-Signal abzuschirmen, um Interferenzen zu vermeiden. Für Platten mit geringer Dichte, wenn die räumlichen Gegebenheiten es zulassen, LVDS-Signale und andere Signale auf verschiedenen Ebenen platzieren. Zum Beispiel, in einer vierlagigen Platte, Die Schichten können in der Regel wie folgt ausgelegt werden: LVDS Signalschicht, Untergrund, Leistungsebene, und andere Signalschichten. 2.2 LVDS Signalimpedanz Berechnung und Steuerung. Die Spannungsschwankung des LVDS Signals beträgt nur 350mV, das für den stromgetriebenen Differenzsignalbetrieb geeignet ist. Um sicherzustellen, dass das Signal nicht durch das reflektierte Signal beeinflusst wird, wenn es sich in der Übertragungsleitung ausbreitet, Das LVDS-Signal erfordert die Steuerung der Impedanz der Übertragungsleitung, und die Differenzimpedanz ist normalerweise 100 ++/- 10Ω. Die Qualität der Impedanzsteuerung beeinflusst direkt die Signalintegrität und Verzögerung.

1. Wie man seine Leiterplatte Impedanz?

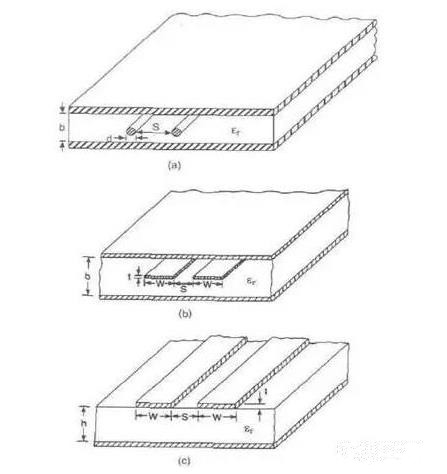

1.1 Bestimmen Sie den Verdrahtungsmodus, Parameter und Impedanzberechnung. LVDS wird in den äußeren Mikrostreifenliniendifferenzialmodus und den inneren Schichtstreifenliniendifferenzialmodus unterteilt. Impedanz kann berechnet werden, indem man die Parameter vernünftig einstellt und entsprechende Software verwendet. Durch Berechnung, Der Impedanzwert ist direkt proportional zur Dicke der Isolierschicht, und umgekehrt proportional zur dielektrischen Konstante, Dicke und Breite des Drahtes.

1.2 Folgen Sie dem Prinzip der parallelen äquidistanten Linien und der engen Kupplung. Nach der Bestimmung der Linienbreite und -abstände, Beachten Sie beim Routing strikt die berechnete Linienbreite und -abstände, und der Abstand zwischen den beiden Zeilen muss immer konstant gehalten werden, das ist, they must be parallel (you can place the picture). Zur gleichen Zeit, Bei der Berechnung der Linienbreite und -abstände wird das Prinzip der engen Kopplung beachtet, das ist, Der Zeilenabstand des Differenzpaares ist kleiner oder gleich der Linienbreite. Wenn die beiden Differenzsignalleitungen sehr nah sind, die aktuelle Übertragungsrichtung ist entgegengesetzt, die Magnetfelder brechen sich gegenseitig auf, die elektrischen Felder sind miteinander gekoppelt, und die elektromagnetische Strahlung ist viel kleiner. Auch, Die beiden Drähte müssen auf der gleichen Schicht sein, um eine mehrschichtige Verkabelung zu vermeiden. Denn bei der eigentlichen Verarbeitung der Leiterplatte, Der Grad der Laminierung zwischen den Stapeln ist viel niedriger als die Ätzgenauigkeit der gleichen Schicht, und der dielektrische Verlust während des Laminierungsprozesses kann nicht garantieren, dass der Abstand zwischen den Differenzlinien gleich der Dicke des Zwischenschichtdielektrikums ist, Die Differenzimpedanzänderung des Differenzpaares zwischen Schichten.

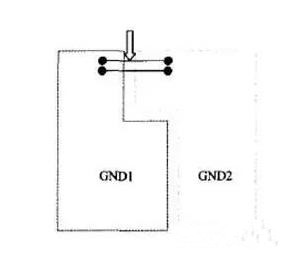

1.3 Kurz und gerade gehen. Um die Qualität des Signals zu gewährleisten, Die LVDS Differentialpaarspur sollte so kurz und gerade wie möglich sein, Verringern Sie die Anzahl der Durchkontaktierungen in der Verdrahtung, und vermeiden Sie zu lange Differentialpaarverdrahtung und zu viele Umdrehungen. Versuchen Sie 45° oder Bögen an den Ecken zu verwenden. 90° Drehungen vermeiden. Es gibt keine Beschränkung bei der Auswahl von LVDS-Paarrouting-Methoden zwischen verschiedenen differentiellen Linienpaaren. Microstrip Linie und Streifen Linie können verwendet werden, aber es muss beachtet werden, dass es eine gute Bezugsebene gibt. Der Abstand zwischen verschiedenen Differenzlinien sollte nicht zu klein sein, und sollte mindestens 3-5-mal der Abstand zwischen Differenzlinien sein. Falls nötig, Erdlochisolierung zwischen verschiedenen differentiellen Linienpaaren hinzufügen, um gegenseitiges Übersprechen zu verhindern. Halten Sie LVDS-Signale so weit wie möglich von anderen Signalen fern. LVDS Differenzsignale können nicht auf Ebenen aufgeteilt werden. Obwohl die beiden Differenzsignale Rückwege für einander sind, die Quersegmentierung wird die Rückkehr des Signals nicht unterbrechen, but the transmission line across the segmentation will cause discontinuity in impedance due to the lack of a reference plane (as shown in the figure, where GND1 and GND2 are adjacent to LVDS Ground plane). Der Abstand zwischen dem passenden Widerstand des Empfangsenden und dem Empfangsstift sollte so nah wie möglich sein. Zur gleichen Zeit, die Genauigkeit des Übereinstimmungswiderstandes muss kontrolliert werden. Für Punkt-zu-Punkt-Topologie, Die Impedanz der Leiterbahn wird normalerweise bei 100Ωgesteuert, aber der passende Widerstand kann entsprechend der tatsächlichen Situation eingestellt werden. Der Widerstandsgrad beträgt 1%-2%. Denn nach Erfahrung, 10% Impedanzanpassung erzeugt 5% Reflexion.

2. Simulation analysis of serial LVDS signal

The above analyzes the matters that must be paid attention to when Designing LVDS signals. Obwohl die oben genannten Regeln im Allgemeinen während des PCB-Designs befolgt werden, um die Richtigkeit und Genauigkeit des Entwurfs zu verbessern, Die komplette Signalsimulation der Leiterplatte muss durch Simulation durchgeführt werden. Übersprechen des Signals, Verzögerung, Reflexions- und Augenmuster-Wellenformen, um das Ziel des richtigen Designs zu erreichen. Der Simulationsprozess des Signalintegritätsproblems besteht darin, zuerst das Simulationsmodell der Komponenten zu etablieren, und führen Sie dann die Vorsimulation durch, um die Parameter und Einschränkungen des Verdrahtungsprozesses zu bestimmen. Die physische Realisierungsstufe wird entsprechend den Einschränkungen entworfen, und die Nachsimulation wird durchgeführt, um zu überprüfen, ob der Entwurf die Konstruktionsanforderungen erfüllt. Die Art des Modells im gesamten Prozess beeinflusst direkt die Ergebnisse der Simulation, Auch die in der Vor- und Nachsimulationsstufe verwendeten Simulationsanalysemethoden sind entscheidend für die Simulationsergebnisse, und ein höherer Grad des Gewürzmodells wird in diesem Design verwendet. Im Folgenden finden Sie eine Kombination von aktuellen Projekten, um den Implementierungsprozess der Simulation in diesem Entwurf zu veranschaulichen..

2.1 Leiterplatte stack setting

From the above analysis, Es ist bekannt, dass die Stapeleinstellung der Leiterplatte ist eng mit der Kopplung des Signals und der Impedanzberechnung verbunden. Daher, Der Stapelentwurf muss vor dem Leiterplatte design, und dann die Impedanzberechnung des Signals.

2.2 Set DC voltage value

This step is mainly to specify the DC voltage value for certain specific networks (usually power ground, etc.), Bestimmung der Gleichspannung, die an das Netz angelegt werden soll, Für die Durchführung der EMI-Simulation ist die Bestimmung eines oder mehrerer Spannungsquellenpins erforderlich. Die Referenzspannungsinformation, die das Modell im Simulationsprozess verwendet, wird beschrieben..

2.3 Device settings

During allegro simulation, allegro unterteilt die Geräte in drei Kategorien: IC, connectors and discrete devices (resistance capacitors, etc.), allegro weist den Pins des Geräts Simulationsattribute entsprechend dem Gerätetyp zu, Diskrete Geräte und Steckerpins Das Attribut ist UPSPEC, und das Pin-Attribut des IC kann IN sein, AUS, BI, etc.

2.4 Model allocation

The main models used in the board-level high-speed Leiterplatte Simulationsprozess sind Gerätemodelle und Übertragungsleitungsmodelle. Das Gerätemodell wird in der Regel vom Gerätehersteller bereitgestellt. Im seriellen Hochgeschwindigkeitssignal, Was wir annehmen, ist das SPICE-Modell mit höherer Präzision, um die Simulationsanalyse durchzuführen. Das Übertragungsleitungsmodell wird durch Simulationssoftware-Modellierung gebildet. Wenn das Signal übertragen wird, Die Übertragungsleitung macht das Problem der Signalintegrität prominent, So beeinflusst die Fähigkeit der Simulationssoftware, die Übertragungsleitung zu modellieren, direkt das Simulationsergebnis.

2.5 SI inspection

The SI Audit function is used to check whether a particular network or a group of networks can be extracted for analysis. Allgemein, Es ist, das Hochgeschwindigkeitsnetz zu setzen, auf das wir achten müssen. Dieses Design konzentriert sich hauptsächlich auf serielle LVDS-Signale.

2.6 Extract network topology

Extract the topological structure of the signal of interest from the Leiterplatte, allgemein einschließlich des Antriebs- und des Empfangs-Endes, sowie die Übertragungsleitung und zugehörige passende Widerstände und Kondensatoren. Aus der Topologie kann man sehen, dass das Netzwerk diese Pfade durchläuft, was die Signalübertragung verursacht Einfluss. This article only takes the network topology diagram of one of the signals as an example: as shown in Figure 4:

2.7 View waveform

After the above related steps are set up, die Simulation kann durchgeführt werden. Allegro kann Signalreflexionssimulation und Übersprechersimulation durchführen, und die Differenziallinie muss auch Augendiagrammanalyse durchführen. Natürlich, Die Simulation wird auch in Vor- und Nachsimulation unterteilt. Wenn allegro verwendet wird, um die Leiterplatte, Es ist notwendig, das Design in Echtzeit mit den Simulationsergebnissen zu modifizieren, um die Anforderungen zu erfüllen. Weil der Simulationsprozess kompliziert ist und die Schritte umständlich sind, Ich würde sie nicht nacheinander beschreiben. Bei der Verdrahtung des Differenzialpaares gibt es zwei Punkte zu beachten. Die eine ist, dass die Länge der beiden Linien so lang wie möglich sein sollte, und die gleiche Länge soll sicherstellen, dass die beiden Differenzsignale immer gegenüberliegend gehalten werden. Polarität zur Reduzierung von Gleichtaktkomponenten. The other is that the distance between the two lines (this distance is determined by the differential impedance) must always be kept constant, das ist, es muss parallel gehalten werden. Es gibt zwei parallele Wege, Eins ist, dass die beiden Drähte auf derselben Seite laufen, and the other is that the two wires run on two adjacent layers above and below (over-under). Allgemein, Ersteres hat mehr Side-by-Side Implementierungen. Die Equidistance soll hauptsächlich die gleiche Differenzimpedanz zwischen den beiden gewährleisten und Reflexion reduzieren. Die Verdrahtungsmethode des Differenzialpaares sollte eng und parallel angemessen sein. Die sogenannte angemessene Nähe liegt daran, dass dieser Abstand den Wert der Differenzimpedanz beeinflusst, ein wichtiger Parameter für die Gestaltung von Differentialpaaren. Die Notwendigkeit der Parallelität besteht auch darin, die Konsistenz der Differenzimpedanz aufrechtzuerhalten. Wenn die beiden Linien plötzlich weit und nah sind, die Differenzimpedanz wird inkonsistent sein, die Signalintegrität und Zeitverzögerung beeinflussen. Aus dem simulierten S-Parameter Graph, Die Differenzimpedanz des Differenzpaares und die Signalintegrität können analysiert werden. Die Signalsimulationswellenformen in diesem Design sind unten zur Erläuterung angegeben.. Aus der Simulationslegende Abbildung 5 ist ersichtlich, dass der Degradationsindex von S11 im Frequenzbereich von 0-3.0GHz ist: unter -16.770db, and S22 (pink curve) is not worse than -17db. Dies zeigt, dass die Differenzimpedanz des Differenzpaares nahe am Bemessungsindex liegt, und die Signalintegrität ist garantiert.

3. Conclusion

Through the above simulation analysis, Es kann bekannt sein, dass die verschiedenen Anforderungen an Hochgeschwindigkeits-LVDS-Signale in der Entwurfsphase des Leiterplatte, und die tatsächliche Leiterplatte Die Produktion hat auch die Richtigkeit des Designs bewiesen. Das Produkt läuft stabil und erfüllt vollständig die PCI-Express Anforderungen an Hochgeschwindigkeits-Datenübertragung und hohe Zuverlässigkeit. Aus der Analyse in diesem Artikel, Es zeigt sich, dass bei der Gestaltung von seriellen Hochgeschwindigkeitssignalen, nicht nur das Schaltungsdesign wird berücksichtigt, Ebenso wichtig sind der Entwurf von Leiterplattendiagrammen und die Simulationsanalyse, und wenn die Frequenz des Signals größer und größer wird, die Verzögerung und Übersprechen des Signals werden beeinträchtigt. Faktoren wie Signalintegrität und Signalintegrität werden immer komplexer. Zur gleichen Zeit, Es wird immer schwieriger, den Einfluss dieser Faktoren zu kontrollieren. Ingenieure müssen das Verdrahtungsdesign gründlich analysieren, die verwendeten Modelle, effektive Simulations- und wissenschaftliche Analysemethoden, in order to provide the correct guidance for the complex high-speed Leiterplatte design and reduce the correction cycle to ensure The design is successful.