Ein weiterer Spezialfall des gemeinsamen Uhrensystems ist die interne Synchrontaktsystem. Viele unerfahrene Ingenieure werden die internen Synchrontaktsystem als Quelle synchrones Timing, und führen Sie gleiche Längensteuerung entsprechend der Quelle synchrone Timing, resultierend in Timing Design Fehlern.

Lassen Sie uns zunächst überprüfen, wie Sie feststellen können, ob ein System eine gemeinsame Uhr ist. Im vorherigen Blogbeitrag wurde erwähnt, dass die Suche nach einem Uhrenbaum und die Bestimmung der Beziehung zwischen Taktsignalen der Schlüssel zur Beurteilung verschiedener Timing-Systeme ist. Common Clock System hat im Allgemeinen einen externen Kristall oder Kristall, der mit dem treibenden Ende und dem empfangenden Ende des Systems durch einen Uhrenverteiler verbunden ist (oder FPGA kann direkt verschiedene Uhren an das treibende Ende und das empfangende Ende ausgeben) und die externe Taktleitung Zur Steuerung des Timings des Systems wird es ein gemeinsames Uhrensystem genannt.

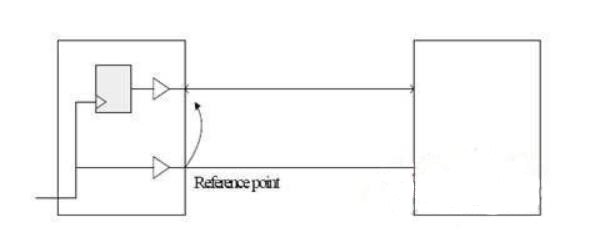

Das Taktsignal der interne Synchronisationszeit wird direkt vom Antriebsende zum Empfangsende gesendet. Im vorherigen Blogbeitrag wurde erwähnt, dass der Zeitabstand des gemeinsamen Uhrensystems klein ist, und einer der Schlüsselfaktoren, die die Frequenz nicht weiter erhöhen können, ist Tco. Aufgrund von Faktoren wie Prozess, Es ist schwierig, diesen Tco zu klein zu machen. Zum Beispiel, der Tco max von SDRAM ist allgemein. Es gibt fünf.4ns. Die interne Synchrontaktsystem ersetzt den externen Takttreiber durch einen internen Puffer, so dass der Puffer auf dem Taktsignal und der Puffer auf dem Datensignal aufeinander abgestimmt werden können, um einander aufzubrechen, So kann der Bereich zwischen den Maximal- und Minimalwerten des Gerätes reduziert und erhöht werden Timing Marge macht das Timing leicht zu erfüllen.

Das interne Synchronisations-Taktsystem ist leicht mit der Quellsynchronisation zu verwechseln. Tatsächlich ist es einfach, es zu unterscheiden, indem man ein Prinzip ergreift. Der Quellsynchronisationszeitpunkt existiert im Allgemeinen in der Systemuhr und dem Strobosignal der Datengruppe, wie z.B. die Beziehung zwischen DQ und DQS und CLK. Die interne synchrone Uhr hat nur ein Taktsignal, das vom treibenden Ende und dem empfangenden Ende geteilt wird (in Mobile SDRAM ist der Signalname SDCK)

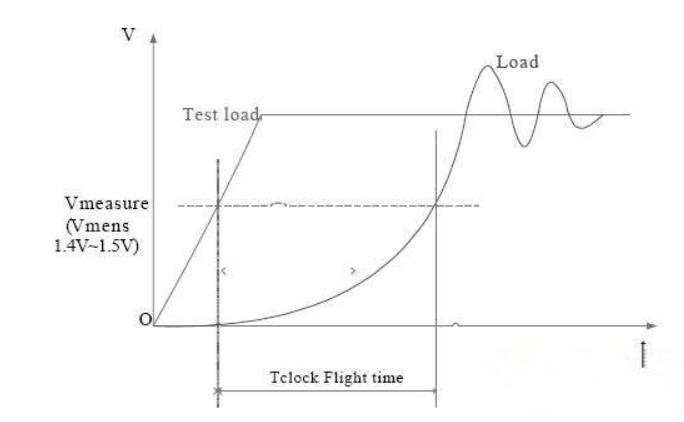

Daher ist die interne Synchronisationszeit in der Berechnung ähnlich wie die gemeinsame Uhr, außer dass es eine weitere Variable in der Ungleichheit gibt, die TCLK_FT: Flugzeit der Uhr ist. Abbildung 2 zeigt die Messmethode von TCLK_FT.

Die Zeitberechnungsformel der internen Synchronisierungsuhr lautet: (wenn die Ausbreitungsrichtung der Uhr und die Daten gleich sind, ist es die positive Richtung)

Tco(max)+Tflight(max)+Tsetup-Tclk_ft+Tjitter+Tmargin Tco(min)+Tflight(min)-Tclk_ft-Tmargin>Thold Auf diese Weise kann die Uhr durch Einstellen von Tclk_ft in der besten Position sein. Diese Methode kann auch verwendet werden, um das Timing im externen Synchronisationsmodus anzupassen. Die spezifische Einstellmethode wurde im vorherigen Fall eingeführt, Sie können darauf verweisen. Zusammenfassung: Aus externer Sicht sind interne Synchronisation und Quellsynchronisation gleich, aber die interne Struktur der beiden ist unterschiedlich. Die Quellsynchronisationsmethode besteht darin, ein Register vor dem Puffer des Taktsignals in der internen Synchronisationsstruktur hinzuzufügen, und die Taktverarbeitung und Datenverarbeitung innerhalb des Chips sind gleich. Auf diese Weise kann sich die Uhr mit der Geschwindigkeit der Daten ändern und befindet sich immer in der Mitte der Daten. Die Essenz der internen Synchronisierungsuhr ist immer noch das gemeinsame Uhrensystem. Die Zeitberechnung ist das gleiche wie das gemeinsame Taktsystem der externen Uhr, außer dass Tclk_ft an beiden Enden des Berechnungsergebnisses addiert oder subtrahiert wird. Die Zeitbeschränkungsbeziehung ist auch der Weg der maximalen und minimalen Gesamtlänge, nicht der Weg der gleichen Länge. Die interne synchrone Uhr erhöht die Mittel der Timing Margin Anpassung, und da sie den Einfluss von Tco ausgleicht, ist das Timing leichter zu erfüllen. Die Zeitberechnungsmethode ist jedoch komplizierter und erfordert, dass der Konstrukteur sie versteht.