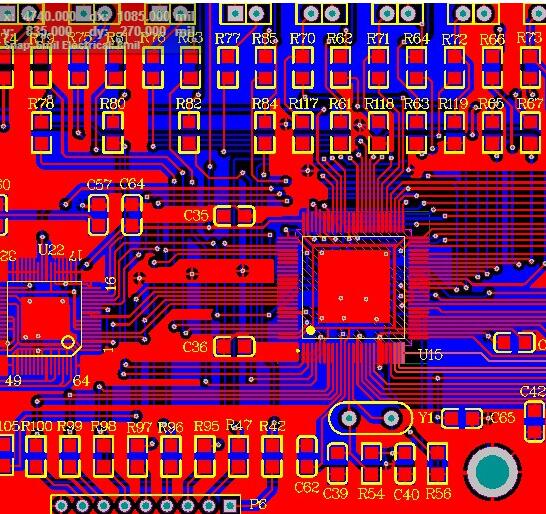

Wie man die Schweißhohlräume und Defekte verschiedener IC-Chips auf PCBA-Leiterplatten

Nach dem Löten der Hardware PCBEin elektronisches Produkt wird in den bleifreien Prozess eingeführt, aufgrund der Eigenschaften von bleifreiem Lot, wie hoher Schmelzpunkt, schlechte Benetzbarkeit, schmales Prozessfenster, etc., Der Lötprozess weist einzigartige Defekte und Defekte des bleifreien Lötens auf, wie Zinnperlen und Lötstellen. Rauheit, fehlendes Lot, kleine Dose, und Hohlräume.

Es ist bekannt, dass beim Löten großer flacher und niederfußhoher Bauteile Hohlräume entstehen, wie QFN-Komponenten. Der Einsatz dieser Art von Komponenten nimmt zu. Um die IPC-Standards zu erfüllen, die Bildung von Hohlräumen macht viele Leiterplatte Designer, PCBEine lötende EMS-Gießerei und das Qualitätskontrollpersonal haben Kopfschmerzen.

Die Parameter zur Optimierung der Void-Leistung sind in der Regel die chemische Zusammensetzung der Lotpaste, das Reflow Temperaturprofil, Beschichtung von Substrat und Bauteilen, und die optimale Gestaltung des Pads und der SMT Schablonenvorlage. Allerdings, in der Praxis, Die Änderung dieser Parameter hat offensichtliche Einschränkungen. Trotz großer Anstrengungen zur Optimierung, aber immer noch zu hohe Void Rate.

Die Hauptursache für Lötlöcher ist, dass die Luft oder das flüchtige Gas, das in die Lötpaste eingewickelt ist, nach dem Schmelzen der Lötpaste nicht vollständig entladen wird.. Zu den Einflussfaktoren gehören Lotpastenmaterial, Druckform der Lötpaste, Druckvolumen der Lötpaste, Reflow-Temperatur, Reflow-Zeit, Lötgröße, Struktur Warten.

IC Chip Packaging Technologie Typen: LGA, PGA, BGA

As an SMT engineer in the electronics manufacturing industry, wenn Sie den SMT Oberflächenmontageprozess nicht beherrschen, Es ist schwierig, den Prozess zu analysieren und zu verbessern. Bevor Sie den Montageprozess verstehen, Sie müssen die Verpackungsstruktur von Oberflächenbauteilen beherrschen. Die Paketstruktur und der Montageprozess werden detailliert analysiert.

IC chip and electronic components packaging structure

SMT surface mount component package type classification Surface mount component (SMD) package is the object of surface mount. Das Verständnis der Paketstruktur von SMD ist von großer Bedeutung für die Optimierung des SMT-Prozesses. Die Paketstruktur von SMD ist die Grundlage des Prozessdesigns. Daher, Hier werden wir nicht nach dem Namen der Verpackung klassifiziert, sondern nach der Struktur des Stifts oder des Lötendes. Nach dieser Abteilung, SMD packages mainly include chip components (Chip), J-förmiger Stift, L-förmiger Stift, BGA, BTC, und Schloss.

BGA package introduction:

1. BGA package (Ball Grid Array), je nach Struktur, mainly includes plastic package BGA (P-BGA), flip-chip BGA (F-BGA), carrier tape BGA (T-BGA) and ceramic BGA (C-BGA) ) Four categories.

Das untere Lotendgerät BTC auf dem Straßenbrett ist weit verbreitet, such as special devices such as ball array devices (BGA/CSP/WLP/POP) and QFN/LLP. The BTC package is listed in the BTC package listed in IPC-7093 There are QFN (Quad Flat No-Lead package), SON (SmallOutline No-Lead), DFN (Dual Flat No-Lead), LGA (land Grid Array), MLFP (Micro Leadframe Package).

Unter ihnen, QFN ist ein bleifreies Paket, das quadratisch oder rechteckig ist. Es gibt ein großes freiliegendes Pad in der Mitte der Unterseite des Pakets für Wärmeleitung, Der Anschluss erfolgt durch die großen Pads am Gehäuserand. Weil es kein Blei gibt, Die Montagefläche ist kleiner als QFP, und die Höhe ist niedriger als QFP. Gepaart mit herausragender elektrischer und thermischer Leistung, Diese Art von Verpackung wird zunehmend in der Elektronikindustrie eingesetzt.

QFN Kühlkörper Pad Void Control ist eines der Probleme des QFN Schweißens Prozess, und es ist auch eines der Probleme in der Industrie.

Da kleine Pakete besser geeignet sind, Hochleistungschips zu tragen, Untere Klemmenkomponenten wie QFN werden immer wichtiger. Da die Anforderungen an die Zuverlässigkeitsleistung weiter steigen, Es ist unerlässlich, die thermische und elektrische Leistung von Leistungsmanagementkomponenten in Paketen wie QFN zu optimieren. Darüber hinaus, um Geschwindigkeit und HF-Leistung zu maximieren, Verringerung von Hohlräumen ist sehr wichtig, um den Strompfad der Schaltung zu reduzieren. Wenn die Packungsgröße schrumpft und der Strombedarf steigt, Der Markt erfordert die Reduzierung von Hohlräumen unter den thermischen Pads von QFN-Komponenten. Daher, Es ist notwendig, die wichtigsten Prozessfaktoren zu bewerten, die Hohlräume erzeugen und die beste Lösung zu entwerfen.

Das QFN-Paket verfügt über eine hervorragende thermische Leistung, hauptsächlich wegen des großflächigen Wärmeableitungspads an der Unterseite des Pakets. Um die Wärme effektiv vom Chip zum PCB, der Boden der PCB muss mit entsprechenden Wärmeableitungspads und Wärmeableitungsdurchführungen ausgelegt sein. Das wärmeableitende Pad bietet einen zuverlässigen Lötbereich, und die Durchkontaktierungen bieten eine Möglichkeit, Wärme abzuleiten. Daher, Wenn die freiliegenden Pads auf der Unterseite des Chips mit den Thermopads auf der PCB, Das Gas in der Lötpaste auf den Thermovias und den großformatigen Pads überläuft, die zu bestimmten Gaslöchern führen. Für den SMT-Prozess In Bezug auf große Hohlräume, es ist fast unmöglich, diese Poren zu beseitigen. Die einzige Möglichkeit, die Poren zu reduzieren, ist, sie zu minimieren.

Der vollständige Name von LGA ist "land grid array", oder "Planar Grid Array Package", das ist, Ein Paket mit Array-State-Elektroden-Kontakten auf der Unterseite. Seine Form ist der von BGA Komponenten sehr ähnlich, weil seine Bodengröße größer ist als die von BGA Kugeln. Der Durchmesser ist etwa 2- bis 3-mal größer, und es ist auch schwierig, die Hohlräume zu kontrollieren. Und es ist das gleiche wie QFN Komponenten, die Industrie hat keine relevanten Prozessstandards formuliert, die der elektronischen Verarbeitungsindustrie bis zu einem gewissen Grad Schwierigkeiten bereitet haben.

Der vollständige Name von BGA wird "ball grid array" genannt., oder "Ball Grid Array Paket". Zur Zeit, Die überwiegende Mehrheit der intel mobilen CPUs verwendet diese Verpackungsmethode, zum Beispiel, alle Intel Prozessoren enden auf H, Hauptquartier, U, Y, etc. ((einschließlich, aber nicht beschränkt auf Niederspannung)).

BGA kann das Extremprodukt von LGA und PGA sein, die sich von der Funktion unterscheidet, dass sie nach Belieben ersetzt werden können. Sobald die BGA verpackt ist, Es ist für normale Spieler unmöglich, es auf normale Weise zu zerlegen und zu ersetzen, aber weil es auf einmal getan wird., So kann BGA kürzer und kleiner gemacht werden.

Die wichtigsten Defekte von BGA Chip Lötstellen sind: Hohlräume, desoldering (open circuit), bridging (short circuit), interne Risse in der Lötkugel, Störung der Lötstelle, Kaltlöten, unvollständiges Schmelzen der Lötkugel, and displacement (the solder ball is not aligned with the PCB pad ), Lötperlen, etc.