Einführung

Signalintegrität bezieht sich auf die Qualität des Signals im Schaltungssystem. Wenn das Signal innerhalb der erforderlichen Zeit verzerrungsfrei von der Quelle zum Empfangsende übertragen werden kann, das Signal soll vollständig sein. Mit der schnellen Entwicklung der Halbleitertechnologie und der Verbesserung der IC-Schalterausgangsgeschwindigkeit, signal integrity issues (including signal overshoot and undershoot, Klingeln, Reflexion, Übersprechen, Ground Bounce, etc.) have become one of the issues that must be paid attention to in high-speed PCB-Design. . Normalerweise, Die Frequenz der digitalen Logikschaltung erreicht oder überschreitet 50 MHz, und die Schaltung, die auf dieser Frequenz arbeitet, nimmt mehr als 1 ein/3 des gesamten Systems, kann es High-Speed-Schaltung nennen. In der Tat, verglichen mit der Frequenz des Signals selbst, Die Oberschwingungsfrequenz der Signalkante ist höher, and the rapid changes (rising and falling edges) of the signal cause unexpected effects of signal transmission. Dies ist auch die Quelle von Signalintegritätsproblemen. Daher, Wie man Signalintegritätsfaktoren in der Hochgeschwindigkeit vollständig berücksichtigt PCB-Design Prozess und Durchführung wirksamer Kontrollmaßnahmen zur Verbesserung der Qualität des Schaltungsdesigns ist ein Problem, das berücksichtigt werden muss.

Mit Hilfe der leistungsstarken Simulationssoftware Cadence SPEECTRAQuest ist die Verwendung des IBIS-Modells zur Durchführung von Signalintegritätssimulationsanalysen auf Hochgeschwindigkeitssignalen eine effiziente und durchführbare Analysemethode, die Signalintegritätsprobleme finden und Signalintegritätsprobleme basierend auf den Simulationsergebnissen durchführen kann. um den Zweck der Verbesserung der Entwurfsqualität und der Verkürzung des Entwurfszyklus zu erreichen.

1 Anwendungsbeispiel

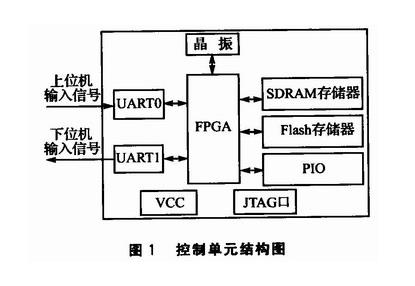

Die Funktion der in diesem Artikel entworfenen Steuereinheit im gesamten System besteht darin, das von der Erdungsempfängervorrichtung empfangene codierte Signal zurück an das Rechenzentrum der Hauptstation zu senden. Der spezifische Arbeitsprozess besteht darin, zuerst die Hostcomputerdaten zu speichern und dann durch den Bitfehlerratetest und die Berechnung einen Pfad mit der niedrigsten Bitfehlerrate als Datenübertragungspfad auszuwählen und schließlich die gespeicherten Hostcomputerdaten an das Hauptstationsdatenbearbeitungszentrum durch diesen Pfad zu übertragen. Nach umfassender Überlegung wurde Alteras Cyclone II-2C8 als Kernchip sowie extern erweiterte SDRAM, Flash, verschiedene Ein-/Ausgangsschaltungen und MAX232-Schnittstellenchips usw. ausgewählt und mit Nios II Soft-Core-Prozessor-Entwicklungskit kombiniert, um zu erreichen. Der Aufbau der Steuereinheit ist in Abbildung 1 dargestellt.

Die Taktfrequenz des CycloneII-2C8 beträgt bis zu 150 MHz oder mehr. Da der Datenspeicherbereich innerhalb des FPGA relativ klein ist, wird SDRAM verwendet, um den externen Datenspeicherplatz zu erweitern. SDRAM verwendet Hy-nix Company HY57V651610/SO, die Taktfrequenz erreicht über 75 MHz. Daher ist es notwendig, die Signalintegritätsprobleme zu berücksichtigen, die durch die zu hohe Signalfrequenz verursacht werden. Ich entschied mich für die leistungsstarke CAD-ence-Design-Software, die Schaltplanentwurf, PCB-Layout und Hochgeschwindigkeits-Simulationsanalyse integriert. Es kann die Probleme im Zusammenhang mit der elektrischen Leistung in allen Aspekten des Entwurfs lösen und das Design erheblich verbessern. Erfolgsquote.

2 Schlüsselsignaltopologie und Simulation

Die höherfrequenten Teile in diesem System sind FPGA und SDRAM. Die Taktfrequenz von FPGA kann mehr als 150 MHz erreichen, und die Taktfrequenz von SDRAM kann mehr als 75 MHz erreichen. Weil die interne Hochfrequenz von FPGA keine Auswirkungen auf andere Geräte hat, und die Verbindung zwischen FPGA und SDRAM ist nahtlos, Die Signalintegrität beeinflusst direkt, ob FPGA SDRAM richtig lesen und schreiben kann. In PCB-Design, Das Hochgeschwindigkeits-Simulationstool SPECCTRAQuest von Cadence wird verwendet, und das IBIS-Modell des Geräts wird verwendet, um die Signalintegrität zu analysieren, und die Impedanzanpassung und Topologiestruktur sind optimiert, um den normalen Betrieb des Systems sicherzustellen. Dieser Artikel gibt nur eine detaillierte Erklärung der Signalreflexion und Übersprechen, und andere Simulationen sind ähnlich.

2.1 Reflexion

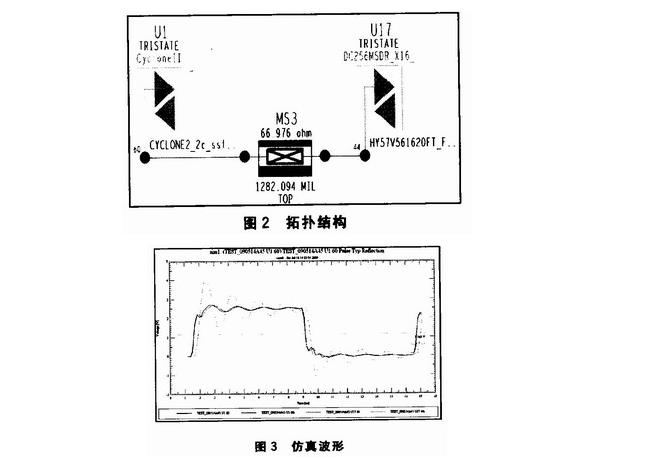

Das sendende Ende ist 44-Stifte von HY57V561620, das Empfangsende ist 60-Stifte von Zyklon II, und die Anregung ist eine 66-MHz-Quadratwelle. Abbildung 2 zeigt die topologische Struktur und Abbildung 3 zeigt die simulierte Wellenform.

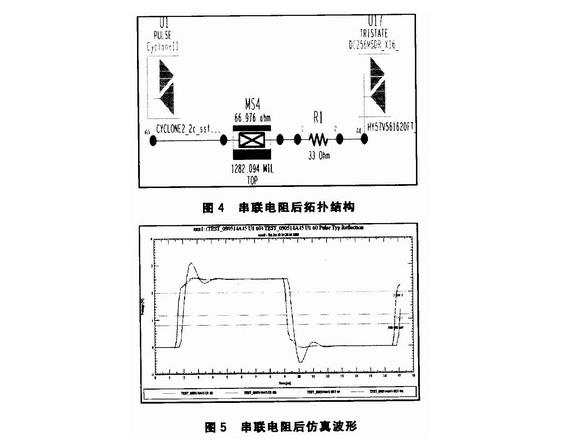

Aus der Simulationswellenform kann ersichtlich werden, dass die Wellenformverzerrung durch die Signalreflexion verursacht wird und das offensichtliche Klingelphänom erzeugt wird. Das Vorhandensein des Klingelphänomens bewirkt, dass das Signal die Pegellogikschwelle mehrmals überschreitet, was zur Störung der Logikfunktion führt. Eine effektive Möglichkeit, das Klingelgeräusch zu reduzieren, besteht darin, einen kleinen Widerstand in Reihe mit der Schaltung zu verbinden, der Dämpfung für die Schaltung bietet, die Klingellamplitude erheblich reduzieren und die Klingelschwingungszeit verkürzen kann, während die Schaltungsgeschwindigkeit kaum beeinträchtigt wird. Im technischen Einsatz beträgt der Widerstand in der Regel 33 Ω. Abbildung 4 und Abbildung 5 zeigen die topologische Struktur und simulierte Wellenformen nach dem Reihenwiderstand.

Das Klingelphänomen nach Serienwiderstand ist gut gelöst. In der Tat wird diese Lösung Impedanzanpassung genannt. Impedanz nimmt eine extrem wichtige Position im Problem der Signalintegrität ein.

2.2 Übersprechen

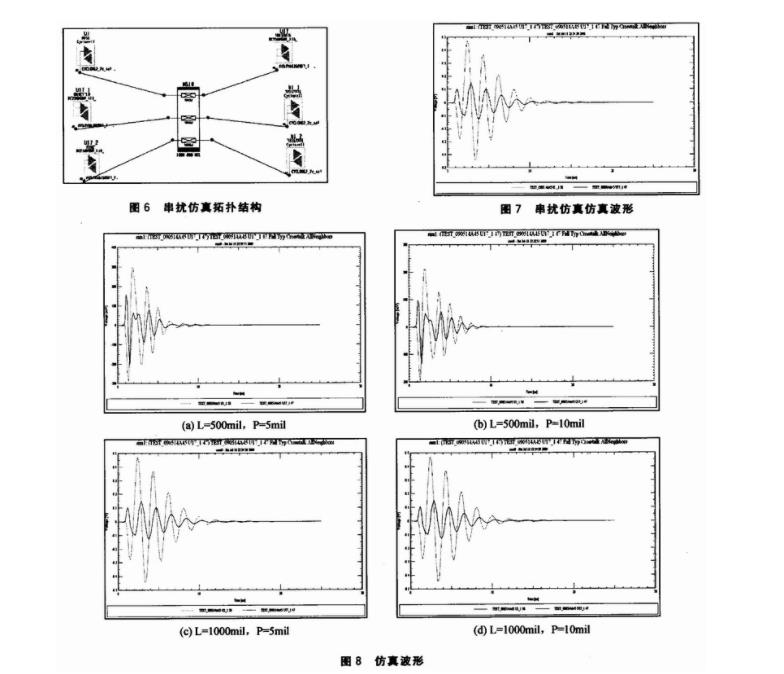

Extrahieren Sie SD_DQlO (verbinden Sie 59-Pins von Zyklon II und 45-Pins von HY57V561620), SD_DQl (verbinden Sie 58-Pins von Zyklon II und 47-Pins von HY57V561620), SD_DQ-l2 (verbinden Sie 57-Pins von Zyklon II und 48-Pins von HY57V561620) diese drei Netzwerke, um Übersprechensimulation zwischen ihnen durchzuführen. Darunter SD_DQll als angegriffenes Netzwerk, SD_DQlO und SD_D-Ql2 als angreifendes Netzwerk. Ihre Topologie und Simulationswellenformen sind in Abbildung 6 und Abbildung 7 dargestellt (die parallele Kopplungslänge der Übertragungsleitung ist L=1000 mil und die Tonhöhe P=5 mil).

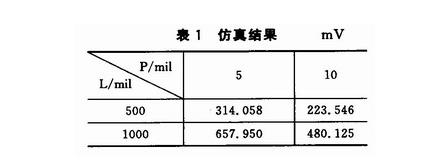

Die Simulationswellenform ist in Abbildung 8 dargestellt. Aus Abbildung 7 ist ersichtlich, dass Übersprechen einen großen Einfluss auf das angegriffene Netzwerk hat. Der Übersprechenwert Übersprechen=657,95 mV bezieht sich auf die Parallelkupplungslänge L und den Abstand P der Übertragungsleitung. Je kürzer die Kupplungslänge, desto größer der Abstand. Je kleiner das Übersprechen. Die Simulationsergebnisse sind in Tabelle 1 aufgeführt.

Daher, bei der Herstellung der PCB, die Parallellänge zwischen den Signalleitungen unterschiedlicher Eigenschaften sollte soweit wie möglich reduziert werden, der Abstand zwischen ihnen sollte erweitert werden, und die Linienbreite und Höhe einiger Linien sollte geändert werden. Natürlich, Es gibt viele Faktoren, die Übersprechen beeinflussen, wie Stromflussrichtung und Frequenzanstiegszeit des Störquellensignals, die umfassend betrachtet werden sollten.

Schlussbemerkungen

In dieser Hochgeschwindigkeit PCB-Design der Steuereinheit, Die leistungsstarke Cadence Software wurde verwendet, um gute Ergebnisse aus der Erstellung von Schaltplänen zu erzielen, PCB Layout zur Hochgeschwindigkeitssimulationsanalyse. Entsprechend der vernünftigen Topologie und Anordnung, die durch SPEECTRAQuest Simulationsanalyse erhalten wurden, die Leiterplatte kann normal arbeiten. Diese Entwurfsmethode verkürzt die Hardware-Debugging-Zeit erheblich, Verbesserung der Arbeitseffizienz, und spart Konstruktionskosten.