Dieser Artikel erklärt, wie Veränderungen im Prozess dazu führen, dass sich die tatsächliche Impedanz ändert, und wie man genaue Feldlöser verwendet, um dieses Phänomen vorherzusagen. Auch wenn es keine Prozessänderung gibt, Andere Faktoren führen dazu, dass die tatsächliche Impedanz sehr unterschiedlich ist. Wann DesignHochgeschwindigkeitsstrecke Bretter, automatisiert Design Tools können dieses unoffensichtliche, aber sehr wichtige Problem manchmal nicht finden. Allerdings, Solange einige Maßnahmen in den frühen Schritten der Design, dieses Problem kann vermieden werden. Diese Technik wird "defensiv" genannt Design".

Die Anzahl der Stapel

Eine gute laminierte Struktur ist die beste vorbeugende Maßnahme für die meisten Signalintegritätsprobleme und EMV-Probleme und wird von den Menschen am meisten missverstanden. Hier spielen mehrere Faktoren eine Rolle, und ein guter Weg, ein Problem zu lösen, kann andere Probleme verschlimmern. Viele SystemDesignanbieter schlagen vor, dass es mindestens eine kontinuierliche Ebene in der Leiterplatte geben sollte, um die charakteristische Impedanz und Signalqualität zu steuern. Solange die Kosten erschwinglich sein können, ist dies ein guter Vorschlag. EMV-Berater empfehlen oft, eine Bodenfüllung oder Bodenschicht auf die äußere Schicht zu legen, um elektromagnetische Strahlung und Empfindlichkeit gegenüber elektromagnetischen Störungen zu kontrollieren. Dies ist auch unter bestimmten Bedingungen ein guter Vorschlag.

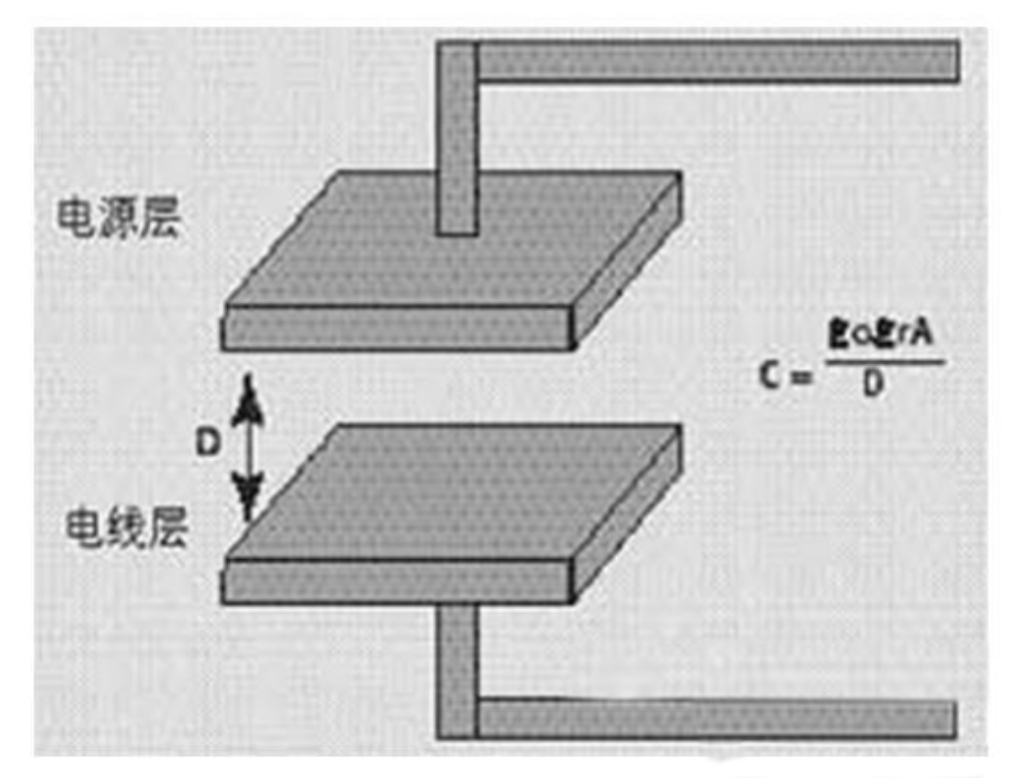

Abbildung 1: Analysieren Sie das Signalproblem in der laminierten Struktur mit dem Kapazitätsmodell

Allerdings, durch transiente Ströme, Diese Methode kann in einigen allgemeinen Designs. Erstens, Lassen Sie uns den einfachen Fall eines Paares von Leistungsebene betrachten/Masseebene: es kann als Kondensator gesehen werden. Es kann davon ausgegangen werden, dass die Leistungsschicht und die Bodenschicht die beiden Platten des Kondensators sind. Um einen größeren Kapazitätswert zu erhalten, it is necessary to move the two plates closer (distance D) and increase the dielectric constant (εâ¼râ¼). Je größer die Kapazität, je niedriger die Impedanz, was wir wollen, weil es Geräusche unterdrücken kann. Egal wie die anderen Schichten angeordnet sind, Die Hauptstromschicht und die Bodenschicht sollten benachbart und in der Mitte des Stapels liegen. Wenn der Abstand zwischen der Leistungsschicht und der Bodenschicht groß ist, Es verursacht eine große Stromschleife und bringt viel Rauschen. Für eine 8-lagige Platte, Das Platzieren der Power-Schicht auf einer Seite und der Ground-Schicht auf der anderen Seite verursacht folgende Probleme:

1. Maximales Übersprechen. Durch die Erhöhung der gegenseitigen Kapazität ist das Übersprechen zwischen den Signalschichten größer als das Übersprechen der Schichten selbst.

2. Die größte Auflage. Strom fließt um jede Leistungsebene und parallel zum Signal tritt eine große Menge Strom in die Hauptleistungsebene ein und kehrt durch die Erdungsebene zurück. Die EMV-Eigenschaften verschlechtern sich aufgrund des Anstiegs des Umwälzstroms.

3. Verlust der Kontrolle über die Impedanz. Je weiter das Signal von der Steuerschicht entfernt ist, desto geringer ist die Genauigkeit der Impedanzsteuerung aufgrund anderer Leiter um sie herum.

4. Weil es einfach ist, Lötkürze zu verursachen, kann es die Kosten des Produkts erhöhen.

Wir müssen eine Kompromisslösung zwischen Leistung und Kosten treffen. Wie kann man also die digitale Leiterplatte anordnen, um die besten SI- und EMV-Eigenschaften zu erhalten?

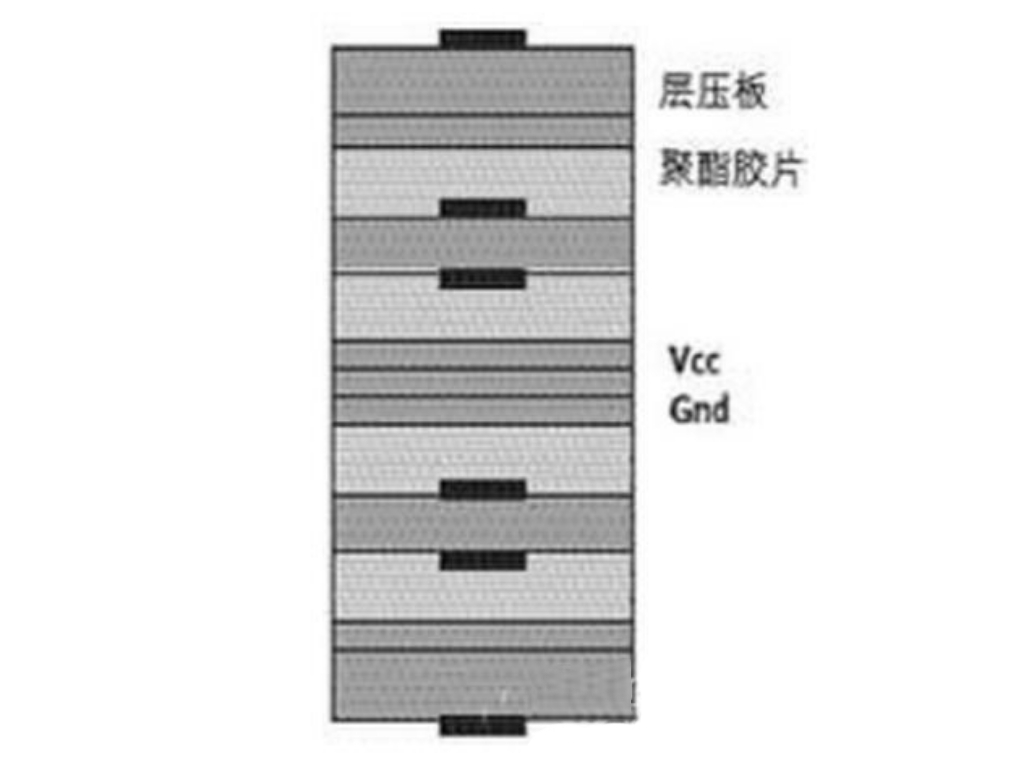

Die Verteilung der einzelnen Schichten der PCB ist im Allgemeinen symmetrisch. Mehr als zwei Signalschichten sollten nicht nebeneinander platziert werden; sonst, die Kontrolle über SI wird weitgehend verloren gehen. Am besten platzieren Sie die internen Signalschichten symmetrisch paarweise. Es sei denn, einige Signale müssen mit SMT-Geräten verdrahtet werden, Wir sollten die Signalverdrahtung auf der äußeren Schicht minimieren.

Abbildung 2: Der erste Schritt einer guten Designlösung besteht darin, die laminierte Struktur korrekt zu entwerfen

For circuit Bretter mit mehr Schichten, Wir können diese Platzierungsmethode viele Male wiederholen. Es ist auch möglich, zusätzliche Leistungsschichten und Bodenschichten hinzuzufügen; solange sichergestellt ist, dass zwischen den beiden Leistungsschichten kein Paar Signalschichten vorhanden ist.

Die Verdrahtung von Hochgeschwindigkeitssignalen sollte in demselben Paar Signalschichten angeordnet sein; es sei denn, dieser Grundsatz muss durch den Anschluss von SMT-Geräten verletzt werden. Alle Spuren eines Signals sollten einen gemeinsamen Rückweg haben (d.h. die Erdungsebene). Es gibt zwei Ideen und Methoden, um zu beurteilen, welche zwei Schichten als Paar betrachtet werden können:

1. Stellen Sie sicher, dass die Rückmeldungen bei gleichen Abständen genau gleich sind. Das bedeutet, dass die Signale symmetrisch auf beiden Seiten der inneren Masseebene geführt werden sollten. Der Vorteil davon ist, dass es einfach ist, die Impedanz und den Zirkulationsstrom zu steuern; Der Nachteil ist, dass es viele Durchgänge auf der Bodenschicht gibt, und es gibt einige nutzlose Schichten.

2. Zwei Signalschichten der benachbarten Verdrahtung. Der Vorteil ist, dass die Durchkontaktierungen in der Bodenschicht auf ein Minimum kontrolliert werden können (mit vergrabenen Durchkontaktierungen); Der Nachteil ist, dass die Wirksamkeit dieser Methode für einige Schlüsselsignale reduziert wird.

Bei dem zweiten Verfahren sollte der Masseanschluss zum Ansteuern und Empfangen des Signals vorzugsweise direkt mit der an die Signalverdrahtungsschicht angrenzenden Schicht verbunden sein. Als einfaches Verdrahtungsprinzip sollte die Oberflächenverdrahtungsbreite in Zoll weniger als ein Drittel der Antriebsanstiegszeit in Nanosekunden betragen (zum Beispiel beträgt die Verdrahtungsbreite von Hochgeschwindigkeits-TTL 1 Zoll).

Wenn es von mehreren Netzteilen mit Strom versorgt wird, muss eine Masseschicht zwischen die Stromversorgungskabel gelegt werden, um sie zu trennen. Kondensatoren können nicht gebildet werden, um Wechselstrom-Kopplung zwischen Netzteilen zu vermeiden.

Die oben genannten Maßnahmen dienen alle dazu, die Zirkulation und Übersprechen zu reduzieren und die Impedanzsteuerungsfähigkeit zu stärken. Die Masseebene wird auch eine effektive EMV "Abschirmbox" bilden. Unter der Voraussetzung, den Einfluss auf die charakteristische Impedanz zu berücksichtigen, kann die ungenutzte Oberfläche in eine Bodenschicht umgewandelt werden.

Charakteristische Impedanz

Eine gute laminierte Struktur kann die Impedanz effektiv steuern, und ihre Verdrahtung kann eine leicht verständliche und vorhersehbare Übertragungsleitungsstruktur bilden. Vor-Ort-Lösungstools können solche Probleme gut bewältigen, solange die Anzahl der Variablen auf ein Minimum kontrolliert wird, können ziemlich genaue Ergebnisse erzielt werden.

Wenn jedoch drei oder mehr Signale gestapelt sind, ist dies nicht unbedingt der Fall, und der Grund ist subtil. Der Sollimpedanzwert hängt von der Prozesstechnik des Gerätes ab. Hochgeschwindigkeits-CMOS-Technologie kann im Allgemeinen etwa 70Ω; Hochgeschwindigkeits-TTL-Geräte können im Allgemeinen etwa 80Ω bis 100Ω erreichen. Da der Impedanzwert normalerweise einen großen Einfluss auf Rauschtoleranz und Signalschaltung hat, ist es notwendig, bei der Wahl der Impedanz sehr vorsichtig zu sein; Das Produkthandbuch sollte hierzu Hinweise geben.

Die ersten Ergebnisse des Vor-Ort-Lösungstools können auf zwei Arten von Problemen stoßen. Das erste ist das Problem der eingeschränkten Sicht. Das Feldlösungstool analysiert nur den Einfluss von nahe gelegenen Leiterbahnen und berücksichtigt nicht parallele Leiterbahnen auf anderen Schichten, die die Impedanz beeinflussen. Das Lösungstool vor Ort kann die Details vor der Verdrahtung, d.h. bei der Zuweisung der Leiterbahnbreite, nicht kennen, aber die oben genannte Paaranordnungsmethode kann dieses Problem minimieren.

Erwähnenswert ist der Einfluss von Teilleistungsebenen. Die äußere Leiterplatte ist nach der Verdrahtung oft mit geerdeten Kupferdrähten überfüllt, was vorteilhaft ist, EMI und Balancing zu unterdrücken. Wenn nur solche Maßnahmen für die äußere Schicht getroffen werden, hat die in diesem Artikel empfohlene laminierte Struktur einen sehr geringen Einfluss auf die charakteristische Impedanz.

Der Effekt der Verwendung einer großen Anzahl benachbarter Signalschichten ist sehr signifikant. Einige Vor-Ort-Lösungswerkzeuge können das Vorhandensein von Kupferfolie nicht finden, da sie nur die gedruckten Linien und die gesamte Schicht überprüfen können, so dass das Ergebnis der Impedanzanalyse falsch ist. Wenn sich Metall auf der benachbarten Schicht befindet, wirkt es wie eine weniger zuverlässige Bodenschicht. Wenn die Impedanz zu niedrig ist, wird der momentane Strom groß sein, was ein praktisches und empfindliches EMI-Problem ist.

Ein weiterer Grund für den Ausfall von Impedanzanalysewerkzeugen sind verteilte Kondensatoren. Diese Analysewerkzeuge können den Einfluss von Pins und Vias in der Regel nicht abbilden (dieser Einfluss wird normalerweise mit einem Simulator analysiert). Dieser Effekt kann besonders auf der Backplane signifikant sein. Der Grund ist sehr einfach: Die charakteristische Impedanz kann in der Regel durch die folgende Formel berechnet werden: â�L/C

Unter ihnen sind L und C die Induktivität bzw. Kapazität pro Einheitslänge.

Wenn die Pins gleichmäßig angeordnet sind, wirkt sich die zusätzliche Kapazität stark auf das Berechnungsergebnis aus. Die Formel wird lauten: âL/(C+C')

C'ist die Pin-Kapazität pro Einheitslänge.

Wenn die Steckverbinder in einer geraden Linie wie auf der Backplane angeschlossen sind, können die Gesamtleitungskapazität und die Gesamtpin-Kapazität außer dem ersten und letzten Pins verwendet werden. Auf diese Weise wird die effektive Impedanz reduziert und kann sogar von 80Ω auf 8Ω fallen. Um den effektiven Wert zu finden, muss der ursprüngliche Impedanzwert geteilt werden durch: â�(1+C'/C)

Diese Berechnung ist für die Bauteilauswahl sehr wichtig.

Verzögerung

Bei der Simulation sollte die Kapazität der Komponente und des Gehäuses (und manchmal sollte auch die Induktivität berücksichtigt werden) berücksichtigt werden. Zwei Punkte sollten beachtet werden: Zunächst einmal kann der Simulator verteilte Kondensatoren möglicherweise nicht korrekt simulieren; Zweitens ist es notwendig, auf die Auswirkungen unterschiedlicher Produktionsbedingungen auf unvollständige Schichten und nicht parallele Spuren zu achten. Viele Vor-Ort-Lösungstools können die Stapelverteilung ohne volle Leistung oder Erdungsebenen nicht analysieren. Wenn sich jedoch eine Masseschicht neben der Signalschicht befindet, wird die berechnete Verzögerung ziemlich schlecht sein, wie ein Kondensator, wird es die größte Verzögerung geben; Wenn eine doppelseitige Platine viele Massedrähte und VCC-Kupferfolie auf beiden Schichten hat, ist diese Situation noch schlimmer. Wenn der Prozess nicht automatisiert ist, wird die Einrichtung dieser Dinge in einem CAD-System sehr chaotisch.

EMV

Es gibt viele Faktoren, die die EMV beeinflussen, von denen viele in der Regel nicht analysiert werden. Selbst wenn sie analysiert werden, ist es oft zu spät, nachdem das Design abgeschlossen ist. Im Folgenden sind einige Faktoren aufgeführt, die die EMV beeinflussen:

1. Die Schlitze in der Leistungsebene bilden eine Viertelwellenlängenantenne. Für Fälle, in denen Montagenuten an Metallbehältern erforderlich sind, sollten stattdessen Bohrmethoden verwendet werden.

2. Induktive Komponenten. Ich traf einmal einen Designer, der alle Designregeln befolgte und Simulationen machte, aber seine Leiterplatte hat immer noch viele Strahlungssignale. Der Grund ist, dass zwei Induktoren parallel zueinander auf der obersten Schicht platziert sind, um einen Transformator zu bilden.

3. Aufgrund des Einflusses der unvollständigen Masseebene verursacht die niedrige Impedanz der inneren Schicht einen großen transienten Strom in der äußeren Schicht.

Die meisten dieser Probleme können durch die Annahme einer defensiven Design. Zunächst einmal, Die richtige Stapelstruktur und Verdrahtungsstrategie sollte erstellt werden, damit ein guter Start gemacht werden kann.

Einige grundlegende Fragen wie Netztopologie, Signalverzerrungsursachen und Übersprecherberechnungsmethoden werden hier nicht behandelt. Es werden nur einige sensible Themen analysiert, um den Lesern zu helfen, die Ergebnisse des EDA-Systems anzuwenden. Jede Analyse hängt vom verwendeten Modell ab, und nicht analysierte Faktoren beeinflussen auch die Ergebnisse. Zu kompliziert zu sein, ist wie zu ungenau zu sein. Das Vermeiden von zu vielen Parameteränderungen (z. B. gedruckte Linienbreite usw.) hilft bei einem sauberen und konsistenten Design.