In der Design der Hochgeschwindigkeit PCB Bretter, via Design ist ein wichtiger Faktor. Es besteht aus Löchern, Pad Bereiche um die Löcher, und Isolationsbereiche der POWER-Schicht. Sie werden normalerweise in drei Arten unterteilt: blinde Löcher, vergrabene Löcher und Durchgangslöcher. In the PCB LeiterplattenDesignprozess, durch die Analyse der parasitären Kapazität und parasitären Induktivität der Vias, some precautions in the high-speed Leiterplatteüber Design werden zusammengefasst.

Zur Zeit, the Design der Hochgeschwindigkeits-Leiterplatte s is widely used in the fields of communications, Computer, Grafik und Bildverarbeitung, und alle elektronischen High-Tech-ProduktDesigns verfolgen Merkmale wie niedrigen Stromverbrauch, geringe elektromagnetische Strahlung, hohe Zuverlässigkeit, Miniaturisierung, und leicht. Um die oben genannten Ziele zu erreichen, via Design is an important factor in high-speed Leiterplatte Design.

1. Via

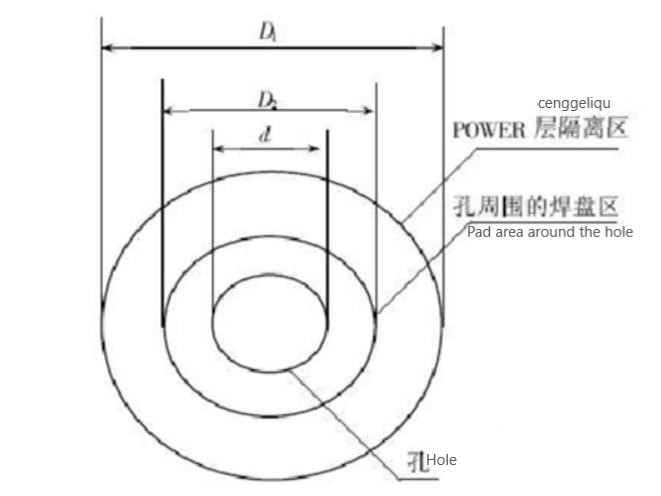

Via ist ein wichtiger Faktor in der Mehrschicht PCB-Design. A via besteht hauptsächlich aus drei Teilen, eins ist das Loch; Die andere ist der Pad Bereich um das Loch; und der dritte ist der Isolationsbereich der POWER-Schicht. Der Prozess des Durchgangslochs besteht darin, eine Metallschicht auf der zylindrischen Oberfläche der Lochwand des Durchgangslochs durch chemische Abscheidung zu platten, um die Kupferfolie zu verbinden, die mit den mittleren Schichten verbunden werden muss, Die Form kann direkt mit den Linien auf der oberen und unteren Seite verbunden werden, oder nicht verbunden. Vias können die Rolle der elektrischen Verbindung spielen, Befestigungs- oder Positioniervorrichtungen. Das schematische Diagramm des Durchgangs ist in Abbildung 1 dargestellt.

Abbildung 1: Schematische Darstellung der Durchkontaktierungen

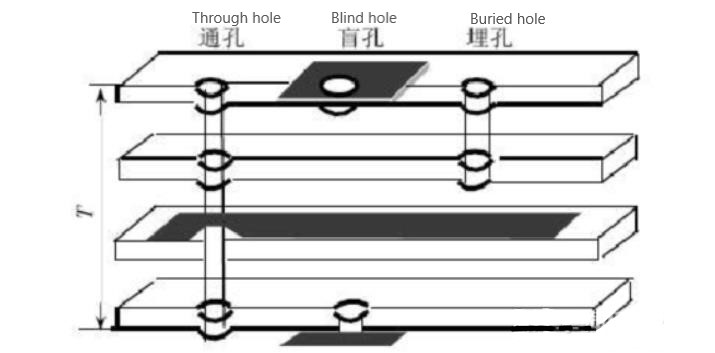

Vias werden im Allgemeinen in drei Kategorien unterteilt: blinde Löcher, vergrabene Löcher und Durchgangslöcher.

Blindlöcher befinden sich auf der Ober- und Unterseite der Leiterplatte und haben eine bestimmte Tiefe. Sie werden verwendet, um die Oberflächenlinie und die darunterliegende innere Linie zu verbinden. Die Tiefe des Lochs und der Durchmesser des Lochs überschreiten normalerweise ein bestimmtes Verhältnis nicht.

Begrabenes Loch bezieht sich auf das Verbindungsloch in der inneren Schicht der Leiterplatte, das sich nicht bis zur Oberfläche der Leiterplatte erstreckt.

Sowohl blinde als auch vergrabene Löcher befinden sich in der inneren Schicht der Leiterplatte und werden durch einen Durchgangslochformungsprozess vor der Laminierung abgeschlossen, und mehrere innere Schichten können während der Bildung des Durchgangs überlappt werden. Durchgangslöcher, die die gesamte Leiterplatte durchlaufen, können zur internen Verschaltung oder als Einbaupositionierungsloch eines Bauteils verwendet werden. Da Durchgangslöcher im Prozess einfacher zu implementieren sind und niedrigere Kosten verursachen, verwenden Leiterplatten im Allgemeinen Durchgangslöcher. Die Klassifizierung der Durchkontaktierungen ist in Abbildung 2 dargestellt.

Abbildung 2: Klassifizierung der Durchkontaktierungen

2. Parasitische Kapazität von Durchkontaktierungen

Die Via selbst hat parasitäre Kapazität zur Erdung. Wenn der Durchmesser des Isolationslochs auf der Bodenschicht des Durchgangs D2 ist, ist der Durchmesser des Durchgangs D1, die Dicke der Leiterplatte ist T, und die Dielektrizitätskonstante des Leiterplattensubstrats ist E, dann ist die parasitäre Kapazität des Durchgangs ungefähr: C=1.41ETD1/((D2-D1))

Der Haupteffekt der parasitären Kapazität des Durchgangslochs auf der Schaltung besteht darin, die Anstiegszeit des Signals zu verlängern und die Geschwindigkeit der Schaltung zu verringern. Je kleiner der Kapazitätswert, desto kleiner der Effekt.

3. Parasitische Induktivität von Vias

Das Via selbst hat parasitäre Induktivität. Bei der Konstruktion von Hochgeschwindigkeits-Digitalschaltungen ist der Schaden, der durch die parasitäre Induktivität des Durchgangs verursacht wird, oft größer als der Einfluss der parasitären Kapazität. Die parasitäre Reiheninduktivität des Durchgangs schwächt die Funktion des Bypass-Kondensators und schwächt die Filterwirkung des gesamten Stromsystems. Wenn L sich auf die Induktivität des Durchgangs bezieht, ist h die Länge des Durchgangs und d ist der Durchmesser des Mittellochs, die parasitäre Induktivität des Durchgangs ist ähnlich wie:

L=5,08hï¼"ln(4h/d)+1ï¼½

Aus der Formel ist ersichtlich, dass der Durchmesser des Durchgangs einen geringen Einfluss auf die Induktivität hat und die Länge des Durchgangs den größten Einfluss auf die Induktivität hat.

4. Nicht durchgehende Technologie

Non-through Vias umfassen blinde Vias und vergrabene Vias. In der Non-Through-Technologie kann die Anwendung von blinden Durchkontaktierungen und vergrabenen Durchkontaktierungen die Größe und Qualität der Leiterplatte erheblich reduzieren, die Anzahl der Schichten reduzieren, die elektromagnetische Verträglichkeit verbessern, die Eigenschaften elektronischer Produkte erhöhen, Kosten senken und auch die Entwurfsarbeit einfacher und schneller machen.

Im traditionellen PCB-Design und -Verarbeitung können Durchgangslöcher viele Probleme bringen. Erstens nehmen sie eine große Menge effektiven Platzes ein, und zweitens sind eine große Anzahl von Durchgangslöchern dicht an einer Stelle verpackt, was auch ein großes Hindernis für die innere Schichtverdrahtung der mehrschichtigen Leiterplatte schafft. Diese Durchgangslöcher nehmen den für die Verdrahtung erforderlichen Platz ein und durchlaufen intensiv die Stromversorgung und den Boden. Die Oberfläche der Drahtschicht zerstört auch die Impedanzmerkmale der Stromerddrahtschicht und macht die Stromerddrahtschicht unwirksam. Und die herkömmliche mechanische Methode des Bohrens wird 20-mal die Arbeitsbelastung der Nicht-Durchgangslochtechnologie sein.

In PCB-Design, obwohl die Größe der Pads und Vias allmählich abgenommen hat, if die Dicke der board layer is not proportionally reduced, das Seitenverhältnis des Durchgangslochs erhöht sich, und die Erhöhung des Seitenverhältnisses des Durchgangslochs verringert die Zuverlässigkeit. Mit der Reife der fortschrittlichen Laserbohrtechnologie und Plasma-Trockenätztechnologie, Es ist möglich, nicht durchdringende kleine blinde Löcher und kleine vergrabene Löcher aufzubringen. Wenn der Durchmesser dieser nicht penetrierenden Vias 0 ist.3mm, die parasitären Parameter werden ungefähr 1 sein/10 der ursprünglichen konventionellen Bohrung, die Zuverlässigkeit der PCB. Durch die Non-Through via Technologie, Es gibt wenige große Vias auf der PCB, die mehr Platz für Routing bieten können.

Der verbleibende Platz kann für großflächige Abschirmungen genutzt werden, um die EMI/RFI-Leistung zu verbessern. Gleichzeitig kann auch mehr verbleibender Platz für die innere Schicht genutzt werden, um das Gerät und die wichtigsten Netzwerkkabel teilweise abzuschirmen, so dass es die beste elektrische Leistung hat. Die Verwendung von nicht durchgehenden Durchkontaktierungen erleichtert das Auslüften der Gerätestifte, macht es einfach, Stiftgeräte mit hoher Dichte (wie BGA-verpackte Geräte) zu routen, die Verdrahtungslänge zu verkürzen und die Timing-Anforderungen von Hochgeschwindigkeitsschaltungen zu erfüllen.

5. Über Auswahl im Normalfall PCB

Im gewöhnlichen PCB-Design haben die parasitäre Kapazität und die parasitäre Induktivität des Durchgangs wenig Einfluss auf das PCB-Design. Für den 1-4-Schicht-PCB-Entwurf wird im Allgemeinen 0.36mm/0.61mm/1.02mm ausgewählt, (Bohr-/Pad/POWER-Isolationsbereich) Durchgänge sind besser. Für einige Signalleitungen mit speziellen Anforderungen (wie Stromleitungen, Erdungsleitungen, Taktleitungen usw.), können Sie 0.41mm/0.81mm/1.32mm Durchgänge wählen, oder Sie können andere Größen entsprechend der tatsächlichen Situation verwenden.

6. Über Design in Hochgeschwindigkeits-PCB

Durch die obige Analyse der parasitären Eigenschaften von Durchkontaktierungen können wir sehen, dass scheinbar einfache Durchkontaktierungen im Hochgeschwindigkeits-PCB-Design oft große negative Auswirkungen auf das SchaltungsDesign haben. Um die negativen Auswirkungen, die durch die parasitären Effekte der Vias verursacht werden, zu reduzieren, kann im Design Folgendes getan werden:

(1) Wählen Sie eine angemessene Größe. Für mehrschichtiges Leiterplattendesign mit allgemeiner Dichte ist es besser, 0.25mm/0.51mm/0.91mm (gebohrte Löcher/Pads/POWER-Isolationsbereich) Durchgänge zu verwenden; Für einige Leiterplatten mit hoher Dichte kann 0.20mm/0.46 auch verwendet werden Für Durchgänge von mm/0.86mm, können Sie auch nicht-durchgehende Durchgänge versuchen; Für Strom- oder Masseverbindungen können Sie eine größere Größe zur Reduzierung der Impedanz in Betracht ziehen;

(2) Je größer die POWER-Isolationsfläche, desto besser, wenn man die Durchgangsdichte auf der Leiterplatte betrachtet, im Allgemeinen D1=D2+0.41mm

(3) Die Signalspuren auf der Leiterplatte sollten nicht so weit wie möglich verändert werden, das heißt, die Durchkontaktierungen sollten so weit wie möglich reduziert werden;

(4) The use of a thinner PCB ist vorteilhaft, um die beiden parasitären Parameter der Via zu reduzieren;

(5) Die Strom- und Erdungsstifte sollten über Löcher in der Nähe hergestellt werden. Je kürzer die Leitung zwischen Durchgangsloch und Stift ist, desto besser, da sie die Induktivität erhöhen. Gleichzeitig sollten die Strom- und Masseleitungen so dick wie möglich sein, um die Impedanz zu reduzieren;

(6) Place some grounding vias near the vias of the signal layer to provide a short-distance loop for the signal. Natürlich, Spezifische Fragestellungen müssen bei der Gestaltung detailliert analysiert werden. Sowohl Kosten als auch Signalqualität berücksichtigen, in high-speed PCB-Design, Designer hoffen immer, dass je kleiner das Durchgangsloch ist, die bessere, so dass mehr Verdrahtungsraum auf der Platine gelassen werden kann. Darüber hinaus, je kleiner das Durchgangsloch, Je kleiner die parasitäre Kapazität, je besser geeignet für Hochgeschwindigkeitsstrukturen. In hoher Dichte PCB-Design, Die Verwendung von nicht durchgehenden Vias und die Verringerung der Größe der Vias haben zu einem Kostenanstieg geführt, und die Größe der Durchkontaktierungen kann nicht unbegrenzt reduziert werden. Es ist betroffen von PCB Bohr- und Galvanikprozesse der Hersteller. Technische Beschränkungen sollten in der über Design of high-speed PCBs.