SMT patch existe - t - il des moyens de réduire certains problèmes d'échec?

SMT patch est une abréviation pour une série de processus de traitement sur la base de PCB. PCB (Printed Circuit Board) est un type de carte de circuit imprimé. Alors, y a - t - il un moyen pour les correctifs SMT de réduire certains problèmes d'échec?

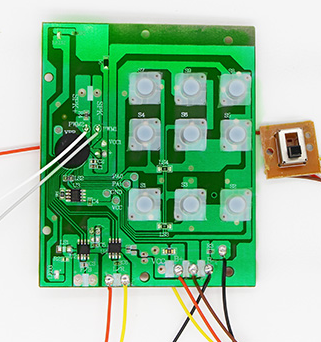

Patch SMT

Le processus de fabrication, la manipulation et les tests d'assemblage de circuits imprimés (PCA) peuvent tous soumettre le boîtier à des contraintes mécaniques importantes pouvant entraîner des défaillances. À mesure que les paquets Grid Array deviennent plus volumineux, il devient de plus en plus difficile de définir un niveau de sécurité pour ces étapes.

La méthode d'essai de point de flexion monotone est une caractéristique typique de l'emballage depuis de nombreuses années. Cet essai est décrit dans le document IPC / jedec - 9702 "monotone flexion Characteristics of Board - level interconnections". Cette méthode d'essai décrit la résistance à la rupture sous charge de flexion des interconnexions horizontales de cartes de circuits imprimés.

Cependant, cette méthode d'essai ne permet pas de déterminer la tension maximale admissible.

Pour les processus de fabrication et d'assemblage, en particulier les PCA sans plomb, l'un de leurs défis est l'incapacité de mesurer directement les contraintes sur les points de soudure. L'indicateur le plus couramment utilisé pour décrire le risque d'un composant interconnecté est la tension de la carte de circuit imprimé PCB adjacente au composant, décrite dans le document IPC / jedec - 9704 "Printed Circuit Board Strain test guidelines".

Intel a pris conscience du problème il y a quelques années et a commencé à développer une stratégie de test différente pour recréer le pire scénario de flexion en pratique. D'autres entreprises comme HP ont également réalisé les avantages d'autres méthodes de test et ont commencé à envisager des idées similaires à celles d'Intel. Cette approche suscite de plus en plus d'attention, car de plus en plus de fabricants de puces et de clients réalisent qu'il est important de déterminer les limites de tension pour minimiser les défaillances mécaniques lors de la fabrication, de la manipulation et des tests. Intérêt

Avec l'expansion de l'utilisation de l'équipement sans plomb, les utilisateurs sont de plus en plus intéressés; Parce que de nombreux utilisateurs sont confrontés à des problèmes de qualité.

Avec l'intérêt croissant de toutes les parties, IPC a jugé nécessaire d'aider d'autres entreprises à développer diverses méthodes d'essai pour s'assurer que le BGA ne soit pas endommagé pendant la fabrication et les essais. Ces travaux, menés conjointement par le Groupe de travail IPC 6 - 10D SMT sur les méthodes d'essai de fiabilité des accessoires et le Sous - Comité jedec JC - 14.1 sur les méthodes d'essai de fiabilité des ensembles complets d'équipements, ont été achevés.

Cette méthode d'essai spécifie huit points de contact disposés en une matrice circulaire. Le PCA avec BGA monté au centre de la carte de circuit imprimé PCB est placé de cette façon: le composant est monté face vers le bas sur la broche de support et la charge est appliquée sur la face arrière du BGA. Placez la jauge de contrainte près de la pièce conformément à la disposition de jauge de contrainte recommandée dans IPC / jedec - 9704.

Le PCA sera plié aux niveaux de tension pertinents et l'analyse de défaillance peut déterminer l'étendue des dommages causés par la déviation de ces niveaux de tension. Les méthodes itératives peuvent être utilisées pour déterminer le niveau de tension qui ne causera pas de dommages. C'est la limite de tension.