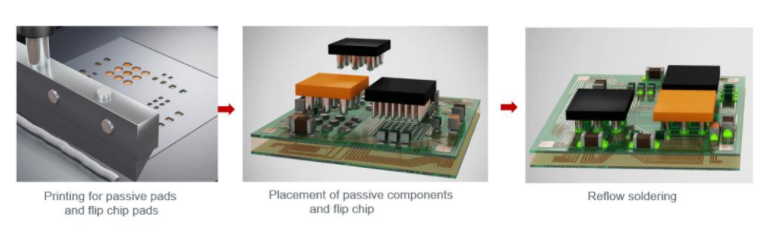

Flip chip, come suggerisce il nome, è un metodo di imballaggio in cui il lato anteriore del chip (il lato in cui è realizzato il circuito IC) è collegato al substrato verso il basso. I terminali di segnale elettrici sono fatti di saldatura tradizionale e possono essere interconnessi con il substrato. In questo tipo di interconnessione, i terminali di ingresso e uscita (I/O) possono coprire l'intero chip, quindi anche allo stesso passo, la densità dell'interconnessione flip-chip è molto più alta di quella dell'incollaggio del cavo. Nell'interconnessione del legame metallico, I/O può essere organizzato solo intorno al chip. Pertanto, non importa quanto sia piccolo il passo, la densità I/O dell'interconnessione flip-chip non può essere raggiunta. Poi la tecnologia bump è la chiave dell'intera tecnologia di interconnessione flip-chip.

Panoramica della tecnologia di bumping wafer La chiave per creare urti wafer è depositare uno strato metallico sotto-bump (UBM). Va sottolineato che il termine utilizzato da IBM nei primi giorni è lo strato di metallizzazione a sfera vincolata (BLM), che funziona come: fornire uno strato di legame per l'interconnessione; fornire uno strato di barriera di diffusione atomica per impedire la diffusione degli atomi del materiale di urto alla struttura metallica sottostante; Il materiale dielettrico sottostante e il metallo forniscono uno strato di adesione e fungono da strato barriera per impedire ai contaminanti di migrare al metallo sottostante lungo la direzione orizzontale dello strato dielettrico. La maggior parte degli UBM attualmente utilizzati sono realizzati mediante processi di sputtering. Il processo di sputtering è il più conveniente per fare UBM. Soprattutto rispetto al processo di evaporazione. Il fattore più diretto che influisce sull'affidabilità della struttura dell'urto di saldatura è la qualità di produzione di UBM. In generale, le strutture UBM devono resistere a molteplici riflusso (spesso fino a 20) senza danni. Poiché UBM è una struttura utilizzata per legare insieme urti di saldatura e strati di metallizzazione pad, deve anche superare le prove di sforzo di taglio e di tensione alla trazione. Nella prova di danno meccanico, il criterio generale per l'avaria di urto della saldatura è che il guasto si verifica nella saldatura stessa. Pertanto, UBM deve avere una forza sufficiente. Non ci sarà alcun degrado delle prestazioni a causa di fattori quali tempo, temperatura, umidità e tensione di polarizzazione.

Tendenze del mercato dei chip Flip Il packaging dei chip Flip è diventato la tecnologia di interconnessione degli imballaggi mainstream. Finora, flip chip è considerato un tipo di imballaggio, non una tecnologia di interconnessione. Ad esempio, Flip Chip Ball Grid Array Packaging (FCBGA) utilizza principalmente la tecnologia del substrato stratificato per completare il processo di assemblaggio e confezionamento, ma è limitato alle applicazioni a circuito integrato ad alte prestazioni. La figura seguente mostra le aree di applicazione del flip chip:

(1) passo di bump: riducendo il passo di bump può aumentare la densità I/O; l'andamento del cambiamento di passo (transizione graduale da 250 micron a 125 micron);

(2) metodo di affondamento del bump della saldatura: evaporazione-serigrafia stampa-galvanica;

(3) composizione della saldatura di bump: passo della colonna eutettico-senza piombo ad alto contenuto di piombo (Sn-Ag)-Cu < 125 micron;

(4) Composizione del pacchetto: substrato ceramico-substrato ad alta densità di interconnessione laminato substrato-prepreg laminato substrato-basso coefficiente di espansione termica substrato laminato? Substrato senza anima.

(5) Struttura del pacchetto: copertura a chip singolo sigillato (SPL) - non sigillato copertura a chip singolo + copertura a chip nudo stampato

I mercati di applicazione della FCCSP tradizionale sono i seguenti:

Mercato delle applicazioni FCCSP:

(1) la densità del bump (I/O) relativa alla dimensione del chip: utilizzato per le dimensioni del chip >200 I/O o >5.5mm; I prodotti a bassa densità utilizzano WLCSP per costi sempre migliori.

(2) Bassa potenza: potenza generale<2w dipendente="" on="" chip="" board-level="" packaging="" can="" be="" used="" for="" power="" bare="" fccsp="">2W).

(3) Area: Per i dispositivi palmari, la tecnologia 40nm/65nm riduce la dimensione del chip, ma più I/O fa non c'è abbastanza area per organizzare l'I/O periferico, quindi è necessario utilizzare il cavo del substrato per ventilare fuori l'area.

(4) Prezzo: Per chip di piccole dimensioni ad alto I/O, area periferica insufficiente, costo della linea Au e substrati di grandi dimensioni per fan-out di piombo guideranno lo sviluppo di FCCSP a prezzi competitivi.

(5) stampaggio, facile da testare e tenere, la forma comune è la stessa di CABGA.

Sintesi

Flip chip è sempre stata una tecnologia di imballaggio emozionante. Ma rispetto agli imballaggi tradizionali per l'incollaggio del filo, il suo costo limita il chip flip per diventare la tecnologia mainstream. Tuttavia, i vincoli di costo vengono gradualmente eliminati e l'uso di chip flip-chip confezionati in strisce ne ha notevolmente ridotto i costi. Poiché i substrati laminati rappresentano il maggior costo del prodotto, ridurre il costo dei substrati laminati è il modo più efficace per ridurre il costo degli imballaggi flip-chip.

Inoltre, per la progettazione FPFC, Amkor ha condotto un sacco di ricerche per trasformare il design esistente del flip-chip array di area in un design a passo fine. L'80% degli studi ha scoperto che il design periferico a passo fine può ridurre il costo del substrato, dovuto alla riduzione dello strato metallico e alla riduzione delle dimensioni esterne. Riducendo il costo dei substrati di imballaggio flip-chip (il suo costo è il più alto), è possibile realizzare imballaggi flip-chip ampiamente utilizzati in altri mercati.