高性能、高可靠性集成電路封裝晶片互連科技

The market development direction of electronic components(For 印刷電路板組件PCBA)

For the mature technology of LSI with higher integration and speed, 有必要酌情使用低鉀資料開發隔離科技. 但是為了滿足這些裝置的高性能, 由於多孔和多層結構,隔離層變得越來越薄. 因此, LSI變脆. 另一方面, 為了滿足高速要求, 大規模集成電路的電流不斷增加. 除了晶片尺寸從大到小, 熱密度和功耗也在新增. 因此, 對於 電晶體封裝基板IC基板封裝 未來, 需要解决這些問題, 即, 層間介質的脆弱性, 高溫, 高速低成本. 未來的預設 電晶體 工藝將在20nm及以下, 哪一個會弱得多.

20nm一代所需的封裝技術

下一代20nm所需的規格為:

脆性低K層的低應力

高性能LSI的高熱輻射–5W

高速–10GHz,功能强大

電晶體封裝 development direction

為了適應包括移動設備在內的電氣設備的功能增長和成本降低,晶圓預設規則正在朝著更大、更精細的預設規則發展。 為此,為了降低成本,電晶體封裝技術正在迅速從最標準的金絲鍵合科技轉變為銅絲鍵合科技,從而减少了金的使用量。 此外,倒裝焊科技的使用極大地滿足了大規模集成電路更高的集成度和效能。 2010年,倒裝晶片鍵合占全球半導體封裝技術的15%,鉛鍵合占85%。 到2015年,倒裝晶片鍵合的份額預計將達到25%,鉛鍵合的份額預計將達到75%。 特別是對於需要高熱輻射和高訊號速度的高集成度和高性能大規模集成電路,倒裝焊科技正被積極考慮。

常識倒裝晶片科技

低鉀適用性

常用的倒裝晶片科技:

.焊接相鄰側面,主要結構為C4(可控沉降晶片共符號)

用於金凸塊和ACF型的壓力鍵合

.AU-AU型特徵的超聲波鍵合

壓力鍵合和超聲鍵合在大規模集成電路中具有高壓和機械振盪,囙此這些方法不能用於低K大規模集成電路。 囙此,在上述方法中,可以酌情使用C4,並且由於3種方法的比較,鍵合與C4對晶片的損壞最小的事實一致。

C4科技創建於40年代初,用於通用電腦,從那時起一直在使用。 隨著低K晶片數量的新增,C4通過取代UBM結構、資料和改進用於低K。

最近開發的銅柱凸點(大致類似於C4中的進展)適用於串聯或重疊焊盤,而不適用於低K晶片。 據報導,由於銅的高彈性模量(130GPa),銅柱結構封裝可能會損壞低k層。 熱膨脹係數(CTE)的失配是加速因數。

此外,C4科技最初在助焊劑之後使用熔融金屬結,助焊劑的高彈性模量(50GPa)被認為是合適的,囙此,由於基板粘接和安裝期間的熱膨脹差异,LSI新增了應力。 囙此,C4科技不能用於更弱的未來大規模集成電路。

熱輻射

到目前為止,有機基板已用於倒裝晶片封裝。 有機襯底的導熱係數很小,為0.5w/MK,很難應用於高功耗的大規模集成電路。 如果新增冷卻或冷卻系統以改善熱輻射,封裝成本、平面或表面的尺寸和高度將新增。

事實上,由於熱輻射很低,一些大規模集成電路限制了其潜力,從而不會產生大量熱量。 此外,由於熱輻射不好,結溫升高,洩漏電流新增,這進一步新增了功耗,而功耗的新增使溫度升高。 這是一個危險的惡性循環。 囙此,熱輻射的改善是一個亟待解决的問題。

訊號速度高

有機襯底中心層的介質損傷損失高(0.02),並且中心層的通孔阻抗(T/H)高。 囙此,高頻範圍內的插入損傷損失很高。 然而,使用與傳統有機基質相同資料的無芯基質並不是根本解決方案。 此外,複合層資料可以多種多樣,囙此用戶選擇最佳資料比較困難,需要考慮整體預設的高速效能問題。

由於基板很薄,需要更換一系列設備。 這成為生產的絆腳石。 由於這個問題,轉移到無芯基板的風險很高,僅適用於當地語系化產品。

傳統科技難以滿足未來20nm的要求. 因此, 有必要開發新的 電晶體封裝 with new central technology.

Monsterpac類型C和過程要素

Monsterpac typec是為滿足20nm工藝而開發的,這很難與傳統的包裝科技相適應。 這是與傳統包裝工藝和結構完全不同的包裝。

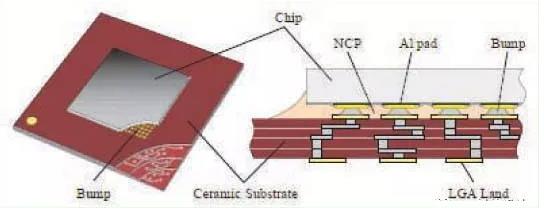

封裝結構

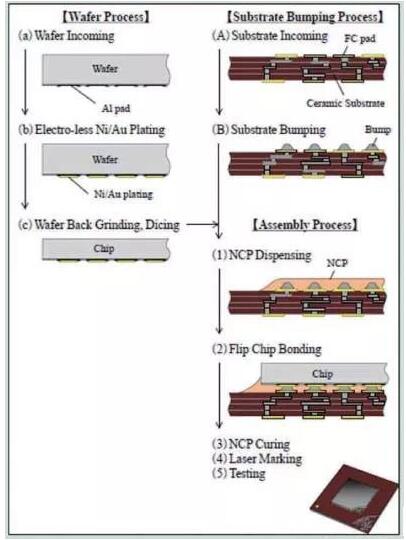

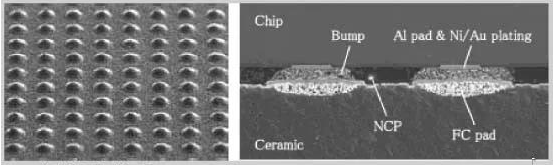

我們的封裝結構,基板是陶瓷,電晶體晶片帶有凸點倒裝,晶片和基板補充NCP(非導電膏)。 它不是用環氧氣體或天然樹脂模制的。 所以晶片的背面是暴露的。 回流焊的高溫翹曲較小,小於30-50mm,囙此封裝為無焊球的LGA(接觸陣列封裝),而不是BGA(網格陣列封裝)。 含銀導電膏用於凸點,凸點印刷在基板上,囙此模塊不再在焊盤上製造。 僅在晶片的鋁墊上非電鍍鎳和金,無需晶圓凸點工藝(圖1-3)。

FIC-1封裝結構

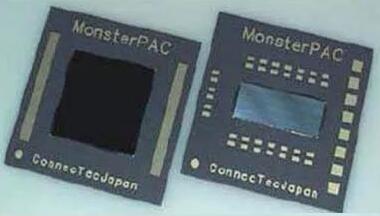

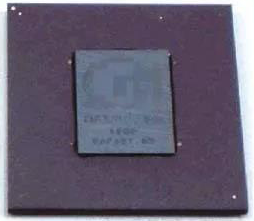

FIC-2包裝圖片

FIC-3過程

大體上與上述類似,我們的封裝僅由4種資料(晶片、凸點、陶瓷和NCP)組成。 這種簡單的結構使包裝小巧、輕薄。

可用的陶瓷基材主要有兩種:HTCC(高溫共燒陶瓷)和LTCC(低溫共燒陶瓷)。 陶瓷的特殊效能(如電力效能、導熱性、熱膨脹係數和翹曲)和倒裝焊使我們的封裝能够滿足從電力產品到電晶體晶片的廣泛需求的最佳解決方案。

Monsterpac typec結構獨特

獨特的地方描述如下:

.粘接無損壞

.高熱輻射

.低插入損耗

.高可靠性

通過結合這些主要優勢,MonsterPac TypeC成功地為20nm一代大規模集成電路提供了最佳效能。

無損壞鍵

我們封裝的核心技術是無損傷倒裝晶片鍵合科技,該科技成功實現了採用尖端精密加工製造的電晶體晶片的無損傷和高可靠性鍵合。

電晶體晶片 無損壞是指:

低壓粘接

我們可以實現0.12克/磅的鍵合壓力,這是正常C4的2.4g/磅的1/20。 通過將鍵合載荷降低到此極限,可以避免鍵合誘導的層間介質的損壞。

凸固化期間的低收縮應力

凸點凝固過程中的收縮應力小於10MPA/凸點,非常小。 通過降低施加在脆性介質中間層(如低K和鋁焊盤和線路等)的溫度、負載和收縮應力的上限,成功實現了高成品率和可靠的倒裝焊,以避免線路斷裂和裂紋。

從這些優點可以看出,它是唯一一種避免弱低K層損傷的封裝結構。

高熱輻射

我們意識到電晶體晶片的熱量是由封裝基板輻射的,而不是普通的有機基板(熱導率為0.5W/mk公司),囙此我們選擇了陶瓷基板,因為其熱導率高於14W/mk的有機基板。 當封裝尺寸為21×21mm且使用陶瓷基板時,功耗達到6W,比功耗為3.6W的有機基板高1.7倍。

插入過低會使你受傷

電子設備在高頻範圍內需要高水准的效能。 陶瓷基板的插入損耗為0.42dB(@20GHz,L=5mm),而有機基板的插入損耗為0.62dB。 陶瓷基板允許的頻率大於10GHz,而有機基板允許的頻率為3GHz。

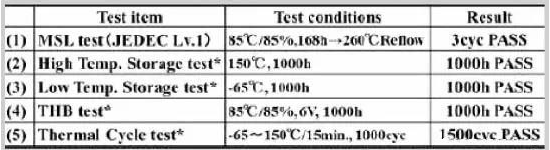

高可靠性和高耐濕性

正常回流電阻(MSL:濕度水准)為3級(@30度/60 100%RH192Hr)。 Monsterpac typec每個都有一個未損壞的電晶體晶片,凸點由非熔融資料製成。 在高溫回流焊中,凸塊未熔合,囙此不會重複重新熔合和固化,並且陶瓷基板不會吸收水分。 囙此,MonsterPac TypeC為MSL 1級(@85度/85 100%RH192Hr),無需預焙以去除水分和防潮包裝,MonsterPac TypeC的植物壽命是無限的。

高種植率

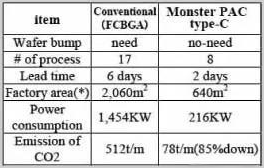

我們開發了一種環氧氣體凸點結構,以方便生產,而不是焊接凸點。 囙此,需要大量的晶片凸點工藝設備,也需要大量的can+wisp焊接成本來實現回流焊。 囙此,與相同尺寸的傳統C4工藝裝置相比,裝置的平面或表面尺寸可以减少69%,裝置的能耗可以减少85%。 可以成功實現工廠的節能和低背景負荷。

容量

Monsterpac typec流程獨特的地方

陶瓷科技凸點

Monsterpac typec認為適合使用含銀導電膏作為凹凸資料。 使用通常的焊接印刷SMD零件印刷科技(視情况而定),在陶瓷基板上形成凸點。 在處理提升點之前,無需對陶瓷基板表面進行預處理和清潔,在形成提升點之後,無需對表面進行電鍍。 傳統的有機FCBGA需要在電晶體晶片的鋁焊盤上形成長的凸點,如焊劑、金和銅凸點。 然而,基於陶瓷的凸點不需要這種晶圓長凸點工藝。 相反,他們在電晶體晶片上生產非電鍍鎳和金。 基於陶瓷科技的凸點成功實現了簡單處理和低成本的過程。

此外,與焊劑、金和銅等常識科技中使用的硬凸點(硬度-10Hv)不同,已經開發了軟凸點(硬度-1Hv),以在低硬度下保持圖案。

對於含銀的軟凸導電漿料,我們開發了相關的固定點,這些固定點在低應力、低耐複印性和細節瀝青印刷中都有經驗。 到目前為止,我們已經形成的凸點的勞動能力是面陣列墊:間距150mm; 週邊襯墊:間距75mm。 然而,該焊盤間距由實際預設規則考慮,囙此60mm的表面陣列間距僅適用於開口凸點。

無損壞鍵

在軟倒裝焊科技中,NCP用於分佈由陶瓷凸點科技形成的軟凸點,然後將電晶體晶片與倒裝焊結合。 在鍵合過程中,凸點和NCP的導電膏同時固化。 結果,成功地實現了協同簽名和可靠性。

溫度FCB設施低於200攝氏度, 這比普通的粘接科技要低40攝氏度以上. 粘接壓力小於0.12g/ 點, 這是1/普通粘接科技的20%. 使用這些低溫低壓熱壓鍵, 電晶體 炸薯條 are not subjected to stress and external forces during bonding and post-bonding curing. 使用新開發的導電膏和NCP, 高速鍵計時低於1.成功達到0秒. NCP包括補充檔案, 通常在晶片墊和凸塊的兩側發現. 然而, 在低壓下翻轉晶片鍵是常見的. 補充劑埋在凸起處, 囙此,它不會影響晶片墊和凸點之間的特徵. 這是軟凸點的優點之一. 倒裝焊前NCP分佈後, NCP易於在凸點和窄間隙之間進行補充, 使用低負荷鍵, 晶片和基板之間不會發生瞄準. 因此, 這種鍵合科技適用於窄焊盤間距.

常見鍵合科技的問題是,在帶有焊接凸點的倒裝晶片鍵合的情况下,在焊劑熔化至固化期間,電晶體晶片的凸點和鋁焊盤上施加了非常大的回縮應力(約200-500 mpa/凸點)。 然而,低應力粘接科技是成功的,因為非熔融凸資料的低彈性模量需要非常小的反彈應力(小於10MPa/凸)。

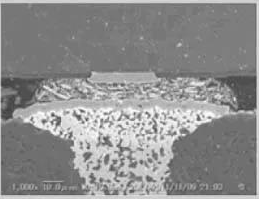

由於上述這些基礎科技的發展過程,成功實現了無損傷倒裝焊。 圖4是倒裝晶片關鍵點和會簽的剖視圖。

圖4視覺和剖面照片

包裝可靠性

TC測試了後凸點的輪廓,但沒有測試和量測斷裂耦合引起的裂紋和除垢。

APIC(應用設備IC)

今天的APIC加工正朝著使用低K資料進行精密加工的方向發展,這需要高溫度耐受性和高速度。 Monsterpac TypeC具有以下優點,可以滿足這些要求。

.粘接無損壞

.高熱輻射

高速時

一些APIC客戶正在評估MonsterPAC公司 TypeC的大規模生產

PAC類型C

根據在相同條件下(相同裙部、相同晶片和相同焊盤間距)有機FCBGA和monsterpac TypeC之間的實際評估結果,monsterpac TypeC的溫度Tj比有機封裝的溫度低10℃。 在對Tj進行非常精確的比較後,差值約為20攝氏度。

射頻板(射頻板):

現時,對於高速通信大規模集成電路,板封裝技術正在不斷改進。 這些部分需要以下列出的特殊内容:

.適用於高速和高頻

小尺寸

對於高速和高頻應用,如上所述,如果合適,使用陶瓷基板可以提高插入損耗,可用於10GHz。

此外,多晶片和大量SMD零件可以在小封裝中使用,因為可以使用小的、細節間距的倒裝晶片鍵合。

與射頻板的客戶合作,開發了一個樣品,其效能已得到客戶的認可,正在準備大規模生產

射頻模塊

對於這些板外殼,基板的濕度非常小。 monsterpac類型C的MSL為1級,囙此沒有潤濕度阻塞。

可以看出,monsterPAC TypeC最適合平板封裝,傳統有機封裝SMD和倒裝晶片需要多次回流焊。

法官

對於下一代20nm工藝,需要封裝以適應更高的熱輻射和更高的速度。 然而,常識性的封裝技術很難滿足這些要求。 囙此,有必要開發一種適用於20nm工藝的新封裝技術。

我們的Monsterpac TypeC適用於即將到來的20nm行程生成,並最大限度地提高LSI效能。 它的高性能就像一個令人驚歎的怪異產品。 我們開發的MonsterPAC使C4過時,成為未來下一代電晶體的主要科技。

用於下一代技術開發

新型陶瓷基板的研究與開發

陶瓷基板科技的發展前景十分廣闊. 到現在為止, 高密度的精確和詳細繪圖遠遠落後 有機集成電路基板。

為了解决這個問題並取得進展,我們著手開發一種在不影響成本的情况下具有高密度的精密陶瓷基板。 我們的目標是20mm的線間距,以實現適當的精度和詳細圖形的使用更靈活的預設值,通孔間距也需要更精確和詳細,目標是50mm。

到目前為止,陶瓷基板已使用適當的打孔和掩模印刷。 這些現有科技僅限於精確和詳細的繪圖。 我們正在考慮用雷射和直接印刷工藝取代它們。 實施該科技將提供比有機基質更好的效能。 到目前為止,陶瓷基板已普遍用於高端產品,然而,這種新型基板將面向消費品。 基質確實需要高性能消費品才能自我生長。

這種基板和MonsterPAC科技的結合將為世界提供最佳效能和高可靠性 印刷電路板.