Auf der Grundlage der jüngsten PCB-Design Trends, Effizienzsteigerung ist zu einem zentralen Ziel geworden, und der Kompromiss von langsamen Schaltgeräten für eine bessere EMI lohnt sich nicht. Super-Verbindungen können die Effizienz in Anwendungen verbessern, in denen planare MOSFETs schwer zu handhaben sind. Im Vergleich zur herkömmlichen planaren MOSFET-Technologie, Super-Junction MOSFET kann den Einschaltwiderstand und die parasitäre Kapazität signifikant reduzieren. Obwohl die signifikante Verringerung des Einschaltwiderstands und die Verringerung der parasitären Kapazität helfen, die Effizienz zu verbessern, it also produces rapid switching of voltage (dv/dt) and current (di/dt), was zu hochfrequentem Rauschen und abgestrahlten EMI führt.

Um schnell schaltende Super-Junction-MOSFETs zu betreiben, ist es notwendig, die Auswirkungen von Paket- und PCB-Design-Layout-Parasiten auf die Schaltleistung zu verstehen, sowie die PCB-Design-Layout-Anpassungen, die zur Verwendung von Super-Junctions vorgenommen werden. Super-Junction MOSFET mit Durchschlagsspannung von 500-600V wird hauptsächlich verwendet. Unter diesen Spannungsklassen sind die Industriestandards TO-220, TO-247, TO-3P und TO-263 die am häufigsten verwendeten Pakete. Der Einfluss von Verpackungen auf die Leistung ist begrenzt, da die internen Gate- und Source-Bonddrahtlängen fest sind. Nur die Länge der Leitung kann geändert werden, um die Quellinduktivität des Gehäuses zu reduzieren.

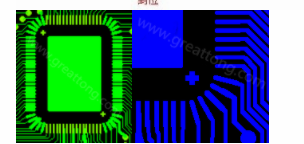

Die typische Bleiinduktivität von 10nH scheint nicht groß zu sein, aber die di/dt dieser MOSFETs können leicht 500A/μs erreichen! Unter der Annahme, dass di/dt 500A/μs ist, ist die Spannung auf der 10nH-Leitungsinduktivität VIND=5V; und die Abschaltung di/dt der 10nH-Leitungsinduktivität beträgt 1.000A/μs, was eine Spannung von VIND=10V erzeugen kann. Die meisten Anwendungen und Designs haben nicht berücksichtigt, dass diese zusätzliche Induktivität auch Spannung erzeugt, aber dies kann nicht ignoriert werden. Die obige einfache Berechnung zeigt, dass die Gesamtquelleninduktivität des Gehäuses, das heißt die Bonddraht- und Pin-Induktivität, auf einen akzeptablen Wert reduziert werden muss. Eine weitere Lärmquelle sind Layoutparasitäre. Es gibt zwei sichtbare Layout-Parasiten: parasitäre Induktivität und parasitäre Kapazität. Die Induktivität einer 1cm Spur beträgt 6-10nH. Diese Induktivität kann durch Hinzufügen einer Schicht auf der Oberseite der Leiterplatte und einer GND-Schicht auf der Unterseite der Leiterplatte reduziert werden. Der andere Typ ist parasitäre Kapazität.

Das Prinzip der kapazitiven Parasiten im Layout. Parasitische Kapazität wird durch zwei benachbarte Leiterbahnen oder zwischen einer Leiterbahn und der Erdungsebene auf der anderen Seite verursacht. Eine andere Art von Kapazität ist die Kapazität zwischen dem Gerät und der Masseebene. Die beiden parallel laufenden Drähte auf beiden Seiten des Leiterplatte Kann Kapazität erhöhen und Schleifeninduktivität reduzieren, Verringerung der elektromagnetischen Lärmstrahlung. Bitte beachten Sie diese Layouttipps, wenn Ihr Design das nächste Mal Super-Junction MOSFETs benötigt.

Parasitische Komponenten in Verpackung und Layout

Da MOSFET ein unipolares Gerät ist, ist die parasitäre Kapazität der einzige begrenzende Faktor für das Schalten von Transienten. Das Prinzip der Ladungsbilanz reduziert den Einschaltwiderstand eines bestimmten Bereichs, und im Vergleich zur Standard-MOSFET-Technologie ist die Chipgröße unter demselben RDS (ON) kleiner. Abbildung 1 zeigt die Kapazität eines Super-Junction-MOSFETs und eines Standard-planaren MOSFETs. Die Coss des Standard-MOSFETs haben eine moderat lineare Beziehung, während die Coss-Kurve des Superjunction-MOSFETs eine hochgradig nichtlineare Beziehung darstellt. Aufgrund der höheren Zelldichte ist der Anfangswert von Coss des Superjunction-MOSFET höher, aber im Superjunction-MOSFET sinkt der Coss schnell in der Nähe der Drain-Source-Spannung von etwa 50V. Wenn Superjunction MOSFETs in PFC- oder DC/DC-Wandlern verwendet werden, können diese nichtlinearen Effekte Spannungs- und Stromschwingungen verursachen. Abbildung 3 zeigt ein vereinfachtes schematisches Diagramm der PFC-Schaltung, einschließlich der internen parasitären Elemente des LeistungsMOSFET und einer externen Oszillatorschaltung. Die externe Oszillatorschaltung enthält einen externen Kopplungskondensator (Cgd_ext.), der vom Layout mitgebracht wird.

Vergleich der Ausgangskapazität zwischen planarem MOSFET und Superjunction MOSFET

Im Allgemeinen, Es gibt mehrere Oszillatorschaltungen, die die Schalteigenschaften des MOSFET beeinflussen, einschließlich interner und externer Oszillatorschaltungen. In der PFC-Schaltung, L, Co und Dboost sind die Induktivität, Ausgangskondensator bzw. Boost-Diode. Cgs, Cgd_int und Cds sind die parasitäre Kapazität des Leistungs-MOSFET. Ld1, Ls1, und Lg1 sind der Abfluss, Quelle, und Gate Bonddrähte und Pin Induktivität des Power MOSFET. Rg_int und Rg_ext sind der interne Gate-Widerstand des Leistungs-MOSFET und der externe Gate-Antriebswiderstand der Schaltung. Cgd_ext ist die parasitäre Gate-Drain-Kapazität der Schaltung. LD, LS, LG und LG sind die streunenden Induktivitäten des Abflusses, Quelle, and gate traces of the printed circuit board (PCB). Wenn der MOSFET ein- oder ausgeschaltet ist, Die Gate-parasitäre Oszillation tritt im Resonanzkreis durch die Gate-Drain-Kapazität Cgd und die Gate-Lead-Induktivität Lg1 auf.

Unter der Resonanzbedingung (ÏL=1/Ï C) ist die im Gate und in der Quellspannung erzeugte oszillierende Spannung viel größer als die Antriebsspannung. Die durch die Resonanzänderung verursachte Spannungsschwingung ist proportional zum Qualitätsfaktor Q (=ÏL/R=1/ÏCR). Wenn der MOSFET ausgeschaltet ist, verursachen die Drain parasitäre Induktivität (LD+Ld1), die Gate-Drain-Kapazität Cgd und das Gate-Lead-Induktivität Lg1-Netzwerk die Gate-Oszillationsspannung. Ist der Gate Widerstand (RG-ext.+Rg_int.) extrem klein, wird Q groß. Darüber hinaus erzeugen der Spannungsabfall über LS und die Quellstreudinduktivität von Ls1 Schwingungen in der Gate-Source-Spannung. Parasitische Schwingungen können Gate-Source-Ausfall, schlechte EMI, große Schaltverluste, Gate-Steuerfehler verursachen und sogar MOSFET-Fehler verursachen.

Es ist sehr wichtig, das Schaltungsdesign zu optimieren, um die Leistung des Super-Junction MOSFET ohne negative Auswirkungen zu maximieren.